**MP2884A** Digital, Multi-Phase PWM Controller with PMBus and PWM-VID

## DESCRIPTION

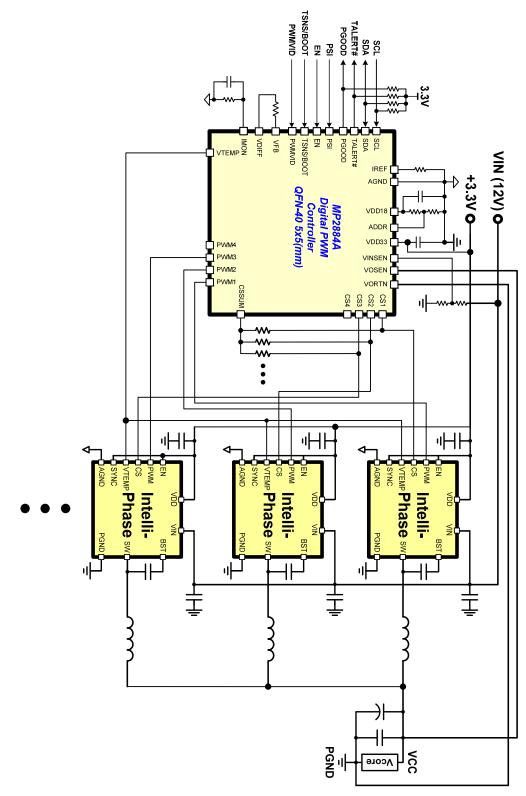

The MP2884A is a digital, multi-phase, pulsewidth modulation (PWM) controller with digital PWM-VID interface compatible with NVIDIA's Open VReg specification. The MP2884A can work with MPS's Intelli-Phase products to complete the multi-phase voltage regulator (VR) solution with minimal external components. The MP2884A can be configured with up to 4-phase operation.

The MP2884A provides an on-chip EEPROM to store and restore device configurations. Device configurations and fault parameters can be easily programmed or monitored via the PMBus/I<sup>2</sup>C interface. The MP2884A can monitor and report the output current through the CS output from the Intelli-Phase products.

The MP2884A is based on a unique, digital, multi-phase, non-linear control and provides fast transient response to the load transient with minimal output capacitors. With only one power-loop control method for both steady state and load transient, the power loop compensation is very easy to configure.

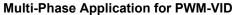

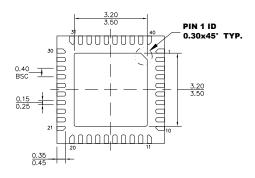

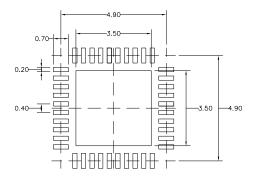

The MP2884A is available in a QFN-40 (5mmx5mm) package.

## FEATURES

- Programmable Multi-Phase up to Four Phases

- PWM-VID Interface Compatible with NVIDIA Open VReg Specification

- PMBus/I<sup>2</sup>C Compliant (1MHz Bus Speed)

- Pin Programmable for PMBus Address

- Built-In EEPROM to Store Custom Configurations

- Switching Frequency Range 200kHz to 5MHz

- Automatic Loop Compensation

- Fewer External Components than Conventional Analog Controller

- Best Transient Performance with Non-Linear Digital Control

- Flexible Phase Assignment

- Auto-Phase Shedding to Improve Overall Efficiency

- Phase-to-Phase Active Current Balancing with Programmable Offsets for Thermal Balance

- Output Voltage/Current, Input Voltage/ Power Monitoring

- Regulator Temperature Monitoring

- VIN UVLO, Output OVP/UVP, OCP, OTP with No Action, Latch, Retry, or Hiccup Mode Options

- Detecting for Intelli-Phase MOSFET Fault Type and Auto-Record to EEPROM

- Register Map Password Lock

- Digital Load-Line Regulation

- Available in an RoHS Compliant QFN-40 (5mmx5mm) Package

## **APPLICATIONS**

- Graphic Card Core Power

- Server Core Power

- Telecom and Networking Systems

- Base Stations

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

## **TYPICAL APPLICATION**

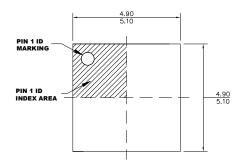

#### **ORDERING INFORMATION**

| Part Number*     | Package          | Top Marking |

|------------------|------------------|-------------|

| MP2884AGU-xxxx** | QFN-40 (5mmx5mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g.: MP2884AGU-xxxx–Z).

\*\* "xxxx" is the configuration code identifier for the register settings stored in the EEPROM. Each "x" can be a hexadecimal value between 0 and F. Please work with an MPS FAE to create this unique number.

## **TOP MARKING**

MPSYYWW MP2884A

LLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP2884A: Part number LLLLLLL: Lot number

#### PACKAGE REFERENCE

www.MonolithicPower.com

## **PIN FUNCTIONS**

| Package<br>Pin # | Name    | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                    |

|------------------|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | TALERT# | D [O]               | <b>Open-drain VR thermal indicator.</b> TALERT# is pulled low if the temperature exceeds the programmed threshold from either VTEMP or TSNS.                                                                                                                   |

| 2                | T1      | D [O]               | Test pin 1. Leave T1 floating.                                                                                                                                                                                                                                 |

| 3                | T2      | D [O]               | Test pin 2. Leave T2 floating.                                                                                                                                                                                                                                 |

| 4                | Т3      | D [O]               | Test pin 3. Leave T3 floating.                                                                                                                                                                                                                                 |

| 5 - 7            | NC      | D [O]               | No connection. Leave NC floating.                                                                                                                                                                                                                              |

| 8                | PWM4    | D [O]               | Tri state logic lovel DMM outputs. Each output is connected to the                                                                                                                                                                                             |

| 9                | PWM3    | D [O]               | <b>Tri-state logic-level PWM outputs.</b> Each output is connected to the PWM input of the Intelli-Phase. The low logic level is 0V. The high logic                                                                                                            |

| 10               | PWM2    | D [O]               | level is 3.3V. The mid-state logic level is 1.5V (or high impedance). Float                                                                                                                                                                                    |

| 11               | PWM1    | D [O]               | PWMx if it is not being used.                                                                                                                                                                                                                                  |

| 12               | VDD33   | Power               | <b>3.3V power supply input.</b> Connect a 1µF bypass capacitor from VDD33 to AGND.                                                                                                                                                                             |

| 13 - 16          | NC      | A [I]               | No connection. Leave NC floating.                                                                                                                                                                                                                              |

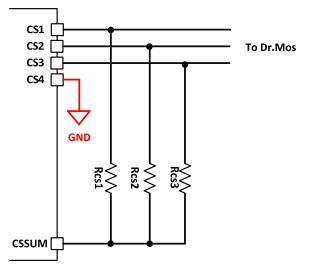

| 17               | CS4     | A [I]               |                                                                                                                                                                                                                                                                |

| 18               | CS3     | A [I]               | Phase 1~4 current sense input. Short CSx to AGND or CSSUM if it is                                                                                                                                                                                             |

| 19               | CS2     | A [I]               | not being used.                                                                                                                                                                                                                                                |

| 20               | CS1     | A [I]               |                                                                                                                                                                                                                                                                |

| 21               | CSSUM   | A [I]               | <b>Total phase current sensing input.</b> CSSUM is used for load-line and over-current protections. Connect the active phases' CS signals together to CSSUM through the current-sense resistors.                                                               |

| 22               | VINSEN  | A [I]               | <b>Input voltage sensing.</b> Place a resistor divider from the power stage $(V_{IN})$ to VINSEN.                                                                                                                                                              |

| 23               | VDD18   | Power               | <b>1.8V LDO output.</b> VDD18 provides a power supply for the internal digital circuit. Connect a 1µF bypass capacitor from VDD18 to AGND.                                                                                                                     |

| 24               | ADDR    | A [I]               | PMBus address setting.                                                                                                                                                                                                                                         |

| 25               | IMON    | A [I/O]             | Analog total average current sensing signal. IMON sources a current proportional to the sensed total average current from CSSUM. IMON is used for load-current reporting.                                                                                      |

| 26               | IREF    | A [I/O]             | Internal bias current set. Connect a 61.9k $\Omega$ , 1% accuracy resistor from IREF to AGND.                                                                                                                                                                  |

| 27               | T4      | A [I]               | Test pin 4. Short T4 to AGND.                                                                                                                                                                                                                                  |

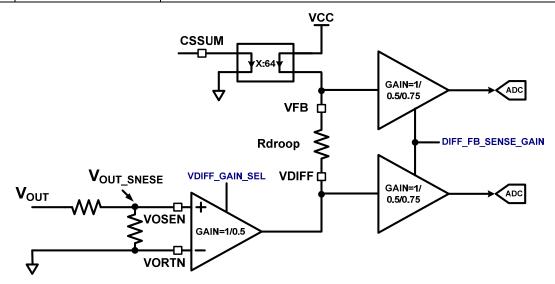

| 28               | VDIFF   | A [O]               | Output of the differential remote sense amplifier.                                                                                                                                                                                                             |

| 29               | VFB     | A [I/O]             | <b>Feedback.</b> VFB sources a current (Idroop) proportional to the sensed output current. This current flows through the resistor (Rdroop) between VFB and VDIFF to create a voltage drop proportional to the load current to achieve the load-line function. |

| 30               | T5      | A [I]               | Test pin 5. Short T5 to AGND.                                                                                                                                                                                                                                  |

| 31               | VOSEN   | A [I]               | <b>Remote voltage sensing positive input.</b> VOSEN is connected to the VR output voltage directly at the load. Route VOSEN with VORTN differentially.                                                                                                         |

| 32               | VORTN   | A [I]               | <b>Remote voltage sensing return input.</b> VORTN is connected to the ground directly at the load. Route VORTN with VOSEN differentially.                                                                                                                      |

## **PIN FUNCTIONS** (continued)

| Package<br>Pin # | Name      | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                                                                                                      |

|------------------|-----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |           |                     | <b>Thermistor thermal sensing input or boot voltage setting.</b><br>TSNS/BOOT can be programmed for either thermistor thermal sensing<br>or boot voltage setting.                                                                                                                                                |

| 33               | TSNS/BOOT | A [I/O]             | When used as TSNS, the controller compares the voltage of TSNS/BOOT to an internal programmable threshold. Once triggered, TALERT# is asserted, and the VR enters a pre-programmed protection mode.                                                                                                              |

|                  |           |                     | When used as BOOT, a voltage divider is required from VDD18 to TSNS/BOOT to set the boot voltage.                                                                                                                                                                                                                |

| 34               | SDA       | D [I/O]             | PMBus data.                                                                                                                                                                                                                                                                                                      |

| 35               | SCL       | D [I]               | PMBus clock.                                                                                                                                                                                                                                                                                                     |

| 36               | EN        | D [I]               | Enable control.                                                                                                                                                                                                                                                                                                  |

| 37               | PSI       | A [I]               | <b>Power saving interface.</b> 1.8V logic. When PSI is 1, all phases have forced continuous conduction mode (CCM). When PSI is 0, there is an adjustable low-phase count. When PSI is in Hi-Z, auto-phase-shedding is enabled.                                                                                   |

| 38               | PGOOD     | D [O]               | <b>Power good indication.</b> PGOOD is an open-drain output. PGOOD asserts when the output voltage is in regulation.                                                                                                                                                                                             |

| 39               | PWMVID    | A [I]               | <b>PWM-VID signal input.</b> PWMVID is a 1.8V logic. Connect the PWM-VID signal to PWMVID. The VR calculates the target VID based on the duty.                                                                                                                                                                   |

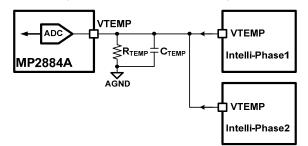

| 40               | VTEMP     | A [I]               | <b>Analog signal from the VR to the controller.</b> VTEMP indicates the maximum temperature of the power stages. The MP2884A supports temperature sensing from the Intelli-Phase power stages. Tie all temperature reporting pins from the Intelli-Phase together to produce the maximum value on the VTEMP bus. |

| PAD              | AGND      | Power               | Analog ground.                                                                                                                                                                                                                                                                                                   |

NOTE:

1) A = analog, D = digital, I = input, O = output, I/O = bidirectional.

#### **ABSOLUTE MAXIMUM RATINGS**<sup>(2)</sup>

| VDD330.3V to +4.0V<br>VDD180.3V to +2.0V    |

|---------------------------------------------|

| CS1~4, PWM1~4, VFB, VDIFF, VOSEN,           |

| VORTN, PGOOD, PSI, SCL, SDA,                |

| TSNS/BOOT, TALERT#, PWMVID, EN,             |

| VTEMP0.3V to +4.0V                          |

| CSSUM, IMON, IREF, VINSEN, ADDR             |

| -0.3V to +2.0V                              |

| Junction temperature 150°C                  |

| Lead temperature                            |

| Continuous power dissipation <sup>(3)</sup> |

#### Recommended Operating Conditions (4)

Supply voltage (V<sub>IN</sub>) ......+3.0V to 3.6V Operating junction temp. (T<sub>J</sub>)....-40°C to +125°C

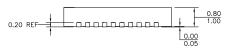

## Thermal Resistance <sup>(5)</sup> $\theta_{JA}$ $\theta_{JC}$

QFN-40 (5mmx5mm)...... 36 ...... 5 .... °C/W

#### NOTES:

- 2) Exceeding these ratings may damage the device.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature.

- 4) The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on JESD51-7, 6-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

VDD33 = 3.3V, EN = 1V, current going into the pin is positive. Typical values are at  $T_A = 25^{\circ}C$ .

| Parameter                                         | Symbol               | Condition                                                                            | Min  | Тур            | Max | Units |

|---------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|------|----------------|-----|-------|

| Remote Sense Amplifier                            |                      | •                                                                                    |      |                |     |       |

| Bandwidth (6)                                     | GBW <sub>(RSA)</sub> |                                                                                      |      | 20             |     | MHz   |

| VORTN current                                     | IVORTN               | EN = 1V, VOSEN = 3V,<br>VORTN = 0V                                                   |      | -38            |     | μA    |

| VOSEN current                                     | IVOSEN               | EN = 1V, VOSEN = 3V,<br>VORTN = 0V                                                   |      | 38             |     | μA    |

| Oscillator                                        | 1                    | •                                                                                    |      |                |     |       |

| Frequency                                         | f <sub>osc</sub>     | V <sub>IREF</sub> = 1.23V, R <sub>IREF</sub> = 61.9kΩ                                |      | 1.56           |     | MHz   |

| System Interface Control In                       |                      |                                                                                      |      |                |     |       |

| Enable (EN)                                       | -                    |                                                                                      |      |                |     |       |

| Input low voltage                                 | V <sub>IL(EN)</sub>  |                                                                                      |      |                | 0.4 | V     |

| Input high voltage                                | VIH(EN)              |                                                                                      | 0.8  |                |     | V     |

| Enable high leakage                               | I <sub>IH(EN)</sub>  | EN = 2V                                                                              |      |                | 2.3 | μA    |

| IMON Output                                       | ·                    | •                                                                                    |      |                |     |       |

| Current gain                                      | Imon/Ics_sum         | Measured from I <sub>CSSUM</sub> to I <sub>MON</sub> ,<br>I <sub>CS_SUM</sub> = -2mA |      | 1:16           |     | μΑ/μΑ |

| Current gain accuracy                             |                      |                                                                                      | -1   |                | 1   | %     |

| PWM-VID                                           |                      |                                                                                      |      |                |     |       |

| Input low voltage                                 | PWM <sub>VIDL</sub>  |                                                                                      |      |                | 0.4 | V     |

| Input mid-state                                   | PWM <sub>HIZ</sub>   |                                                                                      |      | 0.9            |     | V     |

| Input high voltage                                | <b>PWM</b> VIDH      |                                                                                      | 1.4  |                |     | V     |

| PSI                                               |                      |                                                                                      |      |                |     |       |

| Input low voltage                                 | PSI∟                 |                                                                                      |      |                | 0.4 | V     |

| Input mid-state                                   | PSIM                 |                                                                                      |      | 0.9            |     | V     |

| Input high voltage                                | PSIH                 |                                                                                      | 1.4  |                |     | V     |

| PWM Outputs                                       |                      |                                                                                      |      |                |     |       |

| Output low voltage                                | Vol (PWM)            | $I_{PWM(SINK)} = 400 \mu A$                                                          |      | 10             | 200 | mV    |

| Output middle voltage                             | Vom (pwm)            | $I_{PWM(SOURCE)} = -100 \mu A$                                                       |      | 1.36           |     | V     |

| Output high voltage                               | Voh (pwm)            | $I_{PWM(SOURCE)} = -400 \mu A$                                                       | 3.15 | VDD33<br>-0.02 |     | V     |

| Rise and fall time (6)                            |                      | C = 10pF                                                                             |      | 10             |     | ns    |

| PWM tri-state leakage                             |                      | PWM = 1.5V, EN = 0V                                                                  | -1   |                | 1   | μA    |

| PWM fault detection source current <sup>(6)</sup> | Isource(PWM)         | Enter PWM fault detect mode                                                          |      | 150            |     | μA    |

| TSNS                                              |                      |                                                                                      |      |                |     |       |

| Current source                                    | ITSNS                |                                                                                      |      | 10             |     | μA    |

## ELECTRICAL CHARACTERISTICS (continued)

VDD33 = 3.3V, EN = 1V, current going into the pin is positive. Typical values are at  $T_A = 25^{\circ}C$ .

| Parameter                      | Symbol                | Condition                                                    | Min   | Тур  | Мах   | Units |

|--------------------------------|-----------------------|--------------------------------------------------------------|-------|------|-------|-------|

| Comparator (Protection)        |                       |                                                              |       |      |       |       |

|                                |                       | Relative to reference DAC<br>voltage (2Ch bit[2:0] = 3b'001) |       | -190 |       | mV    |

| Under-voltage threshold        |                       | Relative to reference DAC<br>voltage (2Ch bit[2:0] = 3b'010) |       | -310 |       | mV    |

|                                |                       | Relative to reference DAC<br>voltage (2Ch bit[2:0] = 3b'100) |       | -430 |       | mV    |

|                                |                       | Relative to reference DAC<br>voltage (2Ch bit[2:0] = 3b'001) |       | 190  |       | mV    |

| Over-voltage threshold         |                       | Relative to reference DAC<br>voltage (2Ch bit[2:0] = 3b'010) |       | 310  |       | mV    |

|                                |                       | Relative to reference DAC<br>voltage (2Ch bit[2:0] = 3b'100) |       | 430  |       | mV    |

| VDD33 Supply                   | -                     |                                                              |       | -    | -     | -     |

| Supply voltage range           | VDD33                 |                                                              | 3.0   | 3.3  | 3.6   | V     |

| Supply current                 | Ivdd33                | EN = high or programmed as<br>non-low-power mode             |       | 30   |       | mA    |

|                                | 10033                 | EN = 0 and programmed as<br>low-power mode                   |       | 150  |       | μA    |

| UVLO threshold voltage         | VDD33 <sub>UVLO</sub> | VDD33 is rising                                              |       | 2.88 | 2.98  | V     |

|                                | VDD33 <sub>UVLO</sub> | VDD33 is falling                                             | 2.68  | 2.80 |       | V     |

| 1.8V Regulator                 | I                     |                                                              |       | I    | I     | I     |

| 1.8V regulator output voltage  | VDD18                 | I <sub>VDD18</sub> = 0mA                                     |       | 1.8  |       | V     |

| 1.8v regulator load capability | IVDD18                | VOL = VDD18 - 40mV                                           |       | 30   |       | mA    |

| ADC                            |                       |                                                              |       |      |       |       |

| ADC voltage reference          |                       |                                                              | 1.592 | 1.6  | 1.608 | V     |

| ADC resolution (6)             |                       |                                                              |       | 10   |       | bits  |

| DNL <sup>(6)</sup>             |                       |                                                              |       |      | 1     | LSB   |

| Sample rate (6)                |                       |                                                              |       | 700  |       | kHz   |

| DAC (Reference Voltage)        |                       |                                                              |       |      | 1     |       |

| DAC voltage reference          | FSADC                 |                                                              |       | 1.7  |       | V     |

| Resolution/LSB                 | Δadc                  |                                                              |       | 6.25 |       | mV    |

| Max output voltage slew rate   |                       |                                                              |       | 50   |       | mV/µs |

| OC_DAC (Protection)            | ·                     |                                                              |       |      | ·     | •     |

| Range (6)                      | FSDAC_PRT             | Adjustable via the PMBus                                     | 0.17  |      | 2.72  | V     |

| Resolution/LSB (6)             | $\Delta_{DAC\_PRT}$   |                                                              |       | 10   |       | mV    |

## ELECTRICAL CHARACTERISTICS (continued)

#### VDD33 = 3.3V, EN = 1V, current going into the pin is positive. Typical values are at $T_A = 25^{\circ}C$ .

| Parameter                                | Symbol                 | Condition                        | Min  | Тур | Мах  | Units |

|------------------------------------------|------------------------|----------------------------------|------|-----|------|-------|

| PMBus DC Characteristics (               | SDA, SCL)              |                                  |      |     |      |       |

| Input high voltage                       | VIH                    |                                  | 1.35 |     |      | V     |

| Input low voltage                        | VIL                    |                                  |      |     | 0.8  | V     |

| Input leakage current                    |                        |                                  | -10  |     | 10   | μA    |

| Pin capacitance (6)                      | CPIN                   |                                  |      |     | 10   | pF    |

| PMBus Timing Characteristi               | cs (1MHz) <sup>(</sup> | 7)                               |      |     | •    |       |

| Operating frequency range                |                        |                                  | 10   |     | 1000 | kHz   |

| Bus free time                            |                        | Between stop and start condition | 0.5  |     |      | μs    |

| Holding time                             |                        |                                  | 0.26 |     |      | μs    |

| Repeated start condition set-<br>up time |                        |                                  | 0.26 |     |      | μs    |

| Stop condition set-up time               |                        |                                  | 0.26 |     |      | μs    |

| Data hold time                           |                        |                                  | 0    |     |      | ns    |

| Data set-up time                         |                        |                                  | 50   |     |      | ns    |

| Clock low time-out                       |                        |                                  | 25   |     | 35   | ms    |

| Clock low period                         |                        |                                  | 0.5  |     |      | μs    |

| Clock high period                        |                        |                                  | 0.26 |     | 50   | μs    |

| Clock/data fall time                     |                        |                                  |      |     | 120  | ns    |

| Clock/data rise time                     |                        |                                  |      |     | 120  | ns    |

NOTE:

6) 7)

Guaranteed by design or characterization data, not tested in production. The device supports 100kHz, 400kHz, and 1MHz bus speeds. The PMBus timing parameters in this table is for operation at 1MHz. If the PMBus operating frequency is 100kHz or 400kHz, refer to the SMBus specification for timing parameters.

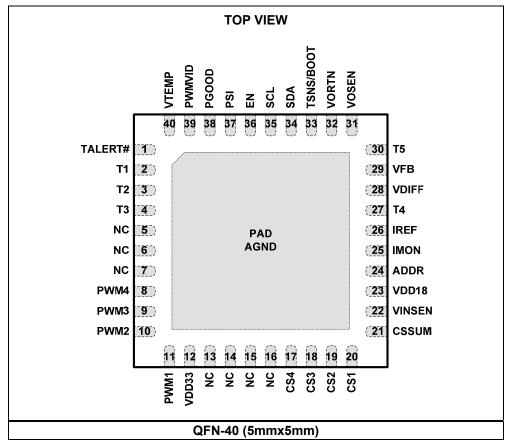

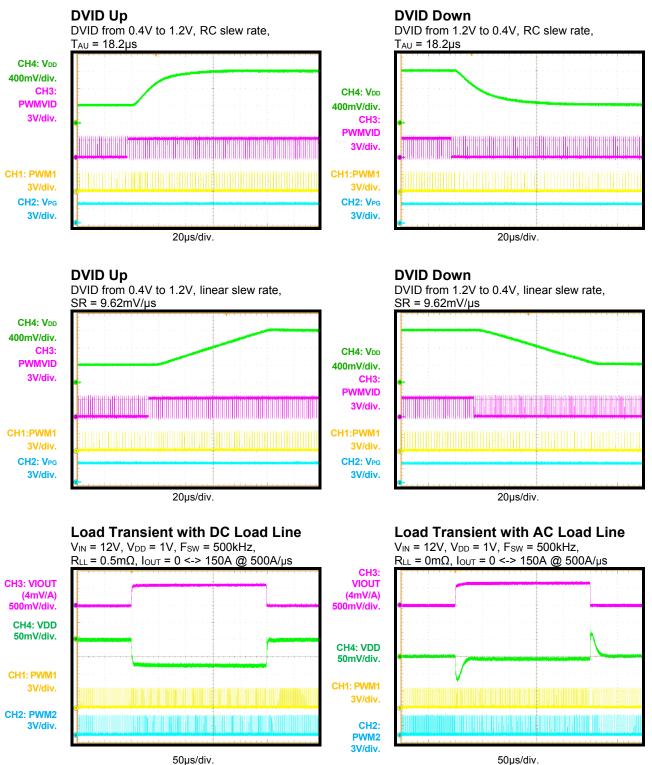

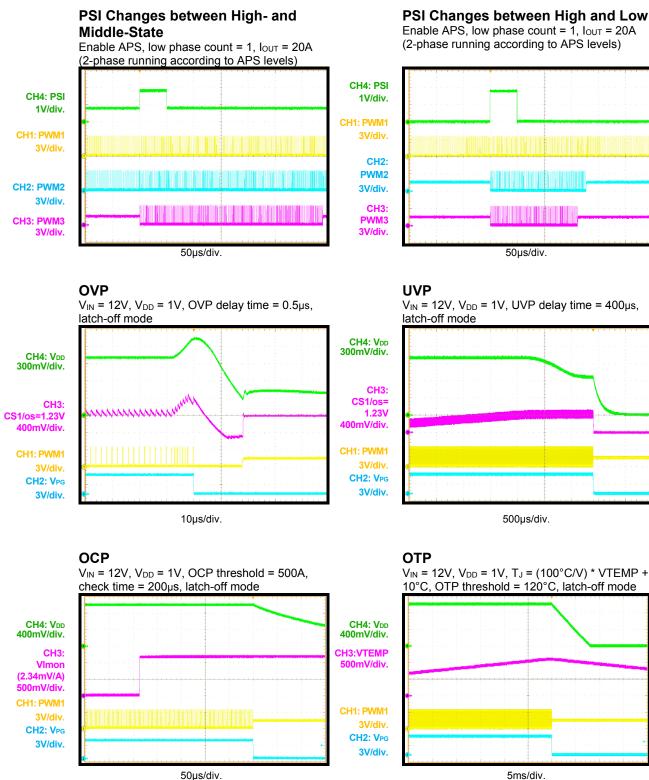

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 12V,  $C_{OUT}$  = 6400µF,  $R_{IMON}$  = 4.42k $\Omega$ , PGOOD is pulled up to +3.3V.  $T_A$  = +25°C, unless otherwise noted.

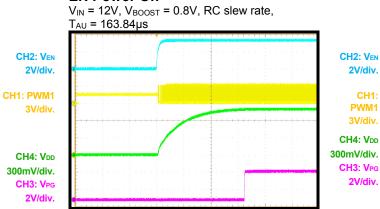

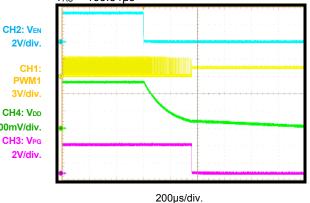

#### **EN Power On**

200µs/div.

**Steady State** V<sub>IN</sub> = 12V, V<sub>DD</sub> = 0.8V, F<sub>SW</sub> = 500kHz, 4-phase CCM, Iout = 60A CH4: VDD/AC 10mV/div. CH1: PWM1 3V/div. CH2. PWM2 3V/div. CH3: PWM3 3V/div

500ns/div.

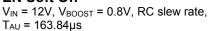

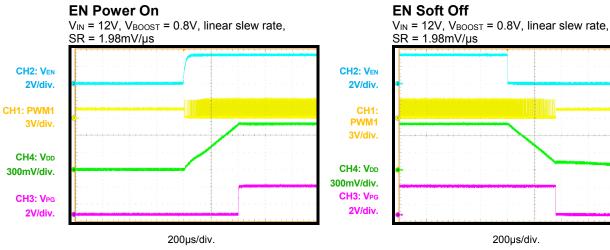

#### **EN Soft Off**

200µs/div.

MP2884A Rev. 1.01 12/25/2018

www.MonolithicPower.com

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{\text{IN}}$  = 12V,  $C_{\text{OUT}}$  = 6400µF,  $R_{\text{IMON}}$  = 4.42k $\Omega$ , PGOOD is pulled up to +3.3V.  $T_{\text{A}}$  = +25°C, unless otherwise noted.

www.MonolithicPower.com

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $C_{OUT}$  = 6400µF,  $R_{IMON}$  = 4.42k $\Omega$ , PGOOD is pulled up to +3.3V.  $T_A$  = +25°C, unless otherwise noted.

www.MonolithicPower.com

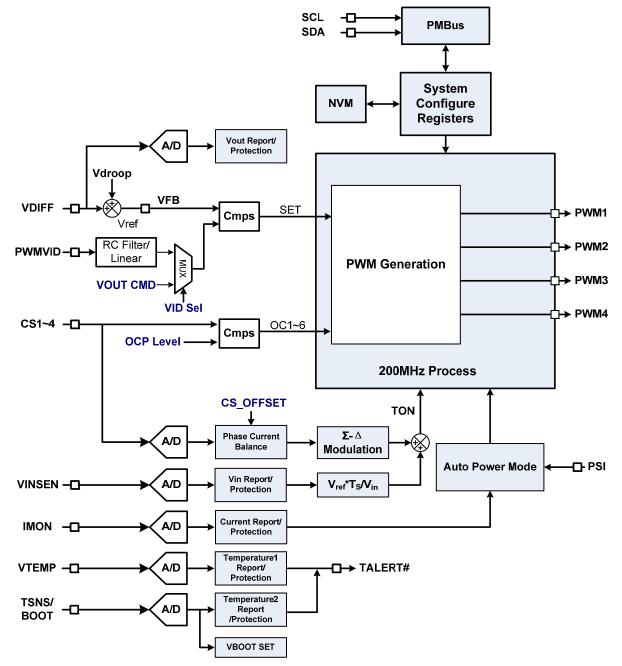

## **BLOCK DIAGRAM**

Figure 1: System Functional Block

## **OPERATION**

The MP2884A is a single-output, digital, multiphase voltage regulator (VR) controller for highperformance GPU or CPU. It supports PWM-VID's controllable V<sub>OUT</sub> reference and is NVIDIA's compliant with Open VReg specification.

The MP2884A uses MPS's unique loop compensation strategy to balance and optimize steady and transient performance. It also adopts adaptive phase-shedding and phaseadding strategies to optimize the overall VR efficiency according to the load current.

The MP2884A contains precision DAC and ADC, differential remote voltage sense amplifier, fast comparators, current-sense amplifiers, internal slope compensation, digital load-line setting, power good monitor, and temperature monitor.

The MP2884A provides rich programmable functions with the PMBus 1.3 interface. On-chip EEPROM is flexible for storing custom configurations and auto-records the fault type when a protection occurs.

Fault protection features include VIN undervoltage lockout (UVLO), VIN over-voltage protection (OVP), V<sub>OUT</sub> OVP, V<sub>OUT</sub> undervoltage protection (UVP), V<sub>OUT</sub> reverse-voltage protection (RVP), output over-current protection (OCP), and over-temperature protection (OTP).

PMBus-programmable functions include phase assignment, switching frequency, reference voltage, loop stability parameters, protection thresholds and behaviors, load-line parameters, and so on.

The MP2884A can also detect the fault type of the Intelli-Phase when a protection occurs. The MP2884A can record all faults into the EEPROM automatically in case the power supply shuts off while the fault is occurring.

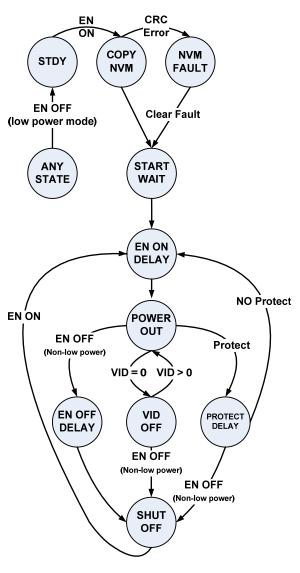

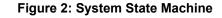

The MP2884A system state machine is shown in Figure 2.

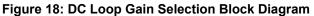

#### PWM Control and Switching Frequency

The MP2884A applies MPS's unique digital pulse-width modulation (PWM) control to provide fast load transient response and easy loop compensation. The switching frequency can be set with the PMBus command MFR FS (BDh).

The PWM on time of each phase updates in real time according to the input voltage, output voltage, and the phase switching frequency adaptively. T<sub>ON</sub> can be calculated with Equation (1):

$$T_{on} = \frac{V_{OUT}}{V_{IN}} \times \frac{1}{F_{s}}$$

(1)

www.MonolithicPower.com

Where  $V_{OUT}$  is the real-time output voltage reference,  $V_{IN}$  is the input voltage, and  $F_S$  is the switching frequency set by the PMBus.

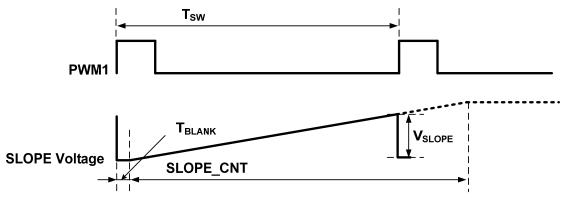

#### Voltage Reference

The MP2884A has an 8-bit VID-DAC, which provides the reference voltage ( $V_{REF}$ ) for the individual output.  $V_{REF}$  is in a VID format with 6.25mV per step. The relationship between  $V_{REF}$  and the VID value in decimals is shown in Equation (2):

$$V_{REF}(V) = VID \times 0.000625$$

(2)

When setting the unit gain for the differential voltage sense amplifier and VID is higher than 256,  $V_{REF}$  is limited to 1.6V.

When setting the half gain for the differential voltage sense amplifier,  $V_{\text{REF}}$  can range from 0 ~ 3.19375V.

#### **Output Voltage Setting and Sensing**

In PMBus-VID control mode, the desired output voltage can be set by the PMBus command VOUT\_COMMAND (21h). VOUT\_COMMAND (21h) is a 9-bit register in a VID format with 6.25mV per step. The output setting range is 0  $\sim$  3.19375V.

In PWM-VID control mode, the desired output voltage can be set according to Equation (3):

$$VID = (VID_{MAX} - VID_{MIN}) \times D_{PWMVID} + VID_{MIN} (3)$$

Where  $VID_{MAX}$  is the maximum voltage setting,  $VID_{MIN}$  is the minimum voltage setting, and  $D_{PWMVID}$  is the duty of the PWM-VID signal.

The voltage at the load is sensed with the differential voltage sense amplifier. This type of sensing provides better load regulation.

The MP2884A provides high-resolution trimming and digital DC calibration for high output voltage regulation accuracy. With a unit gain of the differential voltage amplifier, the  $V_{OUT}$  regulation accuracy is within ±1.5625mV. With a half-gain of the differential voltage amplifier, the  $V_{OUT}$  regulation accuracy is within ±3.125mV.

#### Active Voltage Positioning (AVP)

The MP2884A supports active voltage positioning (AVP) by connecting a droop resistor ( $R_{DROOP}$ ) between VDIFF and VFB. With this function, the output voltage drops gradually as the load current increases. This is also known as load-line regulation. The relationship of the output voltage and load current is shown in Equation (4):

$$V_{\text{OUT}@\text{IOUT}} = V_{\text{OUT}@\text{NO LOAD}} - I_{\text{OUT}} \times R_{\text{LL}} \quad (4)$$

Where  $R_{LL}$  is the equivalent load-line resistor.

The MP2884A provides a PMBusprogrammable load line. The final load-line value is determined by  $R_{DROOP}$  and the value in the register IDROOP\_SET (1Eh). The load-line calculation is shown in Equation (5):

$$R_{LL} = \left(\frac{IDROOP\_SET + 4}{64}\right) \times K_{CS} \times R_{DROOP}$$

(5)

Where IDROOP\_SET is the value in register MFR\_IDROOP\_CTRL (1Eh), and  $K_{CS}$  is the current sense gain of the power stage.

IDROOP\_SET ranges from  $1 \sim 15$ . When setting IDROOP\_SET = 0, the AVP function is disabled.

When setting a half-gain for the differential voltage sense amplifier, the  $R_{LL}$  value in Equation (5) should be doubled.

For non-AVP VR applications, it is recommended to enable the AC droop function via register AC\_DROOP\_EN (1Eh) to increase the phase margin of the loop regulation. The AC droop function can inject the AC current of the total inductor current to  $R_{DROOP}$  to introduce the current ripple signal to the loop regulation.

#### **Boot Voltage Setting**

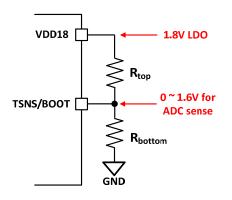

In PMBus-VID control mode, the MP2884A can pre-program the boot voltage ( $V_{BOOT}$ ) either by register VOUT\_COMMAND (21h) or by TSNS/BOOT. Figure 3 shows the connection for the pin-programmed  $V_{BOOT}$ .

#### Figure 3: Circuit of Pin-Strap Boot Voltage

Table 1a and Table 1B show four options for the TSNS/BOOT pin-programmed  $V_{\text{BOOT}}$ .

| TSNS/BOOT<br>Voltage Point<br>(V) | (0.1V/step) | Boot Voltage (V)<br>(0.2V/step)<br>45h bit[1:0] = 10 |

|-----------------------------------|-------------|------------------------------------------------------|

| 0.05                              | 0           | 0                                                    |

| 0.15                              | 0.1         | 0.2                                                  |

| 0.25                              | 0.2         | 0.4                                                  |

| 0.35                              | 0.3         | 0.6                                                  |

| 0.45                              | 0.4         | 0.8                                                  |

| 0.55                              | 0.5         | 1                                                    |

| 0.65                              | 0.6         | 1.2                                                  |

| 0.75                              | 0.7         | 1.4                                                  |

| 0.85                              | 0.8         | 1.6                                                  |

| 0.95                              | 0.9         | 1.8                                                  |

| 1.05                              | 1           | 2                                                    |

| 1.15                              | 1.1         | 2.2                                                  |

| 1.25                              | 1.2         | 2.4                                                  |

| 1.35                              | 1.3         | 2.6                                                  |

| 1.45                              | 1.4         | 2.8                                                  |

| 1.55                              | 1.5         | 3                                                    |

Table 1: Pin-Strap Boot Voltage Table 1

The boot-up linear slew rate is set via register MFR\_BOOT\_SR (B9h) and ranges from 0.12 -  $125mV/\mu s$ , as shown in Equation (6):

SlewRate =

$$\frac{6.25 \text{mV}}{\text{MFR BOOT SR} \times 0.05 \mu \text{s}}$$

(6)

In PWM-VID control mode,  $V_{BOOT}$  can only be set by the register MFR\_VBOOT (BBh). When PWM-VID is in mid-state, the VR output slews to the boot voltage.

There are two boot-up slewing modes for PWM-VID control mode: R-C filter mode and linear mode.

| TSNS/BOOT     | Boot Voltage (V)  | Boot Voltage (V)  |

|---------------|-------------------|-------------------|

| Voltage Point | (0.05V/step)      | (0.1V/step)       |

| (V)           | 45h bit[1:0] = 01 | 45h bit[1:0] = 11 |

| 0.025         | 0                 | 0                 |

| 0.075         | 0.05              | 0.1               |

| 0.125         | 0.1               | 0.2               |

| 0.175         | 0.15              | 0.3               |

| 0.225         | 0.2               | 0.4               |

| 0.275         | 0.25              | 0.5               |

| 0.325         | 0.3               | 0.6               |

| 0.375         | 0.35              | 0.7               |

| 0.425         | 0.4               | 0.8               |

| 0.475         | 0.45              | 0.9               |

| 0.525         | 0.5               | 1                 |

| 0.575         | 0.55              | 1.1               |

| 0.625         | 0.6               | 1.2               |

| 0.675         | 0.65              | 1.3               |

| 0.725         | 0.7               | 1.4               |

| 0.775         | 0.75              | 1.5               |

| 0.825         | 0.8               | 1.6               |

| 0.875         | 0.85              | 1.7               |

| 0.925         | 0.9               | 1.8               |

| 0.975         | 0.95              | 1.9               |

| 1.025         | 1                 | 2                 |

| 1.075         | 1.05              | 2.1               |

| 1.125         | 1.1               | 2.2               |

| 1.175         | 1.15              | 2.3               |

| 1.225         | 1.2               | 2.4               |

| 1.275         | 1.25              | 2.5               |

| 1.325         | 1.3               | 2.6               |

| 1.375         | 1.35              | 2.7               |

| 1.425         | 1.4               | 2.8               |

| 1.475         | 1.45              | 2.9               |

| 1.525         | 1.5               | 3                 |

| 1.575         | 1.55              | 3.1               |

Table 1b: Pin-Strap Boot Voltage Table 2

The boot-up R-C filter time constant is set with register MFR\_PARM\_RC\_CONST (B5h) and ranges from 10.40 -  $655.36\mu$ s, as shown in Equation (7):

$$\tau_{\text{RC}}(\mu s) = \frac{0.32\mu s}{\text{BOOT}_{\text{RC}}} \times 2^{11}$$

(7)

Where BOOT\_RC is the value in register MFR\_PARM\_RC\_CONST (B5h).

The boot-up linear slew rate is set with register MFR\_BOOT\_SR (B9h) and ranges from 0.12 -  $125mV/\mu s$  (see Equation (6)).

#### **Dynamic Voltage Identification (DVID)**

The MP2884A supports dynamical output voltage transition by changing VID via the PMBus commands or the duty of the PWM-VID signal.

The DVID process is active after VOUT is settled and can be either upward or downward.

In PMBus-VID control mode, the DVID linear slew rate is set with register MFR DVID SR (BAh) and ranges from 0.12 - 125mV/µs, as shown in Equation (8):

6.25mV SlewRate =  $\frac{1}{MFR DVID SR \times 0.05 \mu s}$ (8)

There are two slew rate modes in PWM-VID control mode: R-C filter mode and linear mode.

The DVID R-C filter slew rate is set with register MFR PARM RC CONST (B5h) and ranges from 10.40 - 655.36µs, as shown in Equation (9):

$$\tau_{RC}(\mu s) = \frac{0.32\mu s}{DVID_RC} \times 2^{11}$$

(9)

Where DVID RC is the value in register MFR PARM RC CONST (B5h).

The DVID linear slew rate is set with register MFR DVID SR (BAh) and ranges from 0.12 -125mV/µs (see Equation (8)).

#### VID Offset

The MP2884A supports two types of VID offset.

The first type is VID step offset, which ranges from -0.69375V to 0.7V with 6.25mV of resolution. When the PMBus writes a new offset to register VOUT OFFSET (23h), the VR ramps with the slew rate shown in Equation (8).

The second type is fine-tune offset for the VID set point, which ranges from -31.5mV to 31.5mV with 0.5mV of resolution at a unity gain of the differential voltage sense amplifier and ranges from -50.4mV to 50.4mV with 0.8mV of resolution at a half-gain of differential voltage sense amplifier. Refer to the register map MFR\_RSAMP\_OFFSET (2Dh) section on page 44 for details.

#### Inductor Current Sensing

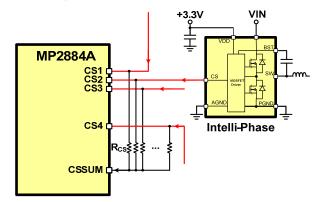

The MP2884A works with the Intelli-Phase for inductor current sensing (see Figure 4). The voltage on CSs is sampled, calculated, and stored in the registers. The results are used for multi-phase current balancing and thermal balancing and can be monitored via the PMBus.

The MP2884A provides cycle-by-cycle perphase current limitation.

The resistor  $(R_{CS})$  is connected from CSx to CSSUM. CSSUM is a 1.23V constant voltage and can sink or source current to provide voltage shifts that meet the operating voltage range of CSs.

Short any unused CSx pin to AGND or CSSUM.

Figure 4: Phase Current Sense

Different types of Intelli-Phase products have different operating voltage ranges for CS (V<sub>CS MIN</sub> and V<sub>CS MAX</sub>). Refer to each Intelli-Phase's datasheet to determine the minimum and maximum operating voltage ranges. Calculate a proper  $R_{CS}$  value with Equation (10):

$$V_{\rm CS MIN} < I_{\rm LOAD} \times K_{\rm CS} \times R_{\rm CS} + 1.23V < V_{\rm CS MAX}$$

(10)

By working with the Intelli-Phase, the MP2884A does not need temperature compensation and impendence matching compared with traditional DCR sensing to achieve an accurate current sense.

#### **Total Current Sensing**

The total current is summed from CSSUM, and a 1/16 proportional current emerges to IMON. Connect a resistor from IMON to AGND to generate a voltage proportional to the output current. The IMON voltage is sampled, calculated, and stored in the registers. This

result is used for total OCP, auto-phase shedding, and output power calculation and can be monitored via the PMBus.

If the auto-phase-shedding function is enabled, the total current report is used to determine the real-time phase number.

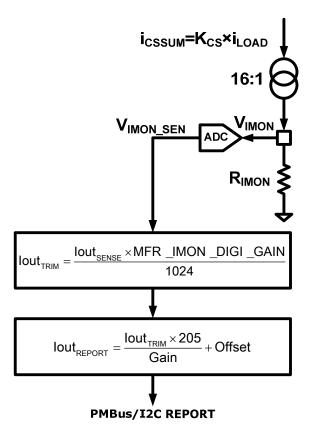

The MP2884A provides a user-programmable scaling factor and a user-programmable current offset. The programmable parameters allow users to match the IMON scaling to the design's voltage regulator tolerance band (VRTOB) calculation. This provides the most accurate current reporting across the entire load range and maximizes the performance of the processor turbo. The scaling factor can also be reduced or offset to under-report the total current to the system for higher performance. Figure 5 shows the MP2884A IMON sense and report block diagram.

Figure 5, the MFR\_IMON\_DIGI\_GAIN In register (2Fh) is used to fine-tune the ADC sense value with 0.1% resolution. The IOUT CAL GAIN register (38h) converts the sensed and trimmed IMON voltage to an ampere format with 0.25A/LSB. The detailed calculation of the register value is provided in the MP2884A application note and register map.

The voltage at IMON can be calculated with Equation (11):

$$V_{\rm IMON} = \left(\frac{K_{\rm CS} \times I_{\rm OUT}}{16}\right) \times R_{\rm IMON}$$

(11)

Where IOUT is the load current, KCS is the current sense gain of the Intelli-Phase, and RIMON is the value of the resistor connected from IMON to ground.

#### **Power Mode**

To improve efficiency over the entire load range, the MP2884A supports automatic phase shedding and adjustable high/low phase count with PSI (see Table 2).

**Table 2: Phase Mode Definition**

| PSI Pin | Mode             |

|---------|------------------|

| High    | High-phase count |

| Hi-Z    | Auto-power mode  |

| Low     | Low-phase count  |

**Figure 5: Current Sense and Report**

In high-phase count mode, the VR is forced to operate with a full-phase count configured in register MFR\_VR\_CONFIG (E1h).

In low-phase count mode, the VR is forced to operate with a low-phase count configured in register MFR\_LOW\_PHASE \_CNT (AAh).

In auto-power mode, the VR can be optimized to adjust the phase count according to the realtime sensed load current.

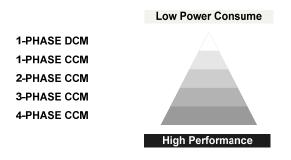

As shown in Figure 6, using 4-phase as an example, the VR works at 4-phase continuous conduction mode (CCM) at heavy loads, and 1phase CCM at light loads to optimize efficiency. 1-phase The VR enters discontinuous conduction mode (DCM) at extremely light loads reduce the switching loss further.

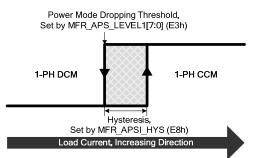

The APM function is implanted by comparing the sensed load current with each power state The MFR APS LEVEL current threshold. (E3h~E7h) registers set the power state dropping thresholds. The hysteresis is set with register MFR\_APS\_HYS (E8h) to prevent the

© 2018 MPS. All Rights Reserved.

converter from changing the power state backand-forth at a steady load current. Figure 7 shows the APM current thresholds setting from 1-phase CCM to 1-phase DCM.

Figure 6: APM Function Diagram at 4-Phase Mode

Table 3 lists the phase shedding and adding entry conditions based on the current report for 4-phase applications.

#### Table 3: Phase Shedding/Adding Based on **Current Report for 4-Phase Applications**

| Condition                                                     | Phase Number |

|---------------------------------------------------------------|--------------|

| MFR_3PH_LOW + MFR_APS_HYS<br>< I <sub>LOAD</sub>              | 4-Ph CCM     |

| MFR_2PH_LOW + MFR_APS_HYS<br>< I <sub>LOAD</sub> ≤MFR_3PH_LOW | 3-Ph CCM     |

| MFR_1PH_LOW + MFR_APS_HYS<br>< I <sub>LOAD</sub> ≤MFR_2PH_LOW | 2-Ph CCM     |

| MFR_DCM_LOW + MFR_APS_HYS<br>< I <sub>LOAD</sub> ≤MFR_1PH_LOW | 1-Ph CCM     |

| $I_{LOAD} \leq MFR_DCM_LOW$                                   | 1-Ph DCM     |

In addition to the sensed output current comparison, the MP2884A provides three APM (listed conditions below) to exit immediately and run in full-phase CCM to accelerate the load transient response and reduce the output voltage undershoot.

- 1. DVID makes the controller run in full-phase CCM. After the output voltage is settled to the target value, the VR resumes APM.

- 2. Load step-up causing a VFB window trip triggers full-phase CCM to reduce the output voltage undershoot.

- 3. Load step-up causing the frequency to change exceeds a programmable threshold and triggers full-phase CCM.

#### Current Balance and Thermal Balance

The MP2884A provides a current balance loop to achieve fair current sharing at multi-phase mode, since different circuit impedances lead to difference phase currents.

The phase current is sensed and calculated with the current reference in the current loop. Each phase's PWM on time is adjusted individually to balance the currents accordingly.

The MP2884A applies  $\Sigma$ - $\Delta$  modulation and delay line-loop technology in the currentbalance modulation to increase the resolution of the function and reduce PWM jitter greatly. The time resolution of the digital system is 5ns. By applying  $\Sigma$ - $\Delta$  modulation technology, the digital PWM resolution can be increased to 0.08ns.

Each current balance loop can also include a programmable phase current offset to achieve thermal balance among the phases. For example, a phase can have a greater cooling capability due to proximity to the airflow, which allows it to take more phase current by increasing the phase current reference with the offset to keep the phase thermal more balanced. The bandwidth of the current proportionalintegral (PI) loop is relatively lower than the output voltage feedback loop, so it barely impacts the output voltage.

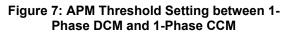

#### Input Voltage Sensing

The input power supply voltage is sampled at VINSEN with a resistor divider (see Figure 8). The sensed input voltage is used for PWM ontime calculation, VIN UVLO, VIN OVP fault protection, VIN UV warning, and input voltage monitoring.

In designs, the divided voltage on VINSEN should not exceed the ADC sampling range (1.6V) at the maximum input voltage. A 1 - 10nF ceramic capacitor from VINSEN to AGND is recommended as an input sense filtering capacitor ( $C_{IN}$ ) (see Figure 8).

Program the input voltage sensing divider ratio with register MFR\_VIN\_SCALE\_LOOP (C0h). The calculation of the ratio ( $K_{IN}$ ) is shown in Equation (12):

$$K_{IN} = \frac{R_{IN2}}{R_{IN1} + R_{IN2}}$$

(12)

=  $\frac{VIN_SCALE_LOOP}{2^{10}}$

Where VIN\_SCALE\_LOOP is the decimal value in the register MFR\_VIN\_SCALE\_LOOP (C0h).

In designs, match the resistor setting  $(K_{\mbox{\scriptsize IN}})$  and register setting value for accurate input voltage sensing.

Figure 8: Input Voltage Sense Connection

#### **Temperature Sense of Intelli-Phase**

The MP2884A senses the Intelli-Phase's temperature by connecting the Intelli-Phase's VTEMP pin to the MP2884A's VTEMP pin (see Figure 9). The sensed temperature is used for over-temperature fault protection, over-temperature warning (assert TALERT#), and power stage temperature monitoring.

Figure 9: Temperature Sense with Intelli-Phase

$C_{\text{TEMP}}$  is a VTEMP pin filtering capacitor (recommend to be a 10nF ceramic capacitor).  $R_{\text{TEMP}}$  is a discharging resistor when the junction temperature is falling (ranging from 10 - 49.9k $\Omega$ ).

The VTEMP pin of the Intelli-Phase reports a voltage proportional to the junction temperature. Set the calculation gain and offset in register MFR\_TEMP\_GAIN\_OFFSET (C1h).

An example of the Intelli-Phase VTEMP voltage is shown in Equation (13):

$$\begin{split} T_{JUNCTION}(^{\circ}C) = &100 \times V_{TEMP}(V) + 10 \\ \text{for} \quad T_{JUNCTION} > &10^{\circ}C \end{split} \tag{13}$$

If VTEMP is 700mV, then the junction temperature of the Intelli-Phase is 80°C. Since VTEMP cannot go below 0V, it reads 0V when the junction temperature is lower than 10°C. Refer to the datasheet of the Intelli-Phase for more information.

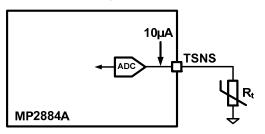

#### **Temperature Sense of the Thermistor**

The MP2884A senses the external thermal component's temperature by connecting a thermistor to TSNS (see Figure 10). The sensed temperature is used for over-temperature fault protection and over-temperature warning (assert TALERT#).

#### Figure 10: Temperature Sense with Thermistor

TSNS sources a  $10\mu$ A current source to the thermistor, and the MP2884A senses the voltage of TSNS. The  $10\mu$ A current source can be disabled via register TSNS\_CURRENT\_DIS (34h bit[10]), and a voltage signal can be connected to TSNS as a new defined protection function.

Note that if the  $10\mu$ A current source is enabled, TSNS cannot be floated.

#### **EEPROM Operation**

The MP2884A provides an EEPROM to store custom configurations. A 4-digit part number suffix is assigned for each application. The default configuration for each 4-digit part can be pre-programmed at the MPS factory. The data programmed again using can be the STORE\_USER\_ALL (15h) command via the PMBus and requires 200ms of time for the data to be stored to the EEPROM. The EEPROM is read automatically during the power-on sequence or by the RESTORE USER ALL (16h) command via the PMBus and requires at least 300µs of time for data to be restored from the EEPROM.

The operation to the EEPROM can be accomplished easily with the MPS GUI software.

The MP2884A uses register DBh to enable EEPROM write protection.

The EEPROM can be erased or written for more than 100,000 cycles. When the EEPROM is write-protected, the write into EEPROM action is ineffective.

#### **EEPROM** Fault

If the data from the EEPROM is checked as invalid by the cyclic redundancy code (CRC) during the system initialization process, the system enters an EEPROM fault state without outputting power and waits for the error clear command. The configuration from the EEPROM is ignored.

There are three ways to clear the EEPROM fault and start up again with the restored value from the EEPROM:

- 1. Clear the EEPROM fault via the PMBus command (FFh).

- 2. Clear the fault status via the PMBus command (03h).

- 3. Store the configuration into the EEPROM and restart.

#### Low-Power Mode

The MP2884A can be programmed to operate in regular-power mode or low-power mode.

In regular-power mode, the PMBus communication is available when EN is low. With low-power mode enabled, when EN is low,

the PMBus communication is disabled, and the quiescent current ( $I_Q$ ) can be reduced to  $150\mu$ A.

Low-power mode is factory-programmable.

#### Power-On

The MP2884A is supplied by a +3.3V voltage at VDD33. VDD33 provides the bias supply for the analog circuit and internal 1.8V LDO. The 1.8V LDO produces the +1.8V supply for the digital circuit. The system is reset by the internal power-on reset signal (POR) after the VDD33 supply is ready. If the MP2884A is in regular-power mode, EN must be high. After the system exits POR, the data in the EEPROM is loaded into the operating registers to configure the VR operation.

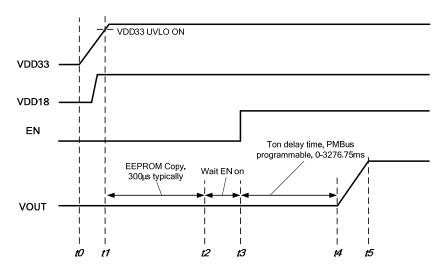

Figure 11a shows the power-on sequence of the MP2884A in regular-power mode.

t0~t1: at t0, VDD33 is supplied by a +3.3V voltage and reaches the VDD33 UVLO\_ON threshold at t1. VDD18 reaches +1.8V when VDD33 is higher than 1.8V.

t1~t2: at t1, the data in the EEPROM starts loading into the operating registers. The entire EEPROM copy process takes about 300µs, typically. During this stage, the PMBus address is detected if the voltage on ADDR is selected to set the PMBus address.

t2~t3: at t2, after the EEPROM copy is finished, the MP2884A waits for EN to pull high. The PMBus is available at this stage.

t3~t4: when EN is high, if the PMBus command OPERATION (01h) is pre-set to an off state. The MP2884A halts at this stage and waits for the OPERATION on command. If OPERATION (01h) is pre-programmed to an on state, the turn-on delay time ( $T_{ON}$  delay) begins counting. The  $T_{ON}$  delay is PMBus-programmable from 0 to 3276.75ms with the command TON\_DELAY (60h).

t4~t5: when the  $T_{ON}$  delay time expires, the VID-DAC starts ramping up  $V_{REF}$  and a programmed slew rate to the boot-up voltage. During soft start, OCP\_Total, OVP, and UVP are masked until  $V_{REF}$  reaches the target value.

In PWM-VID mode, before t5, PWM-VID should remain at a Hi-Z state.

Figure 11a: MP2884A Power-On Sequence at Regular-Power Mode

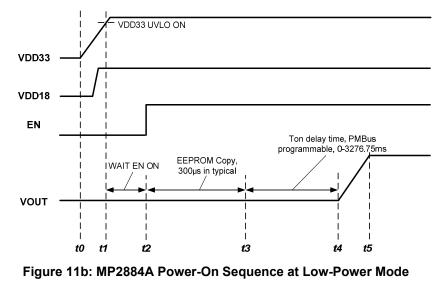

Figure 11b shows the power-on sequence of the MP2884A in low-power mode.

t0~t1: at t0, VDD33 is supplied by a +3.3V voltage and reaches the VDD33 UVLO\_ON threshold at t1. VDD18 reaches +1.8V when VDD33 is greater than 1.8V.

t1~t2: after t1, VDD33 rises above the UVLO\_ON threshold, and the MP2884A waits for EN to pull high. The PMBus is unavailable at this stage.

t2~t3: at t2, EN pulls high, the data in the EEPROM starts loading into the operating registers. The entire EEPROM copy process takes about 300µs, typically. During this stage, the PMBus address is detected if the voltage on ADDR is selected to set the PMBus address.

t3~t4: after the EEPROM copy is finished, if the PMBus command OPERATION (01h) is pre-set to an off state. The MP2884A halts at this stage and waits for an OPERATION on command. If OPERATION (01h) is pre-programmed to an on state, the turn-on delay time ( $T_{ON}$  delay) begins counting. The  $T_{ON}$  delay is PMBus-programmable from 0 to 3276.75ms with the command TON\_DELAY (60h).

t4~t5: when the  $T_{ON}$  delay time expires, the VID-DAC starts ramping up  $V_{REF}$  with a programmed slew rate to the boot-up voltage. During soft start, OCP\_Total, OVP, and UVP are masked until  $V_{REF}$  reaches the target value.

In PWM-VID mode, before t5, PWM-VID should remain at Hi-Z.

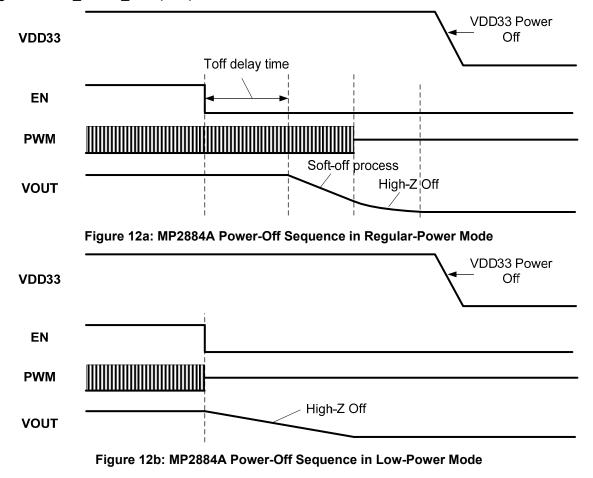

#### **Power-Off**

The MP2884A can be powered off by the OPERATION command, EN, or VDD33.

- <u>OPERATION command off</u>: The MP2884A provides Hi-Z off and soft off with commands. During soft off, V<sub>OUT</sub> drops down with a pre-programmed slew rate in register MFR\_BOOT\_SR (B9h) until V<sub>REF</sub> reaches the level of register MFR\_VID\_SD (BCh) and then enters Hi-Z off. This prevents V<sub>OUT</sub> from becoming negative during the shutdown process. A turn-off delay can be set via register TOFF\_DELAY (64h).

- <u>EN off:</u> The MP2884A provides Hi-Z off and soft-off when EN is pulled low in regularpower mode. During soft off, V<sub>OUT</sub> drops down with a pre-programmed slew rate in register MFR\_BOOT\_SR (B9h) until V<sub>REF</sub>

reaches the level of register MFR\_VID\_SD (BCh) and then enters Hi-Z off. This prevents  $V_{OUT}$  from becoming negative during the shutdown process. A turn-off delay can be set via TOFF DELAY (64h).

In low-power mode when EN is pulled low, the MP2884A can enter Hi-Z off without any turn-off delay immediately, and enters standby mode with the smallest amount of power consumption.

<u>VDD33 power-off:</u> When the voltage on VDD33 falls below the UVLO threshold, the MP2884A powers off immediately. All PWMs enter Hi-Z.

Figure 12a shows the EN soft-off power sequence in regular-power mode.

Figure 12b shows the EN Hi-Z off power sequence in low-power mode.

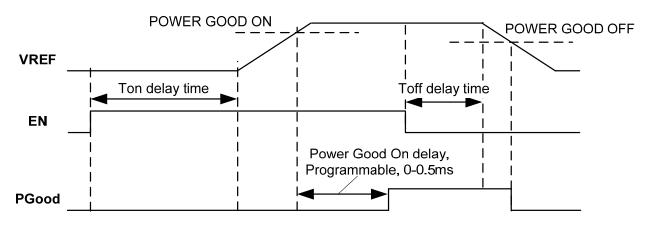

#### Power Good Indication (PGOOD)

The MP2884A power good (PGOOD) on/off thresholds are programmable via POWER\_GOOD\_ON (5Eh) and POWER\_GOOD\_OFF (5Fh).

During the soft-start process, when  $V_{REF}$  rises above the POWER\_GOOD\_ON threshold, the MP2884A starts a delay counter before asserting PGOOD. The delay counter time is programmable via register MFR\_DELAY\_SET (5Dh).

During the soft-shutdown process, when  $V_{REF}$  falls below the POWER\_GOOD\_OFF threshold, the MP2884A de-asserts PGOOD immediately. The POWER\_GOOD\_OFF threshold must be set below the VID value, which is regulated during the normal operation process.

For Hi-Z shutdown caused by protections or EN turning off, PGOOD is de-asserted immediately. Figure 13 shows the power good indication in regular-power mode.

#### V<sub>FB</sub> Window

The MP2884A has a feedback voltage (V<sub>FB</sub>) window (V<sub>REF</sub>  $\pm$  25mV), which provides an advanced non-linear loop control to fasten the transient performance.

When  $V_{FB}$  is higher than  $V_{REF}$  + 25mV ( $V_{FB}$  positive window limit), all PWMs pull low and blank the PWM set signal until  $V_{FB}$  falls below the positive limit. The  $V_{FB}$  positive window is used to reduce the output voltage overshoot at the load release, typically, especially in multiphase operation.

When  $V_{FB}$  is lower than  $V_{REF}$  - 25mV ( $V_{FB}$  negative window limit), VR exits auto-power mode immediately and enters full-phase running to improve the transient response.

#### **Fault and Protections**

The MP2884A supports the following fault monitoring and protections.

#### VIN UVLO and OVP

The VR can shut down immediately by forcing the PWM signals into tri-state if the sensed input voltage is below the VIN\_OFF threshold. The VR restarts when the sensed input voltage is above the VIN\_ON threshold. The V<sub>IN</sub> UVLO threshold is programmable with register VIN\_ON (35h) and VIN\_OFF (36h) with 0.125V/LSB.

VR latches if the input voltage is above the  $V_{IN}$  OVP threshold, which is set with register VIN\_OV\_FAULT\_LIMIT (55h).

#### **Over-Current Protection (OCP)**

OCP applies a dual OCP mechanism with two types of thresholds.

The first OCP type, OCP\_Total, is a time- and current-based threshold. The PMBus sets the OCP\_Total threshold using MFR\_OCP\_TOTAL (ECh). OCP\_Total should trigger when the sensed average output current exceeds the

threshold for a period of time referred to as the OCP blanking time. OCP\_Total can be programmed to no action, hiccup, retry six times, and latch-off mode via the PMBus.

The controller does not take action in no action mode and keeps the PWMs switching. The fault indication bit in register STATUS\_IOUT (7Bh) and STATUS\_WORD (79h) is not set in no action mode.

In hiccup mode, the controller forces the PWM signals into tri-state to disable the output. The controller attempts to restart after 12.5ms of protection delay time.

In retry six times mode, the VR hiccups six times at most. If the fault is removed within the six restarts, the VR resumes normal operation. If the fault remains after the six restarts, the VR shuts down until a new power cycle, an EN toggle, or a PMBus COMMAND ON occurs.

In latch mode, the VR shuts down until a new power cycle, an EN toggle, or a PMBus COMMAND on occurs.

These four protection types are also available for  $V_{\text{OUT}}$  UVP and  $V_{\text{OUT}}$  OVP2.

The second OCP type, OCP\_Phase, is a current-based limitation threshold. The MP2884A monitors the phase current cycle-by-cycle. When the phase current exceeds the OCP\_Phase threshold at the PWM off time, the PWM remains low to discharge the inductor current. If the load current continues rising, the output voltage drops because the inductor current is limited. OCP\_Phase is implemented with  $V_{OUT}$  UVP, generally. The OCP\_Phase threshold is PMBus-programmable with register MFR\_OCP\_PHASE (EDh).

#### Under-Voltage Protection (UVP)

The MP2884A monitors the VDIFF voltage to provide UVP and uses a dual UVP approach.

The first UVP type, UVP1, is a digital UVP. UVP1 is triggered when the internal ADC senses that the VDIFF voltage is lower than the threshold for a pre-set blanking time. The UVP1 threshold can be set from 0 - 480mV with 32mV of resolution. Refer to the register MFR\_SYS\_CONFIG (44h) section on page 54. The second UVP type, UVP2, is triggered when the VDIFF voltage is lower than the threshold for a pre-set blanking time. The register OVUV\_LEVEL (2Ch) can program the UVP2 threshold to  $V_{REF}$  - 430mV,  $V_{REF}$  - 310mV or  $V_{REF}$  - 190mV. Refer to the MFR\_OVUV\_SEL (2Ch) section on page 44. When programming the gain of the differential voltage sense amplifier as half, the UVP2 threshold is doubled. For example, set the register to a -430mV level to achieve the V<sub>REF</sub> - 860mV threshold.

The UVP scheme is the same as the OCP\_Total protection scheme. When the VDIFF voltage is lower than the UVP threshold for a given amount of time (UVP blanking time), the controller forces the PWM signals into tristate to disable the output. The register MFR\_OVP\_UVP\_SET (EEh) sets the UVP mode and blanking time. Like the OCP\_Total protection scheme, the UVP scheme also provides no action, hiccup, retry six times, and latch-off options.

#### Over-Voltage Protection (OVP)

The MP2884A monitors the VDIFF voltage to provide OVP and uses a dual OVP approach (described below). When OVP is triggered, the MP2884A pulls all activated PWMs low to turn on the low-side MOSFET to discharge the output capacitors until  $V_{OUT}$  reaches +300mV. Then all PWMs are set to Hi-Z.

The first OVP type, OVP1, is triggered when the VDIFF voltage is higher than the OVP1 threshold without any delay time. The OVP1 fault is in latch-off mode.

The OVP1 threshold is VOUT\_MAX (24h) +400mV, regardless of the gain of the differential voltage sense amplifier.

The second OVP type, OVP2, is triggered when the VDIFF voltage above the OVP2 threshold for a pre-set blanking time. Just like in UVP, the MP2884A provides no action, hiccup, retry six times, and latch-off modes for the OVP2 fault.

The register MFR\_OVUV\_LEVEL (2Ch) can program the OVP2 level to  $V_{REF}$  + 430mV,  $V_{REF}$ + 310mV, and  $V_{REF}$  + 190mV. Refer to the MFR\_OVUV\_SEL (2Ch) section on page 44. When programming the gain of the differential voltage sense amplifier as half, the OVP2 threshold is doubled. For example, set the MP2884A - DIGITAL PWM CONTROLLER WITH PMBUS AND PWM-VID

register to a +190mV level to achieve the  $V_{\text{REF}}$  + 380mV threshold.

#### **Over-Temperature Protection (OTP)**

The MP2884A uses a dual OTP approach.

The first OTP type is VTEMP protection from the Intelli-Phase (see Figure 9). If the VTEMP report value is higher than the threshold in the register OT\_WARN\_LIMIT (51h), TALERT# is asserted.

If the VTEMP report value is higher than the threshold in the register VTEMP\_OTP\_THRE (EAh), the VR Hi-Z shuts down.

The VTEMP fault can be programmed to either latch-off mode or hiccup mode via register VTEMP\_OTP\_MODE (EAh).

The second OTP type is TSNS protection from the thermistor (see Figure 10). If the TSNS report value is higher than the threshold in register TSNS\_T\_ALT\_THRE (34h), TALERT# is asserted. If the TSNS report value is higher than the threshold in register TSNS\_OTP\_ THRE (E9h), the VR shuts down.

The TSNS fault can be programmed to no action, latch-off, or hiccup mode via register TSNS\_OTP\_MODE (E9h).

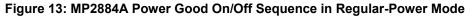

#### Intelli-Phase Fault Detection

When VTEMP is pulled up to 3.3V or any CS pin is pulled down to 0V, the MP2884A latches off immediately. These protections are called VTEMP fault protection and CS fault protection.

When VTEMP or CS fault protection occurs, the MP2884A can detect the fault type of the Intelli-Phase. There are four typical fault types:

- Over-current fault

- Over-temperature fault

- Low-side MOSFET fault

- High-side MOSFET fault

Fault type detection only works when the Intelli-Phase supports fault type indication via PWMx. Refer to the datasheet of the Intelli-Phase for specific details. Figure 14 shows the flow chart of Intelli-Phase fault detection.

#### Figure 14: Flow Chart of Intelli-Phase Fault Detection

The related registers are described below.

- The enable bit of the VTEMP and CS fault function is bit[9:8] of MFR\_PROTECT\_DIS (3Ah).

- 2. The enable bit of the ADC sampling the fault type from the Intelli-Phase PWM is bit[10] of MFR\_PROTECT\_DIS (3Ah).

- The enable bit to record a fault to the EEPROM is bit[1] of MFR\_EEPROM\_CTRL (06h).

#### Protection Type Storage in the EEPROM

Once any protection occurs, the fault type is recorded to Page 0's registers F8h ~ FBh. If the EEPROM fault record is enabled, the last fault event is recorded in Page 29's registers FBh ~ FEh. EN must remain high for at least 20ms after the fault occurs to save the fault type into the EEPROM.

To clear the fault record in the EEPROM registers, 0x0000 must be written to these registers (Page 29 FBh ~ FEh). This is a direct access to the EEPROM registers. The time required for each write command is 5ms.

#### **Phase Number Configuration**

The MP2884A can be configured to different phase numbers via the PMBus register or by CSx (see Table 4).

Table 4: Phase Number Configuration and Activated PWM Pins

| PHASE_CNT (E1h) | Activated PWM Pins |

|-----------------|--------------------|

| 1               | PWM1               |

| 2               | PWM1~2             |

| 3               | PWM1~3             |

| 4               | PWM1~4             |

If PHASE\_CNT is set to 0, the MP2884A operates in 1-phase DCM.

Any unused PWM pin enters tri-state, and the activated phases interleave automatically. Float the unused PWM pins. For the Intelli-Phase, if the PWM input is in Hi-Z, the SW node is in Hi-Z as well.

If the CS pins are enabled to program the phase number, the register setting in E1h is ignored. Pull down the unused CS pins to ground. After EN is pulled high, the MP2884A checks the voltage on the CS pins sequentially from CS1 to CS4 until it finds the first low voltage. Figure 15 shows an example of the connection for 3-phase applications. The first low voltage is on CS4.

Figure 15: CS Pins Program to 3-Phase

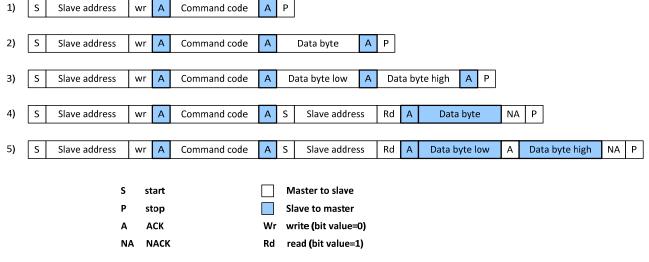

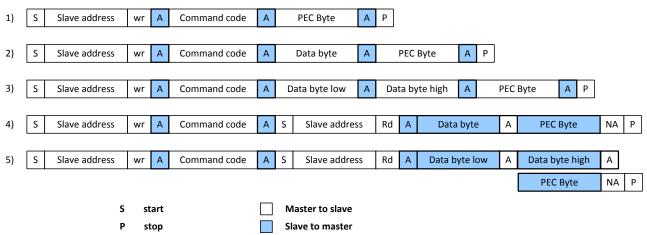

#### PMBUS/I<sup>2</sup>C COMMUNICATION

#### **General Description**

The Power Management Bus (PMBus) is an open-standard, power-management protocol that defines a means of communicating with power conversion and other devices. The PMBus is a two-wire, bidirectional serial interface consisting of a data line (SDA) and a clock line (SCL). The lines are pulled to a bus voltage externally when they are idle. When connecting the PMBus to the line, a master device generates the SCL signal and device address and arranges the communication sequence. This is based on the principles of I<sup>2</sup>C operation.

The MP2884A supports 100kHz, 400kHz, and 1MHz bus timing requirements. Timing and electrical characteristics of the PMBus can be found in the Electrical Characteristics section on page 7 to page 9 or in the PMBus Power Management Protocol Specification part 1, revision 1.3 available at http://PMBus.org.

#### PMBus/I<sup>2</sup>C Address

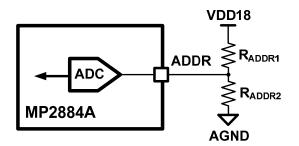

To support multiple VR devices being used with the same PMBus/I<sup>2</sup>C interface, the MP2884A provides PMBus address programming via ADDR or a register.

The device address is a 7-bit code and ranges from 0x00 to 0x7F. The 3MSB bits are set by the register. The 4LSB bits can be set either by the register or by the ADDR voltage.

The address of 00h is reserved as the all-call address. Do not use 00h as the MP2884A address.

The register MFR\_PMBUS\_ADDR (BEh) is used to program or store the device address. Bit[7] sets the mode of the 4LSB address. When bit[7] = 0, the 4LSB bits are determined by the voltage of ADDR, and its value is stored in register BEh bit[3:0] automatically.

The ADDR voltage can be set by a resistor divider (see Figure 16). Using 3MSB = 3'b010 as an example, Table 6 shows the resistor values for different 4LSB addresses.

Table 6: Pin Configuration for PMBus/I<sup>2</sup>C Address

| Address          |                      |                               |                               |  |  |  |

|------------------|----------------------|-------------------------------|-------------------------------|--|--|--|

| PMBus<br>Address | Setting<br>Point (V) | R <sub>ADDR1</sub><br>(kΩ) 1% | R <sub>ADDR2</sub><br>(kΩ) 1% |  |  |  |

| 20h              | 0                    | -                             | 0                             |  |  |  |

| 21h              | 0.031                | 3.32                          | 0.059                         |  |  |  |

| 22h              | 0.057                | 3.32                          | 0.11                          |  |  |  |

| 23h              | 0.084                | 3.32                          | 0.162                         |  |  |  |

| 24h              | 0.116                | 3.32                          | 0.226                         |  |  |  |

| 25h              | 0.156                | 3.32                          | 0.316                         |  |  |  |

| 26h              | 0.205                | 3.32                          | 0.43                          |  |  |  |

| 27h              | 0.266                | 3.32                          | 0.576                         |  |  |  |