# Triple Channel PWM Controller with Integrated Driver for IMVP8 Mobile CPU Core Power Supply

# **General Description**

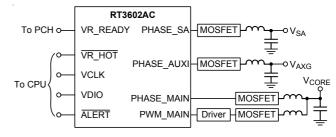

The RT3602AC is an IMVP8 compliant CPU power controller which includes three voltage rails: a 2/1 phase synchronous Buck controller, the MAIN VR, a single phase synchronous Buck controller, the auxiliary VR, and a single phase synchronous Buck controller, the VCCSA VR. The RT3602AC adopts G-NAVP<sup>TM</sup> (Green Native AVP) which is Richtek's proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all Intel CPU requirements of AVP (Adaptive Voltage Positioning). Based on the G-NAVP<sup>TM</sup> topology, the RT3602AC also features a quick response mechanism for optimized AVP performance during load transient. The RT3602AC supports mode transition function with various operating states. A serial VID (SVID) interface is built in the RT3602AC to communicate with Intel IMVP8 compliant CPU. The RT3602AC supports VID on-the-fly function with three different slew rates: Fast, Slow and Decay. By utilizing the G-NAVP<sup>TM</sup> topology, the operating frequency of the RT3602AC varies with VID, load and input voltage to further enhance the efficiency even in CCM. Moreover, the G-NAVP<sup>TM</sup> with CCRCOT (Constant Current Ripple COT) technology provides superior output voltage ripple over the entire input/output range. The built-in high accuracy DAC converts the SVID code ranging from 0.25V to 1.52V with 5mV per step. The RT3602AC integrates a high accuracy ADC for platform setting functions, such as quick response trigger level. Besides, the setting function also supposes this two rails address exchange. The RT3602AC provides VR ready output signals. It also features complete fault protection functions including over-voltage (OV), negative voltage (NV), over-current (OC) and under-voltage lockout (UVLO). The RT3602AC is available in the WQFN-52L 6x6 small foot print package.

#### **Features**

- Intel IMVP8 Serial VID Interface Compatible Power Management States

- 2/1 Phase (MAIN VR) + Single Phase (Auxiliary VR)

+ Single Phase (VCCSA VR) PWM Controller

- 1 Embedded MOSFET Driver at the MAIN VR, 1 Embedded MOSFET Driver at the Auxiliary VR, and Embedded MOSFET Driver at the VCCSA VR

- G-NAVP<sup>™</sup> (Green Native Adaptive Voltage Positioning) Topology

- 0.5% DAC Accuracy

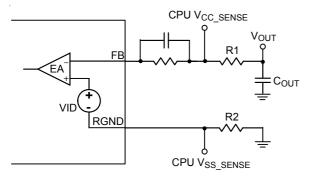

- Differential Remote Voltage Sensing

- Built-in ADC for Platform Programming

- Accurate Current Balance

- System Thermal Compensated AVP

- Diode Emulation Mode at Light Load Condition for Multiple or Single Phase Operation

- Fast Transient Response

- VR Ready Indicator

- Thermal Throttling

- Current Monitor Output

- OVP, OCP, NVP, UVLO

- Slew Rate Setting/Address Flip Function

- DVID Enhancement

# **Applications**

- IMVP8 Intel Core Supply

- Notebook/Desktop Computer/ Servers Multi-Phase CPU Core Supply

- AVP Step-Down Converter

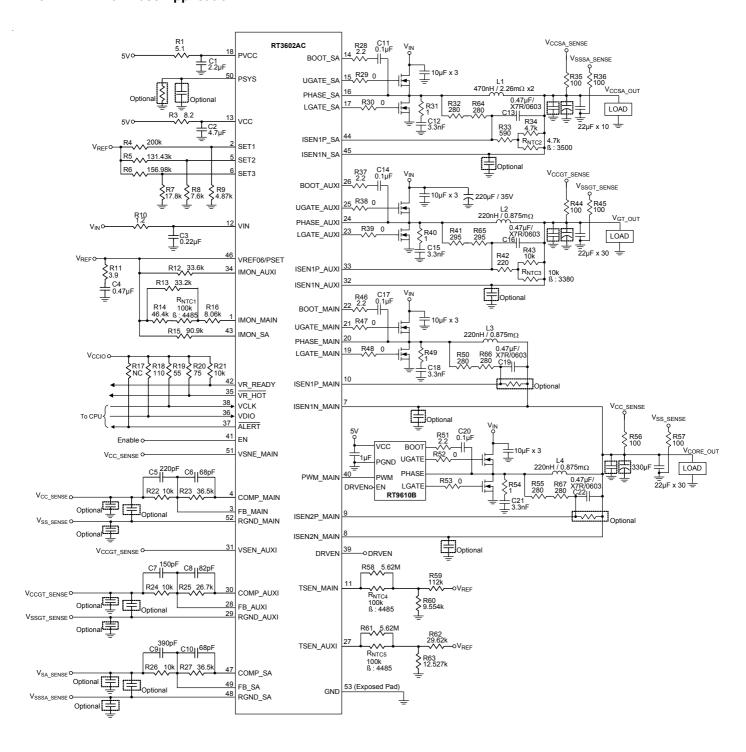

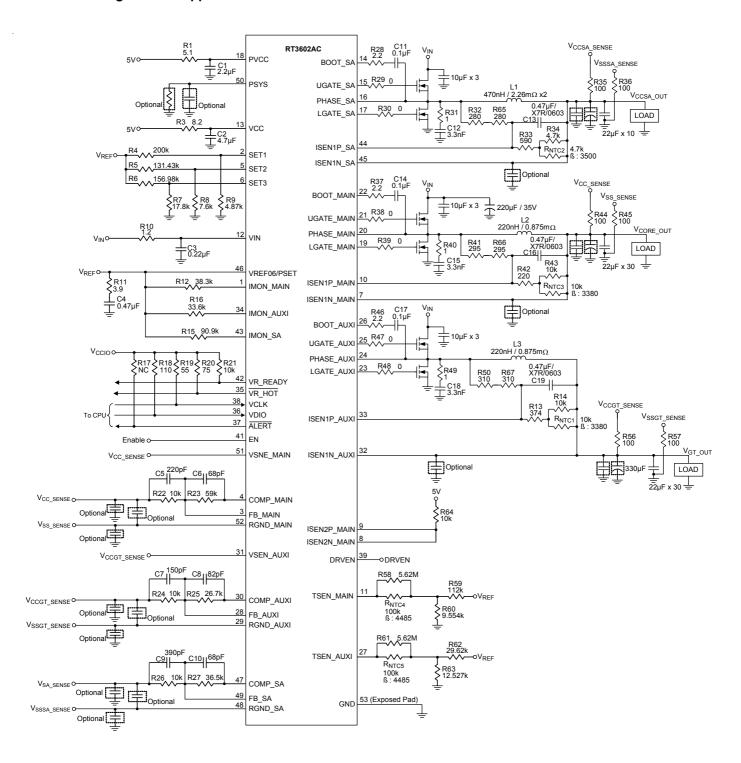

# Simplified Application Circuit

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Ordering Information**

RT3602AC□□

Package Type

QW: WQFN-52L 6x6 (W-Type)

Lead Plating System

G: Green (Halogen Free and Pb Free)

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

RT3602AC **GQW YMDNN**

RT3602ACGQW: Product Number

YMDNN: Date Code

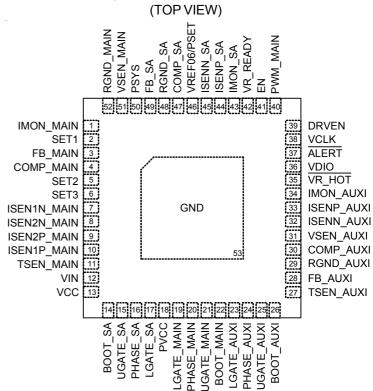

# **Pin Configuration**

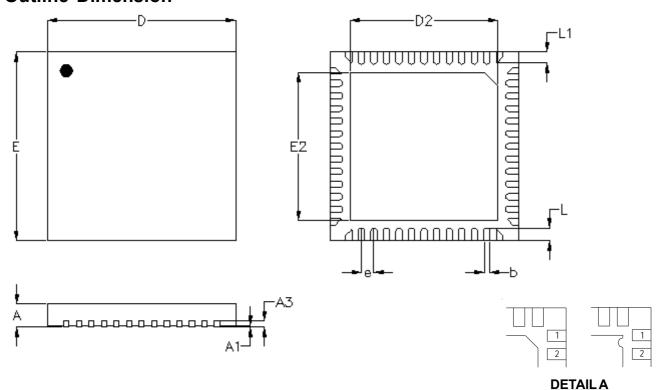

WQFN-52L 6x6

# **Functional Pin Description**

| Pin No | Pin Name         | Pin Function                                                                                                                                                                                                                                                        |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

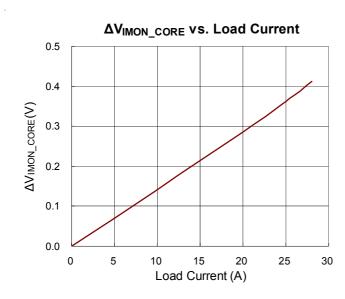

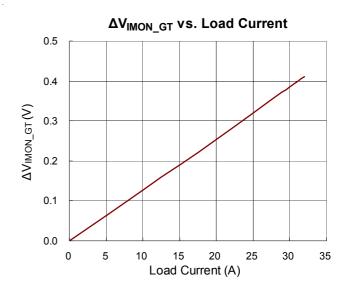

| 1      | IMON_MAIN        | MAIN rail VR current monitor output. This pin outputs a voltage proportional to the output current.                                                                                                                                                                 |

| 2      | SET1             | Platform setting. Platform can use this pin to set switching frequency, ki gain, QRTH, QR width and anti-overshoot for Auxiliary VR. Connect the SET1 pin to 5V and turn-on the EN pin, if the soldering is good, VSEN_MAIN = VSEN_AUXI = 1.1V and VSEN_SA = 1.05V. |

| 3      | FB_MAIN          | Negative Input of the error amplifier. This pin is for MAIN rail VR output voltage feedback to controller.                                                                                                                                                          |

| 4      | COMP_MAIN        | MAIN rail VR compensation. This pin is error amplifier output pin.                                                                                                                                                                                                  |

| 5      | SET2             | Platform setting. Platform can use this pin to set switching frequency, ki gain, QRTH, QR width and anti-overshoot for MAIN VR.                                                                                                                                     |

| 6      | SET3             | Platform setting. Platform can use this pin to set switching frequency, ki gain zero load-line, QRTH and QR width for VCCSA rail. And it can be set DVID TH and force-non-zero VBOOT function for MAIN and AUXI rail.                                               |

| 7, 8   | ISEN[1:2]N_MAIN  | Negative current sense inputs of multi-phase MAIN rail VR Channel 1 and 2.                                                                                                                                                                                          |

| 10, 9  | ISEN[1:2]P_ MAIN | Positive current sense inputs of multi-phase MAIN rail VR Channel 1 and 2.                                                                                                                                                                                          |

| 11     | TSEN_ MAIN       | Thermal sense input for MAIN rail VR.                                                                                                                                                                                                                               |

| 12     | VIN              | VIN input pin. Connect a low pass filter to this pin to set on-time.                                                                                                                                                                                                |

| 13     | VCC              | Controller power supply. Connect this pin to 5V and place a decoupling capacitor $2.2\mu F$ at least. The decoupling capacitor is as close PWM controller as possible.                                                                                              |

| Pin No | Pin Name   | Pin Function                                                                                                                                           |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14     | BOOT_SA    | Bootstrap supply for high-side gate MOSFET driver for VCCSA VR.                                                                                        |

| 15     | UGATE_SA   | High-side driver output for VCCSA VR. Connect the pin to the gate of high-side MOSFET.                                                                 |

| 16     | PHASE_SA   | Switch node of high-side driver for VCCSA VR. Connect the pin to high-side MOSFE source together with the low-side MOSFET drain and inductor.          |

| 17     | LGATE_SA   | Low-side driver output for VCCSA VR. This pin drives the gate of low-side MOSFET.                                                                      |

| 18     | PVCC       | Driver power supply input. Connect this pin to GND by a minimum 2.2µF ceramic Capacitor.                                                               |

| 19     | LGATE_MAIN | Low-side driver output for MAIN rail VR. This pin drives the gate of low-side MOSFET.                                                                  |

| 20     | PHASE_MAIN | Switch node of high-side driver for MAIN rail VR. Connect the pin to high-side MOSFE source together with the low-side MOSFET drain and inductor.      |

| 21     | UGATE_MAIN | High-side driver output for MAIN rail VR. Connect the pin to the gate of high-side MOSFET.                                                             |

| 22     | BOOT_MAIN  | Bootstrap supply for high-side gate MOSFET driver for MAIN rail VR.                                                                                    |

| 23     | LGATE_AUXI | Low-side driver output for auxiliary rail VR. This pin drives the gate of low-side MOSFET.                                                             |

| 24     | PHASE_AUXI | Switch node of high-side driver for auxiliary rail VR. Connect the pin to high-side MOSFE source together with the low-side MOSFET drain and inductor. |

| 25     | UGATE_AUXI | High-side driver output for auxiliary rail VR. Connect the pin to the gate of high-side MOSFET.                                                        |

| 26     | BOOT_AUXI  | Bootstrap supply for high-side gate MOSFET driver for auxiliary rail VR.                                                                               |

| 27     | TSEN_AUXI  | Thermal sense input for VR.                                                                                                                            |

| 28     | FB_AUXI    | Negative input of the error amplifier. This pin is for auxiliary rail VR output voltage feedback to controller.                                        |

| 29     | RGND_AUXI  | Return ground for auxiliary rail VR. This pin is the negative node of the differential remote voltage sensing.                                         |

| 30     | COMP_AUXI  | Auxiliary rail VR compensation. This pin is error amplifier output pin.                                                                                |

| 31     | VSEN_AUXI  | AUXI VR voltage sense input. This pin is connected to the terminal of AUXI VR output voltage.                                                          |

| 32     | ISENN_AUXI | Negative current sense input of single-phase AUXI rail.                                                                                                |

| 33     | ISENP_AUXI | Positive current sense input of single-phase AUXI rail.                                                                                                |

| 34     | IMON_AUXI  | Auxiliary rail VR current monitor output. This pin outputs a voltage proportional to the output current.                                               |

| 35     | VR_HOT     | Thermal monitor output, this pin is active low.                                                                                                        |

| 36     | VDIO       | VR and CPU data transmission interface.                                                                                                                |

| 37     | ALERT      | SVID alert. (Active low)                                                                                                                               |

| 38     | VCLK       | Synchronous clock from the CPU.                                                                                                                        |

| 39     | DRVEN      | External driver enable control. Connecting to driver enable pin.                                                                                       |

| 40     | PWM_MAIN   | PWM outputs for MAIN VR.                                                                                                                               |

| 41     | EN         | VR enable control input.                                                                                                                               |

| 42     | VR_READY   | VR ready indicator.                                                                                                                                    |

| Pin No              | Pin Name    | Pin Function                                                                                                                                                                                               |  |  |  |  |  |

|---------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

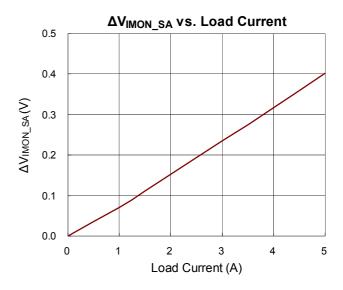

| 43                  | IMON_SA     | VCCSA rail VR current monitor output. This pin outputs a voltage proportional to the output current.                                                                                                       |  |  |  |  |  |

| 44                  | ISENP_SA    | Positive current sense input of single-phase VCCSA rail VR.                                                                                                                                                |  |  |  |  |  |

| 45                  | ISENN_SA    | Negative current sense input of single-phase VCCSA rail VR.                                                                                                                                                |  |  |  |  |  |

| 46                  | VREF06/PSET | Fixed 0.6V output reference voltage. This voltage is used to offset the outp voltage of IMON pin. Between this pin and GND must be placed a exa $0.47\mu F$ decoupling capacitor and $3.9\Omega$ resistor. |  |  |  |  |  |

| 47                  | COMP_SA     | VCCSA rail VR compensation. This pin is error amplifier output pin.                                                                                                                                        |  |  |  |  |  |

| 48                  | RGND_SA     | Return ground for VCCSA rail VR. This pin is the negative node of the differential remote voltage sensing.                                                                                                 |  |  |  |  |  |

| 49                  | FB_SA       | Negative input of the error amplifier. This pin is for VCCSA rail VR output voltage feedback to controller.                                                                                                |  |  |  |  |  |

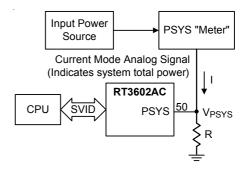

| 50                  | PSYS        | System input power monitor. Place the PSYS resistor as close to the IC as possible.                                                                                                                        |  |  |  |  |  |

| 51                  | VSEN_MAIN   | MAIN VR voltage sense input. This pin is connected to the terminal of MAIN VR output voltage.                                                                                                              |  |  |  |  |  |

| 52                  | RGND_MAIN   | Return ground for MAIN rail VR. This pin is the negative node of the differential remote voltage sensing.                                                                                                  |  |  |  |  |  |

| 53<br>(Exposed Pad) | GND         | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                |  |  |  |  |  |

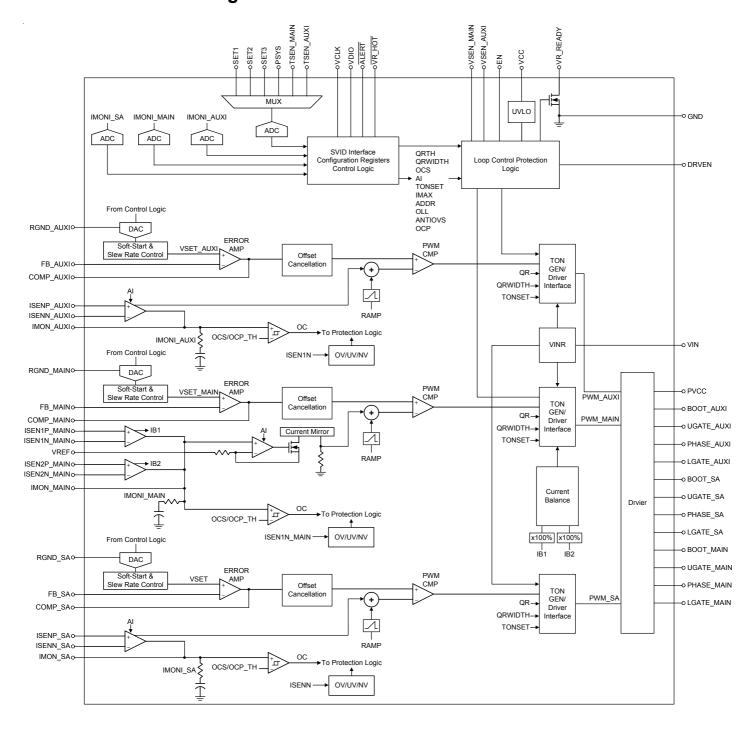

# **Functional Block Diagram**

# **Operation**

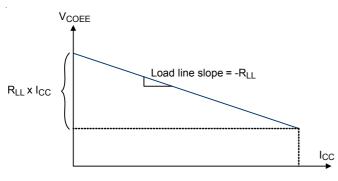

The RT3602AC adopts G-NAVP<sup>TM</sup> (Green Native AVP) which is Richtek's proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all Intel CPU requirements of AVP (Adaptive Voltage Positioning).

The G-NAVP<sup>TM</sup> controller is one type of current mode constant on-time control with DC offset cancellation. The approach can not only improve DC offset problem for increasing system accuracy but also provide fast transient response. When current feedback signal reaches COMP signal, the RT3602AC generates an on-time width to achieve PWM modulation.

#### **TON GEN/Driver Interface PWMx**

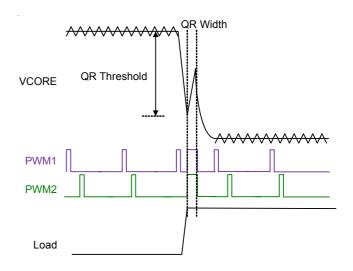

Generate the sequentially according to the phase control signal from the Loop Control/Protection Logic. Pulse width is determined by current balance result and pin setting. Once quick response mechanism is triggered, VR will allow all PWM to turn on at the same time. PWM status is also controlled by Protection Logic. Different protections may cause different PWM status (Both High-Z or LG turnon).

## **SVID Interface/Configuration Registers/Control** Logic

The interface receives the SVID signal from CPU and sends the relative signals to Loop Control/Protection Logic for loop control to execute the action by CPU. The registers save the pin setting data from ADC output. The Control Logic controls the ADC timing, generates the digital code of the VID for VSEN voltage.

#### **Loop Control/Protection Logic**

It controls the power on sequence, the protection behavior, and the operational phase number.

#### **MUX and ADC**

The MUX supports the inputs from SET1, SET2, SET3, IMON\_MAIN, IMON\_AUXI, TSEN\_MAIN and TSEN\_AUXI. The ADC converts these analog signals to digital codes for reporting or performance adjustment.

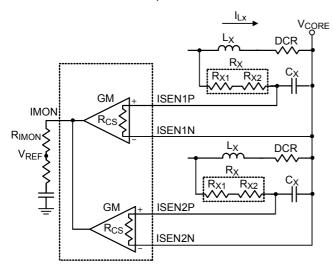

#### **Current Balance**

Each phase current sense signal is sent to the current balance circuit which adjusts the on-time of each phase to optimize current sharing.

#### Offset Cancellation

Cancel the current/voltage ripple issue to get the accurate VSEN.

#### **UVLO**

Detect the VCC voltage and issue POR signal as they are high enough.

#### DAC

Generate an analog signal according to the digital code generated by Control Logic.

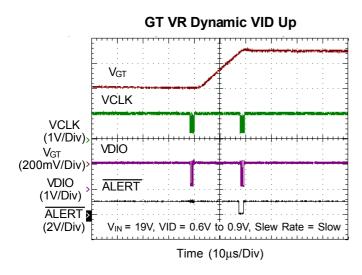

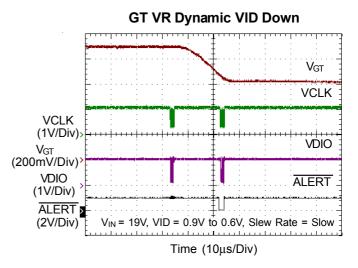

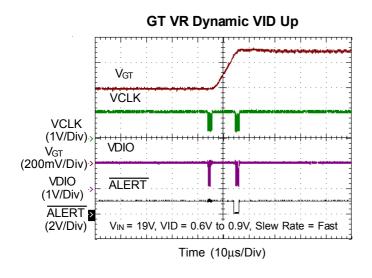

Soft-Start & Slew Rate Control

Control the Dynamic VID slew rate of VSEN according to the SetVID fast or SetVID slow.

#### **Error Amp**

Error amplifier generates COMP\_MAIN/COMP\_AUXI/ COMP SA signal by the difference between output of MAIN/Auxiliary/SA rail and FB\_MAIN/FB\_AUXI/FB\_SA.

#### **PWM CMP**

The PWM comparator compares COMP signal and current feedback signal to generate a signal for TON trigger.

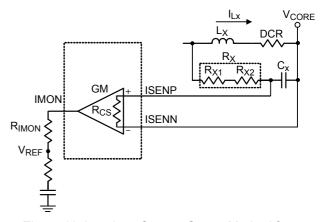

#### **IMON Filter**

IMON Filter is used for average sum current signal by analog RC filter.

Table 1. IMVP8 VID Code Table

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 01  | 0.25        |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 02  | 0.255       |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 03  | 0.26        |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 04  | 0.265       |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 05  | 0.27        |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 06  | 0.275       |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 07  | 0.28        |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 08  | 0.285       |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 09  | 0.29        |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0A  | 0.295       |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0B  | 0.3         |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0C  | 0.305       |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0D  | 0.31        |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0E  | 0.315       |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0F  | 0.32        |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 10  | 0.325       |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 11  | 0.33        |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 12  | 0.335       |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 13  | 0.34        |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 14  | 0.345       |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 15  | 0.35        |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 16  | 0.355       |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 17  | 0.36        |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 18  | 0.365       |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 19  | 0.37        |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1A  | 0.375       |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1B  | 0.38        |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1C  | 0.385       |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1D  | 0.39        |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1E  | 0.395       |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1F  | 0.4         |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 20  | 0.405       |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 21  | 0.41        |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 22  | 0.415       |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 23  | 0.42        |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 24  | 0.425       |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 25  | 0.43        |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 26  | 0.435       |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 27  | 0.44        |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 28  | 0.445       |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 29  | 0.45        |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 2A  | 0.455       |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 2B  | 0.46        |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 2C  | 0.465       |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 2D  | 0.47        |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 2E  | 0.475       |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 2F  | 0.48        |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 30  | 0.485       |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 31  | 0.49        |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 32  | 0.495       |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 33  | 0.5         |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 34  | 0.505       |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 35  | 0.51        |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 36  | 0.515       |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 37  | 0.52        |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 38  | 0.525       |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 39  | 0.53        |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 3A  | 0.535       |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 3B  | 0.54        |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 3C  | 0.545       |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 3D  | 0.55        |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 3E  | 0.555       |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 3F  | 0.56        |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 40  | 0.565       |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 41  | 0.57        |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 42  | 0.575       |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 43  | 0.58        |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 44  | 0.585       |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 45  | 0.59        |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 46  | 0.595       |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 47  | 0.6         |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 48  | 0.605       |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 49  | 0.61        |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 4A  | 0.615       |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 4B  | 0.62        |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 4C  | 0.625       |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 4D  | 0.63        |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 4E  | 0.635       |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 4F  | 0.64        |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 50  | 0.645       |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 51  | 0.65        |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 52  | 0.655       |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 53  | 0.66        |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 54  | 0.665       |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 55  | 0.67        |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 56  | 0.675       |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 57  | 0.68        |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 58  | 0.685       |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 59  | 0.69        |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 5A  | 0.695       |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 5B  | 0.7         |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 5C  | 0.705       |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 5D  | 0.71        |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 5E  | 0.715       |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 5F  | 0.72        |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 60  | 0.725       |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 61  | 0.73        |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 62  | 0.735       |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 63  | 0.74        |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 64  | 0.745       |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 65  | 0.75        |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 66  | 0.755       |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 67  | 0.76        |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 68  | 0.765       |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 69  | 0.77        |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 6A  | 0.775       |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 6B  | 0.78        |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 6C  | 0.785       |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 6D  | 0.79        |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 6E  | 0.795       |

10

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 6F  | 0.8         |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 70  | 0.805       |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 71  | 0.81        |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 72  | 0.815       |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 73  | 0.82        |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 74  | 0.825       |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 75  | 0.83        |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 76  | 0.835       |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 77  | 0.84        |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 78  | 0.845       |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 79  | 0.85        |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 7A  | 0.855       |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 7B  | 0.86        |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 7C  | 0.865       |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 7D  | 0.87        |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 7E  | 0.875       |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 7F  | 0.88        |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 80  | 0.885       |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 81  | 0.89        |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 82  | 0.895       |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 83  | 0.9         |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 84  | 0.905       |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 85  | 0.91        |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 86  | 0.915       |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 87  | 0.92        |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 88  | 0.925       |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 89  | 0.93        |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 8A  | 0.935       |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 8B  | 0.94        |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 8C  | 0.945       |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 8D  | 0.95        |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 8E  | 0.955       |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 8F  | 0.96        |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 90  | 0.965       |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 91  | 0.97        |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 92  | 0.975       |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 93  | 0.98        |

Copyright ©2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 94  | 0.985       |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 95  | 0.99        |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 96  | 0.995       |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 97  | 1           |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 98  | 1.005       |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 99  | 1.01        |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 9A  | 1.015       |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 9B  | 1.02        |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 9C  | 1.025       |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 9D  | 1.03        |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 9E  | 1.035       |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 9F  | 1.04        |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | A0  | 1.045       |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | A1  | 1.05        |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | A2  | 1.055       |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | A3  | 1.06        |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | A4  | 1.065       |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | A5  | 1.07        |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | A6  | 1.075       |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | A7  | 1.08        |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | A8  | 1.085       |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | A9  | 1.09        |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | AA  | 1.095       |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | AB  | 1.1         |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | AC  | 1.105       |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | AD  | 1.11        |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | AE  | 1.115       |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | AF  | 1.12        |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | В0  | 1.125       |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | B1  | 1.13        |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | B2  | 1.135       |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | В3  | 1.14        |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | B4  | 1.145       |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | B5  | 1.15        |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | В6  | 1.155       |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | В7  | 1.16        |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | В8  | 1.165       |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | В9  | 1.17        |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | BA  | 1.175       |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | BB  | 1.18        |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | ВС  | 1.185       |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | BD  | 1.19        |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | BE  | 1.195       |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | BF  | 1.2         |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | C0  | 1.205       |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | C1  | 1.21        |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | C2  | 1.215       |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | C3  | 1.22        |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | C4  | 1.225       |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | C5  | 1.23        |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | C6  | 1.235       |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | C7  | 1.24        |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | C8  | 1.245       |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | C9  | 1.25        |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | CA  | 1.255       |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | СВ  | 1.26        |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | CC  | 1.265       |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | CD  | 1.27        |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | CE  | 1.275       |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | CF  | 1.28        |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | D0  | 1.285       |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | D1  | 1.29        |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | D2  | 1.295       |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | D3  | 1.3         |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | D4  | 1.305       |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | D5  | 1.31        |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | D6  | 1.315       |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | D7  | 1.32        |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | D8  | 1.325       |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | D9  | 1.33        |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | DA  | 1.335       |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | DB  | 1.34        |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | DC  | 1.345       |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | DD  | 1.35        |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | HEX | Voltage (V) |

|------|------|------|------|------|------|------|------|-----|-------------|

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | DE  | 1.355       |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | DF  | 1.36        |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | E0  | 1.365       |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | E1  | 1.37        |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | E2  | 1.375       |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | E3  | 1.38        |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | E4  | 1.385       |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | E5  | 1.39        |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | E6  | 1.395       |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | E7  | 1.4         |

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | E8  | 1.405       |

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | E9  | 1.41        |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | EA  | 1.415       |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | EB  | 1.42        |

| 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | EC  | 1.425       |

| 1    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | ED  | 1.43        |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | EE  | 1.435       |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | EF  | 1.44        |

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | F0  | 1.445       |

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | F1  | 1.45        |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | F2  | 1.455       |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | F3  | 1.46        |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | F4  | 1.465       |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | F5  | 1.47        |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | F6  | 1.475       |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | F7  | 1.48        |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | F8  | 1.485       |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | F9  | 1.49        |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | FA  | 1.495       |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | FB  | 1.5         |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | FC  | 1.505       |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | FD  | 1.51        |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | FE  | 1.515       |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | FF  | 1.52        |

| <b>Absolute</b> | Maximum | Ratings | (Note 1) |

|-----------------|---------|---------|----------|

|-----------------|---------|---------|----------|

| • VCC to GND                                                                |                                             |

|-----------------------------------------------------------------------------|---------------------------------------------|

| • RGND to GND                                                               |                                             |

| • VIN to GND                                                                |                                             |

| • PVCC to GND                                                               |                                             |

| BOOT to PHASE                                                               | –0.3V to 6.5V                               |

| PHASE to GND                                                                |                                             |

| DC                                                                          | –0.3V to 30V                                |

| <20ns                                                                       | –10V to 35V                                 |

| LGATE to GND                                                                |                                             |

| DC                                                                          | 0.3V to (VCC+ 0.3V)                         |

| <20ns                                                                       | –2V to (VCC+ 0.3V)                          |

| UGATE to GND                                                                |                                             |

| DC                                                                          | $(V_{PHASE} - 0.3V)$ to $(V_{BOOT} + 0.3V)$ |

| <20ns                                                                       | $(V_{PHASE} - 2V)$ to $(V_{BOOT} + 0.3V)$   |

| • Other Pins                                                                |                                             |

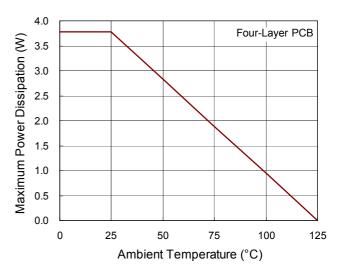

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                             |

| WQFN-52L 6x6                                                                | 3.77W                                       |

| Package Thermal Resistance (Note 2)                                         |                                             |

| WQFN-52L 6x6, $\theta_{JA}$                                                 | 26.5°C/W                                    |

| WQFN-52L 6x6, $\theta_{JC}$                                                 | 6.5°C/W                                     |

| Junction Temperature                                                        | 150°C                                       |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C                                       |

| Storage Temperature Range                                                   |                                             |

| ESD Susceptibility (Note 3)                                                 |                                             |

| HBM (Human Body Model)                                                      | 2kV                                         |

|                                                                             |                                             |

| Recommended Operating Conditions (Note 4)                                   |                                             |

| Supply Voltage, VIN                                                         | 4.5V to 24V                                 |

| Supply Voltage, VCC                                                         |                                             |

| Supply Voltage, PVCC                                                        |                                             |

| Junction Temperature Range                                                  |                                             |

| -                                                                           |                                             |

# **Electrical Characteristics**

( $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                      | Symbol               | Test Conditions                                                                      | Min          | Тур          | Max          | Unit     |  |

|--------------------------------|----------------------|--------------------------------------------------------------------------------------|--------------|--------------|--------------|----------|--|

| Supply Input                   |                      |                                                                                      |              |              |              |          |  |

| Supply Voltage                 | Vcc                  |                                                                                      | 4.5          | 5            | 5.5          | V        |  |

| Supply Current                 | Ivcc                 | V <sub>EN</sub> = 1.05V, no switching                                                |              | 9            | 15           | 5 mA     |  |

| Supply Current at PS4          | Ivcc_ps4             | V <sub>EN</sub> = 1.05V, no switching                                                |              | 0.2          | 0.25         | l MA     |  |

| Shutdown Current               | ISHDN                | V <sub>EN</sub> = 0V                                                                 |              | 10           | 20           | μА       |  |

| Driver Supply Voltage          | VPVCC                |                                                                                      | 4.5          |              | 5.5          | V        |  |

| Reference and DAC              |                      |                                                                                      |              |              |              |          |  |

|                                |                      | VDAC = 0.75V - 1.52V                                                                 | -0.5%        | 0            | 0.5%         | % of VID |  |

| DAC Accuracy                   | V <sub>FB</sub>      | VDAC = 0.5V - 0.745V                                                                 | -8           | 0            | 8            | mV       |  |

|                                |                      | VDAC = 0.25V - 0.495V                                                                | -10          | 0            | 10           |          |  |

| Slew Rate                      |                      |                                                                                      |              |              |              |          |  |

| Dunamia VID Claus Bata         | CD                   | Set VID fast                                                                         | 30           | 34           | 38           | mV/μs    |  |

| Dynamic VID Slew Rate          | SR                   | Set VID slow, set slow = 1/2 Fast                                                    | 15           | 17           | 19           |          |  |

| EA Amplifier                   |                      |                                                                                      |              |              |              |          |  |

| DC Gain                        | ADC                  | $R_L = 47k\Omega$                                                                    | 70           | 80           |              | dB       |  |

| Gain-Bandwidth Product         | GBW                  | C <sub>LOAD</sub> = 5pF                                                              |              | 5            |              | MHz      |  |

| Input Offset                   | VEAOFS               |                                                                                      | -3           |              | 3            | mV       |  |

| Slew Rate                      | SREA                 | $C_{LOAD}$ = 10pF (Gain= -4, R <sub>F</sub> = 47k $\Omega$ , $V_{OUT}$ =0.5V to -3V) |              | 5            |              | V/μs     |  |

| Output Voltage Range           | V <sub>COMP</sub>    | $R_L = 47k\Omega$                                                                    | 0.3          |              | 3.6          | V        |  |

| Max Source/Sink Current        | I <sub>OUTEA</sub>   | V <sub>COMP</sub> = 2V                                                               |              | 5            |              | mA       |  |

| <b>Current Sensing Amplifi</b> | er                   |                                                                                      |              |              |              |          |  |

| Input Offset Voltage           | Voscs                |                                                                                      | -0.4         |              | 0.4          | mV       |  |

| Impedance at Positive Input    | RISENXP              |                                                                                      | 1            |              |              | ΜΩ       |  |

| Current Mirror Gain            | Amirror              | IIMON/ISENxN                                                                         | 0.97         | 1            | 1.03         | A/A      |  |

| Input Range                    | V <sub>ISEN_IN</sub> | V <sub>DAC</sub> = 1.1V, I <sub>SENP_X</sub> - I <sub>SENN_X</sub>                   | -40          |              | 40           | mV       |  |

| TON Setting                    |                      |                                                                                      |              |              |              |          |  |

| On-Time Setting                | ton                  | V <sub>IN</sub> = 10V, V <sub>DAC</sub> = 1V, f = 400k                               | I            | 250          |              | ns       |  |

| Minimum Off-Time               | toff                 | V <sub>DAC</sub> = 1                                                                 | 1            | 180          | 300          | ns       |  |

| Protections                    |                      |                                                                                      |              |              |              |          |  |

| Under-Voltage Lockout          | V <sub>UVLO</sub>    | Falling edge                                                                         | 3.9          | 4.1          | 4.2          | V        |  |

| Threshold                      | $\Delta V_{UVLO}$    | Rising edge hysteresis                                                               | 100          | 170          | 250          | mV       |  |

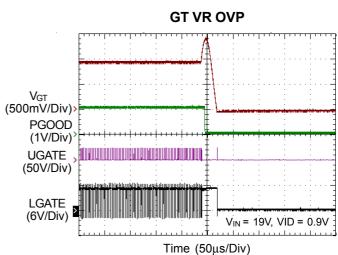

| Over-Voltage Protection        | Vov                  | Respect to VID voltage                                                               | VID +<br>300 | VID +<br>350 | VID +<br>400 | mV       |  |

| Threshold                      |                      | Lower limit to 1V                                                                    | 1300         | 1350         | 1400         | mV       |  |

Copyright ©2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                                       | Symbol               | Test Conditions                                                                     | Min              | Тур                | Max   | Unit      |  |

|-------------------------------------------------|----------------------|-------------------------------------------------------------------------------------|------------------|--------------------|-------|-----------|--|

| Under-Voltage Protection                        | .,                   | D \/ID                                                                              |                  | 250                | 000   | mV        |  |

| Threshold                                       | Vuv                  | Respect to VID voltage                                                              | <del>-4</del> 00 | -400   -350   -300 |       | mV        |  |

| Negative Voltage<br>Protection Threshold        | V <sub>NV</sub>      |                                                                                     | -100             | -50                |       | mV        |  |

| VRON and VR_READY                               |                      |                                                                                     |                  |                    |       |           |  |

| VOONT                                           | V <sub>IH</sub>      | Respect to 1V, 70%                                                                  | 0.7              |                    |       | V         |  |

| VRON Threshold                                  | V <sub>IL</sub>      | Respect to 1V, 30%                                                                  |                  |                    | 0.3   | V         |  |

| Leakage Current of VRON                         |                      |                                                                                     | -1               |                    | 1     | μА        |  |

| PGOOD Pull Low<br>Voltage                       | Vpgood               | I <sub>VR_Ready</sub> = 10mA                                                        |                  |                    | 0.13  | V         |  |

| Serial VID and VR_HOT                           |                      |                                                                                     |                  |                    |       |           |  |

|                                                 | ViH                  | Respect to INTEL Spec. with 50mV                                                    | 0.65             |                    |       | V         |  |

| VCLK, VDIO                                      | VIL                  | hysteresis                                                                          |                  |                    | 0.45  |           |  |

| Leakage Current of VCLK, VDIO, ALERT and VR HOT | I <sub>LEAK_IN</sub> |                                                                                     | -1               |                    | 1     | μΑ        |  |

| VDIO, ALERT and                                 |                      | I <sub>VDIO</sub> = 10mA                                                            |                  |                    |       | V         |  |

| VR HOT Pull Low                                 |                      | I <sub>ALERT</sub> = 10mA                                                           |                  |                    | 0.13  |           |  |

| Voltage                                         |                      | I <sub>VR</sub> HOT = 10mA                                                          |                  |                    |       |           |  |

| VREF                                            |                      | new.                                                                                |                  |                    |       |           |  |

| VREF06                                          | VREF                 |                                                                                     | 0.595            | 0.6                | 0.605 | V         |  |

| ADC                                             | 1                    |                                                                                     |                  |                    |       |           |  |

|                                                 | VIMON                | V <sub>IMON</sub> – V <sub>IMON_INI</sub> = 0.8V,<br>MAIN rail, 2 phase application |                  | 255                |       | — Decimal |  |

| Digital IMON Set                                |                      | V <sub>IMON</sub> - V <sub>IMON_INI</sub> = 0.4V, single phase application          |                  | 255                |       |           |  |

| Update Period                                   | t <sub>IMON</sub>    |                                                                                     |                  | 125                |       | μS        |  |

| TSEN Threshold for<br>Tmp_Zone[7] Transition    |                      | 100°C                                                                               |                  | 1.092              |       |           |  |

| TSEN Threshold for<br>Tmp_Zone[6] Transition    |                      | 97°C                                                                                |                  | 1.132              |       |           |  |

| TSEN Threshold for<br>Tmp_Zone[5] Transition    |                      | 94°C                                                                                |                  | 1.176              |       |           |  |

| TSEN Threshold for<br>Tmp_Zone[4] Transition    |                      | 91°C                                                                                |                  | 1.226              |       | .,        |  |

| TSEN Threshold for<br>Tmp_Zone[3] Transition    | VTSEN                | 88°C                                                                                |                  | 1.283              |       | V         |  |

| TSEN Threshold for Tmp_Zone[2] Transition       |                      | 85°C                                                                                |                  | 1.346              |       |           |  |

| TSEN Threshold for Tmp_Zone[1] Transition       |                      | 82°C                                                                                |                  | 1.418              |       |           |  |

| TSEN Threshold for Tmp_Zone[0] Transition       |                      | 75°C                                                                                |                  | 1.624              |       |           |  |

| Update Period                                   | t <sub>TSEN</sub>    |                                                                                     |                  | 100                |       | 1         |  |

| Parameter           | Symbol                | Test Conditions                                                             | Min  | Тур | Max  | Unit |  |  |

|---------------------|-----------------------|-----------------------------------------------------------------------------|------|-----|------|------|--|--|

| Switching Timing    |                       |                                                                             |      |     |      |      |  |  |

| UGATEx Rising Time  | tugater               | 3nF load                                                                    |      | 8   |      | ns   |  |  |

| UGATEx Falling Time | tugatef               | 3nF load                                                                    |      | 8   |      | ns   |  |  |

| LGATEx Rising Time  | tLGATEr               | 3nF load                                                                    |      | 8   |      | ns   |  |  |

| LGATEx Falling Time | tLGATEf               | 3nF load                                                                    |      | 4   |      | ns   |  |  |

|                     | tUGATEpgh             | Output unloaded                                                             |      | 20  |      | - ns |  |  |

| Propagation Dolay   | tUGATEpdl             | Output unloaded                                                             |      | 35  |      |      |  |  |

| Propagation Delay   | t <sub>LGATEpdh</sub> | Output unloaded                                                             |      | 20  |      |      |  |  |

|                     | t <sub>LGATEpdl</sub> | Output unloaded                                                             |      | 35  |      |      |  |  |

| Output              |                       |                                                                             |      |     |      |      |  |  |

| UGATEx Drive Source | Rugatesr              | V <sub>BOOT</sub> – V <sub>PHASE</sub> = 5V,<br>I <sub>Source</sub> = 100mA |      | 1   |      | Ω    |  |  |

| UGATEx Drive Sink   | RUGATEsk              | V <sub>BOOT</sub> – V <sub>PHASE</sub> = 5V,<br>I <sub>Sink</sub> = 100mA   |      | 1   |      | Ω    |  |  |

| LGATEx Drive Source | RLGATEsr              | I <sub>Source</sub> = 100mA                                                 |      | 1   |      | Ω    |  |  |

| LGATEx Drive Sink   | RLGATEsk              | I <sub>Sink</sub> = 100mA                                                   |      | 0.5 |      | Ω    |  |  |

| ITSEN               |                       |                                                                             |      |     |      |      |  |  |

| TSEN Source Current | I <sub>TSEN</sub>     | V <sub>TSEN</sub> = 1.6V                                                    | 79.2 | 80  | 80.8 | μΑ   |  |  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A$  = 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# **Typical Application Circuit**

#### For MAIN Two Phase Application

#### For MAIN Single Phase Application

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

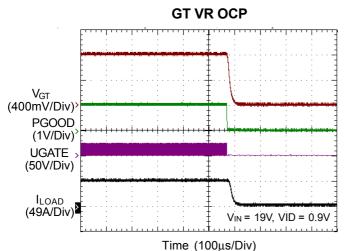

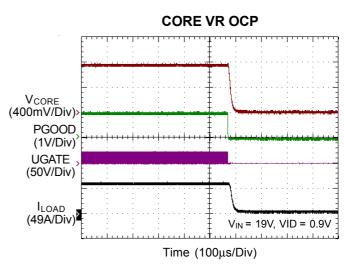

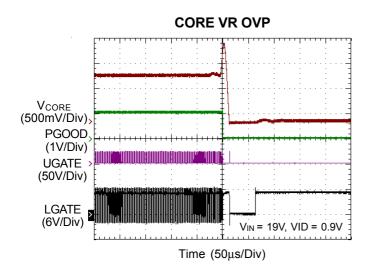

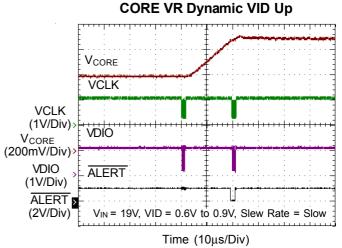

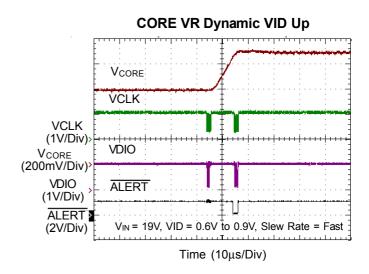

# **Typical Operating Characteristics**

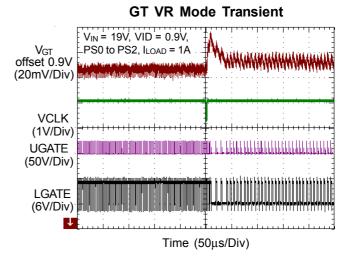

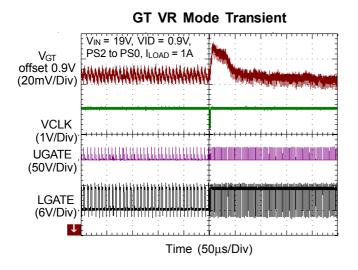

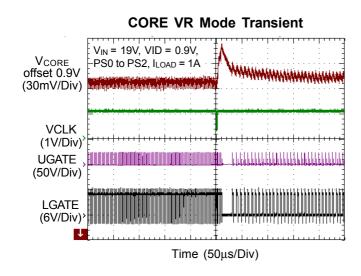

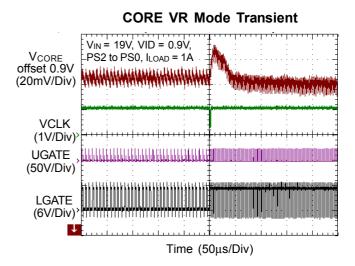

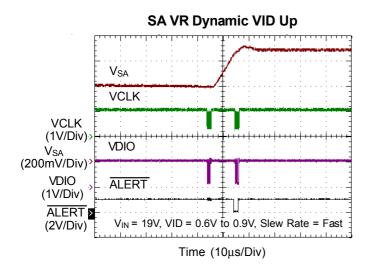

# VCLK (1V/Div) VCORE (200mV/Div) VDIO (1V/Div) ALERT (2V/Div) VIN = 19V, VID = 0.9V to 0.6V, Slew Rate = Slow Time (10µs/Div)

# **Applications information**

The RT3602AC includes three voltage rails: a 2/1 phase synchronous Buck controller, the MAIN VR, a single multiphase synchronous Buck controller, the auxiliary VR, and a single phase synchronous Buck controller, the VCCSA VR, designed to meet Intel IMVP8 compatible CPUs specification with a serial SVID control interface. The controller uses an ADC to implement all kinds of settings to save total pin number for easy use and increasing PCB space utilization. The RT3602AC is used in notebooks, desktop computers and servers.

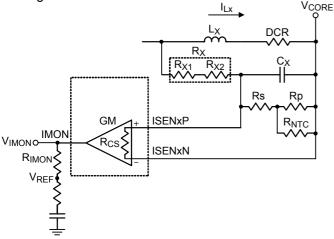

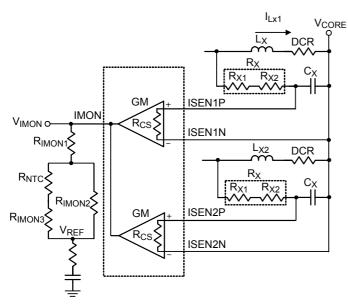

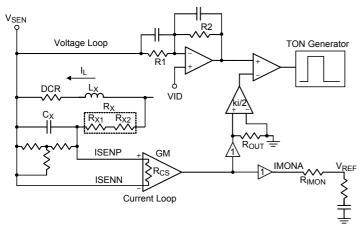

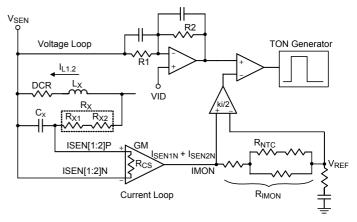

#### **General loop Function**

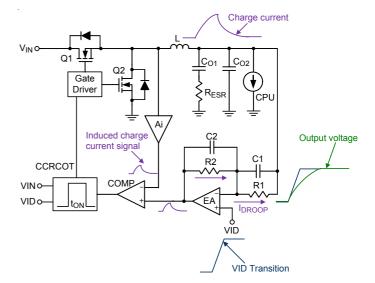

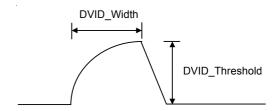

#### G-NAVP<sup>TM</sup> Control Mode

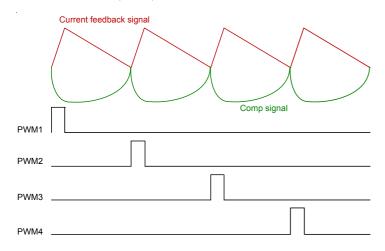

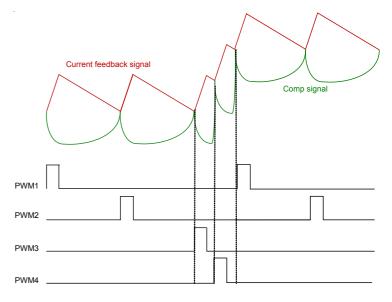

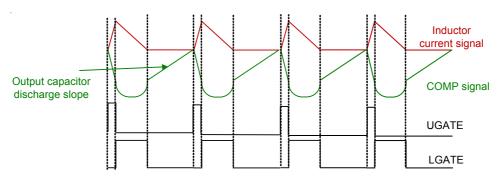

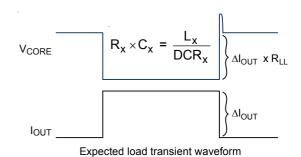

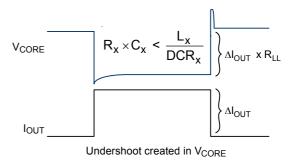

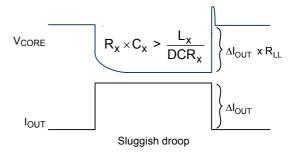

The RT3602AC adopts the G-NAVP<sup>TM</sup> controller, which is a current mode constant on-time control with DC offset cancellation. The approach can not only improve DC offset problem for increasing system accuracy but also provide fast transient response. When current feedback signal reaches comp signal, the RT3602AC generates an on-time width to achieve PWM modulation. Figure 1 shows the basic G-NAVP<sup>TM</sup> behavior waveforms in continuous conduct mode (CCM).

Figure 1 (a). G-NAVP<sup>™</sup> Behavior Waveforms in CCM in Steady State

Figure 1 (b). G-NAVP<sup>TM</sup> Behavior Waveforms in CCM in Load Transient.

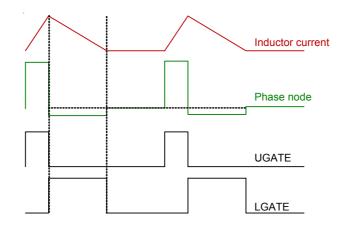

#### **Diode Emulation Mode (DEM)**

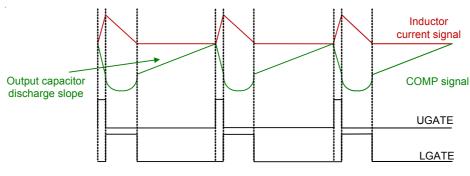

As well-known, the dominate power loss is switching related loss during light load, hence VR needs to be operated in asynchronous mode (or called discontinuous conduct mode, DCM) to reduce switching related loss since switching frequency is dependent on loading in the asynchronous mode. The RT3602AC can operate in diode emulation mode (DEM) to improve light load efficiency. In DEM operation, the behavior of low-side MOSFET(s) needs to work like a diode, that is, the low-side MOSFET(s) will be turned on when the phase voltage is a negative value, i.e. the inductor current follows from Source to Drain of low-side MOSFET(s). And the low-side MOSFET(s) will be turned off when phase voltage is a positive value, i.e. reversed current is not allowed. Figure 2 shows the control behavior in DEM. Figure 3 shows the G-NAVP<sup>TM</sup> operation in DEM to illustrate the control behaviors. When the load decreases, the discharge time of output capacitors increases during UGATE and LGATE are turned off. Hence, the switching frequency and switching loss will be reduced to improve efficiency in light load condition.

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Figure 2. Diode Emulation Mode (DEM) in Steady State

Figure 3. (a)

Figure 3. (b)

$\label{eq:figure 3.G-NAVP} \textbf{Figure 3. G-NAVP}^{\text{TM}} \ \textbf{Operation in DEM. (a): The load is lighter, output capacitor discharge slope is smaller and the } \\$ switching frequency is lower. (b): The load is increasing, output capacitor discharge slope is increased and switching frequency is increased, too.

#### **Phase Interleaving Function**

The RT3602AC is a multi-output controller, the MAIN rail of the RT3602AC has a phase interleaving function, 180 degree phase shift for 2-phase operation which can help reduce output voltage ripple and EMI problem.

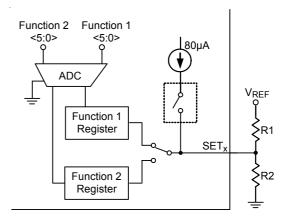

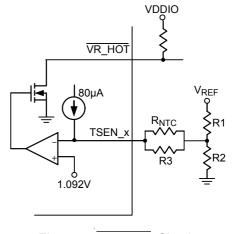

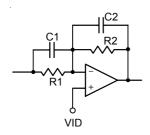

#### **Multi-Function Pin Setting Mechanism**

For reducing total pin number of package, SET [1:3], TSEN\_Main and TSEN\_AUXI pins adopt the multi-function pin setting mechanism in the RT3602AC. Figure 4 illustrates this operating mechanism for SET [1:3]. The voltage at VREF pin will be pulled up to 3.2V after power ready (POR). First, external voltage divider is used to set the Function1, and then internal current source  $80\mu A$  is used to set the Function2. The setting voltage of Function1 and Function2 can be represented as

$$V_{Function1} = \frac{R2}{R1 + R2} \times 3.2V$$

$$V_{Function2} = 80 \mu A \times \frac{R1 \times R2}{R1 + R2}$$

All function setting will be done within  $500\mu s$  after power ready (POR), and the voltage at VREF pin will be fixed to 0.6V after all function setting over.

If  $V_{\text{Function1}}$  and  $V_{\text{Function2}}$  are determined, R1 and R2 can be calculated as follows :

$$R1 = \frac{3.2V \times V_{Function2}}{80\mu\text{A} \times V_{Function1}}$$

$$R2 = \frac{R1 \times V_{Function1}}{3.2V - V_{Function1}}$$

Figure 4. Multi-Function Pin Setting Mechanism for SET [1:3]

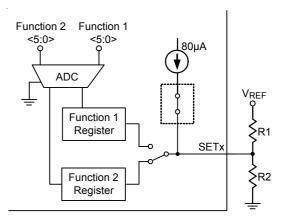

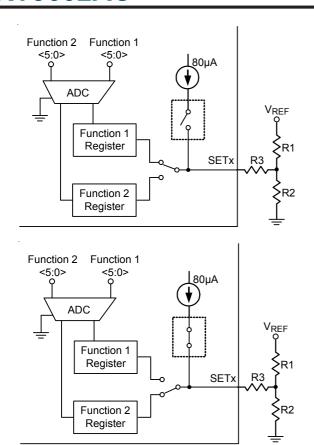

Connecting a R3 resistor from SETx pin or SETAx pin to the middle node of voltage divider can help to fine tune the set voltage of Function 2, which does not affect the set voltage of Function1. The Figure 5 shows the setting method and the set voltage of Function 1 and Function2 can be represented as:

$$V_{Function1} = \frac{R2}{R1 + R2} \times 3.2V$$

$$V_{Function2} = 80 \mu A \times \left(R3 + \frac{R1 \times R2}{R1 + R2}\right)$$

Figure 5. Multi-Function Pin Setting Mechanism with a R3 Resistor to Fine Tune the Set Voltage of Function2

Figure 6 shows operating mechanism for TSEN\_Main and TSEN\_AUXI pins. There is only voltage divider Function to program VR. The internal current source is used to thermal sensing. The Function for program VR can be represented as

$$V_{Function1} = \frac{R2}{R1 + R2} \times 3.2V$$

$$\begin{array}{c} Function \\ <5:0> \\ \hline \\ ADC \\ \hline \\ ICCMAX \\ Setting \\ Register \\ \hline \\ Thermal \\ Sense \\ \end{array}$$

$$\begin{array}{c} V_{REF} \\ \hline \\ R3 \\ \hline \\ R2 \\ \hline \end{array}$$

Figure 6. Multi-Function Pin Setting Mechanism for TSEN\_MAIN and TSEN\_AUXI

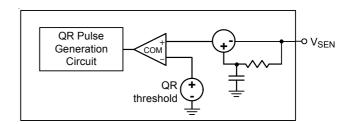

By the way, Function1 of SET1 and SET2 pins are used to program QR threshold and QR width for MAIN and AUXI rails, respectively. Function1 of SET3 pin is used to setting force-non-zero VBOOT, SA rail TON factor, and SA rail DVID threshold. Function2 of SET1 and SET2 pins are used to program TON factor, Ki gain and anti-overshoot functions for MAIN and AUXI rails. Function2 of SET3 can be setting DVID threshold for MAIN and AUXI rails. TSEN\_AUXI pin is used to set ICCMAX and zero load-line for SA rail. TSEN\_MAIN is used to program ICCMAX of AUXI and SA rails. In addition, Richtek provide a Microsoft Excel-based spreadsheet to help design SETx, TSEN\_Main and TSEN\_AUXI resistor network.

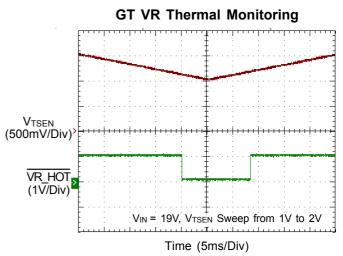

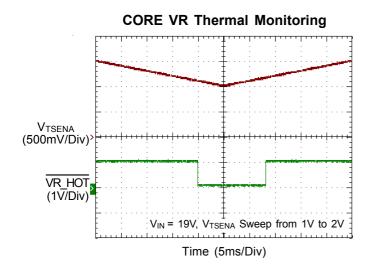

### TSEN\_Main, TSEN\_AUXI and VR\_HOT

The  $\overline{VR}$ \_HOT signal is an open-drain signal which is used for VR thermal protection. When the sensed voltage in each TSEN pin is less than 1.092, the  $\overline{VR}$ \_HOT signal will be pulled-low to notify CPU that the thermal protection needs to work. According to Intel VR definition,  $\overline{VR}$ \_HOT signal needs acting if VR power chain temperature exceeds 100°C. Placing an NTC thermistor at the hottest area in the VR power chain and its connection is shown in Figure 7, to design the TSEN network so that  $V_{TSEN}$  = 1.092V at 100°C. The resistance accuracy of TSEN network is recommended to be 1% or higher.

$$V_{TSEN_X} = 80 \mu A \times [(R_{NTC} //R3) + (R1 //R2)]$$

Figure 7. VR HOT Circuit

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

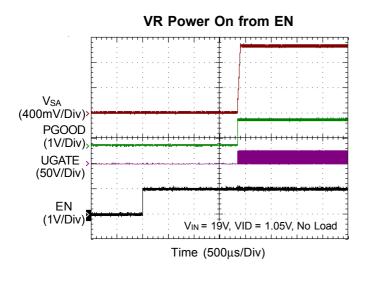

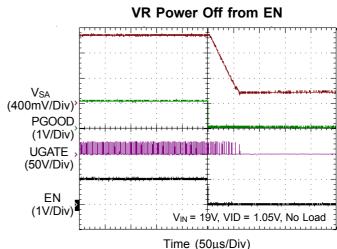

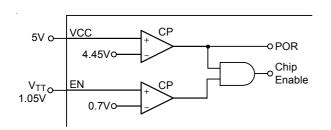

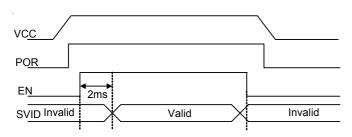

#### Power Ready (POR) Detection

During start-up, the RT3602AC detects the voltage at the voltage input pins:  $V_{CC}$  and EN. When  $V_{CC}>4.45$ V, the RT3602AC recognizes the power state of system to be ready (POR = high) and waits for enable command at the EN pin. After POR = high and  $V_{EN}>0.7$ V, the RT3602AC enters start-up sequence. If  $V_{CC}$  drops below low threshold (POR = low), the RT3602AC enters power down sequence and all functions will be disabled. Normally, connecting system voltage  $V_{TT}$  (1.05V) to the EN pin is recommended. 2ms (max) after the chip has been enabled, the SVID circuitry will be ready. All the protection latches (OVP, OCP, UVP) will be cleared only by  $V_{CC}$ . The condition of VEN = low will not clear these latches. Figure 8 and Figure 9 show the POR detection and the timing chart for POR process, respectively.

#### **Under-Voltage Lockout (UVLO)**

During normal operation, if the voltage at the VCC pin drops below POR threshold 4.14V (min), the VR triggers UVLO. The UVLO protection forces all high-side MOSFETs and low-side MOSFETs off by shutting down internal PWM logic drivers.

Figure 8. POR Detection

Figure 9. Timing Chart for POR Process

#### Phase Disable (Before POR)

The number of active phases is determined by the internal circuitry that monitors the ISENxN voltages during startup. Normally, the MAIN rail operates as a 2-phase PWM controller. Pulling ISEN2N to VCC programs a 1-phase operation. Before POR, VR detects whether the voltage of ISEN2N is higher than "VCC – 1V" to decide how many phases should be active. Phase selection is only active during POR. When POR = high, the number of active phases is determined and latched. The unused ISENxP pins are recommended to be connected to VCC and unused PWM pins can be left floating.

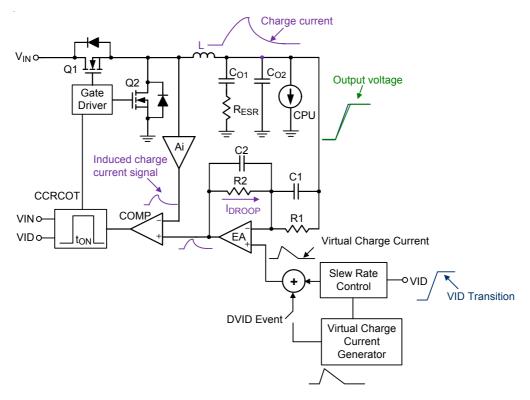

#### **Switching Frequency Setting**

The RT3602AC is one kind of constant on-time control. The patented CCRCOT (Constant Current Ripple COT) technology can generate an adaptive on-time with input voltage and VID code to obtain a constant current ripple, so that the output voltage ripple can be controlled nearly like a constant as different input and output voltages change.

The Ton equation can be classified as below two regions.

$$\begin{split} &V_{DAC} \geq 0.9 \\ &T_{ON} = \frac{1.2 \mu \times V_{DAC}}{k_{TON} \times (V_{IN} - V_{DAC})} + 15n \end{split}$$

$$V_{DAC} < 0.9$$

$$T_{ON} = \frac{1.08 \mu}{k_{TON} \times (V_{IN} - V_{DAC})} + 15n$$

where  $k_{TON}$  is a coefficient which can be selected by SET[1 to 3] pins for each VR rail. Table 3 and Table 6 show the  $k_{TON}$  coefficient and ki gain setting for each VR rail on the SET[1 to 3] pins.

Table 2. SET[1 to 2] Pins Setting for QR\_TH and QRWIDTH

|          | $SET[1to 2]_V = V_{REF} \times \frac{R1 \times R2}{R1 + R2}$ |          |      | QRTH_X<br>(mV) | QRWIDTH_X<br>(% of On-Time) |

|----------|--------------------------------------------------------------|----------|------|----------------|-----------------------------|

| Min      | Тур                                                          | Max      | Unit |                |                             |

| 24.77419 | 25.02444                                                     | 25.27468 | mV   |                | 160%                        |

| 74.32258 | 75.07331                                                     | 75.82405 | mV   | Disable        | 130%                        |

| 123.871  | 125.1222                                                     | 126.3734 | mV   |                | 100%                        |

| 173.4194 | 175.1711                                                     | 176.9228 | mV   |                | 70%                         |

| 222.9677 | 225.2199                                                     | 227.4721 | mV   |                | 160%                        |

| 272.5161 | 275.2688                                                     | 278.0215 | mV   | 10             | 130%                        |

| 322.0645 | 325.3177                                                     | 328.5709 | mV   |                | 100%                        |

| 371.6129 | 375.3666                                                     | 379.1202 | mV   |                | 70%                         |

| 421.1613 | 425.4154                                                     | 429.6696 | mV   |                | 160%                        |

| 470.7097 | 475.4643                                                     | 480.219  | mV   | 15             | 130%                        |

| 520.2581 | 525.5132                                                     | 530.7683 | mV   | 15             | 100%                        |

| 569.8065 | 575.5621                                                     | 581.3177 | mV   |                | 70%                         |

| 619.3548 | 625.6109                                                     | 631.8671 | mV   |                | 160%                        |

| 668.9032 | 675.6598                                                     | 682.4164 | mV   | 20             | 130%                        |

| 718.4516 | 725.7087                                                     | 732.9658 | mV   | 20             | 100%                        |

| 768      | 775.7576                                                     | 783.5152 | mV   |                | 70%                         |

| 817.5484 | 825.8065                                                     | 834.0645 | mV   |                | 160%                        |

| 867.0968 | 875.8553                                                     | 884.6139 | mV   | 25             | 130%                        |

| 916.6452 | 925.9042                                                     | 935.1632 | mV   | 25             | 100%                        |

| 966.1935 | 975.9531                                                     | 985.7126 | mV   | 1 -            | 70%                         |

| 1015.742 | 1026.002                                                     | 1036.262 | mV   |                | 160%                        |