# 4/3/2/1 Phase Buck Controller with PWM\_VID and I<sup>2</sup>C Interface

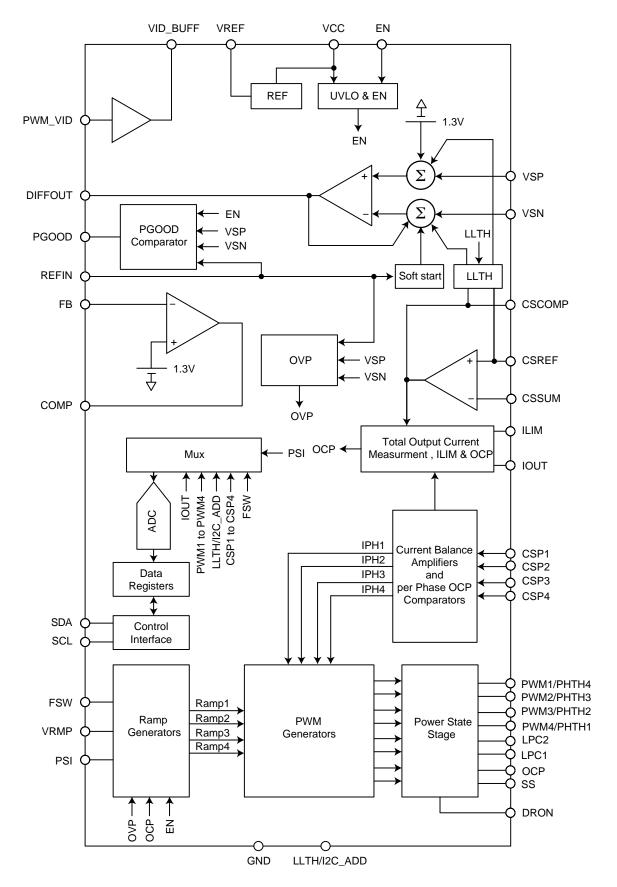

The NCP81276 is a multiphase synchronous controller optimized for new generation computing and graphics processors. The device is capable of driving up to 4 phases and incorporates differential voltage and phase current sensing, adaptive voltage positioning and PWM\_VID interface to provide and accurately regulated power for computer or graphic controllers. The integrated power saving interface (PSI) allows for the processors to set the controller in one of three modes, i.e. all phases on, dynamic phases shedding or fixed low phase count mode, to obtain high efficiency in light-load conditions. The dual edge PWM multiphase architecture ensures fast transient response and good dynamic current balance.

# Features

- Compliant with NVIDIA<sup>®</sup> OVR4+ Specifications

- Supports Up to 4 Phases

- 4.5 V to 20 V Supply Voltage Range

- 250 kHz to 1.2 MHz Switching Frequency (4 Phase)

- Power Good Output

- Under Voltage Protection (UVP)

- Over Voltage Protection (OVP)

- Over Current Protection (OCP)

- Per Phase Over Current Protection

- Startup into Pre-Charged Loads while Avoiding False OVP

- Configurable Adaptive Voltage Positioning (AVP)

- High Performance Operational Error Amplifier

- True Differential Current Balancing Sense Amplifiers for Each Phase

- Phase-to-Phase Dynamic Current Balancing

- Current Mode Dual Edge Modulation for Fast Initial Response to Transient Loading

- Power Saving Interface (PSI)

- Automatic Phase Shedding with User Settable Thresholds

- PWM\_VID and I<sup>2</sup>C Control Interface

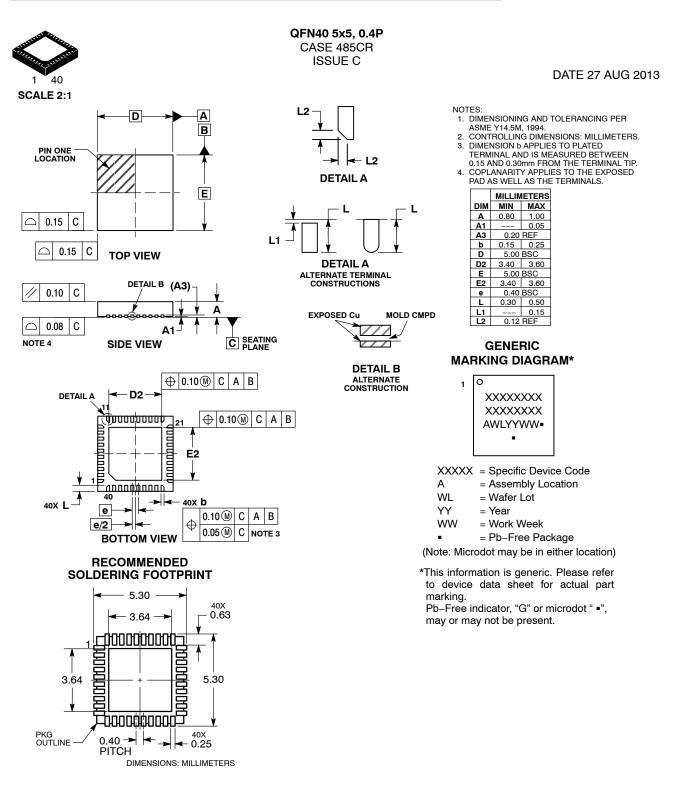

- Compact 40 Pin QFN Package (5 × 5 mm Body, 0.4 mm Pitch)

- This Device is Pb-Free and is RoHS Compliant

# **Typical Applications**

- GPU and CPU Power

- Graphic Cards

- Desktop and Notebook Applications

# **ON Semiconductor®**

www.onsemi.com

CASE 485CR

# MARKING DIAGRAM

# ORDERING INFORMATION

| [ | Device        | Package            | Shipping <sup>†</sup> |

|---|---------------|--------------------|-----------------------|

|   | NCP81276MNTXG | QFN40<br>(Pb-Free) | 5000/Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, <u>BRD8011/D</u>.

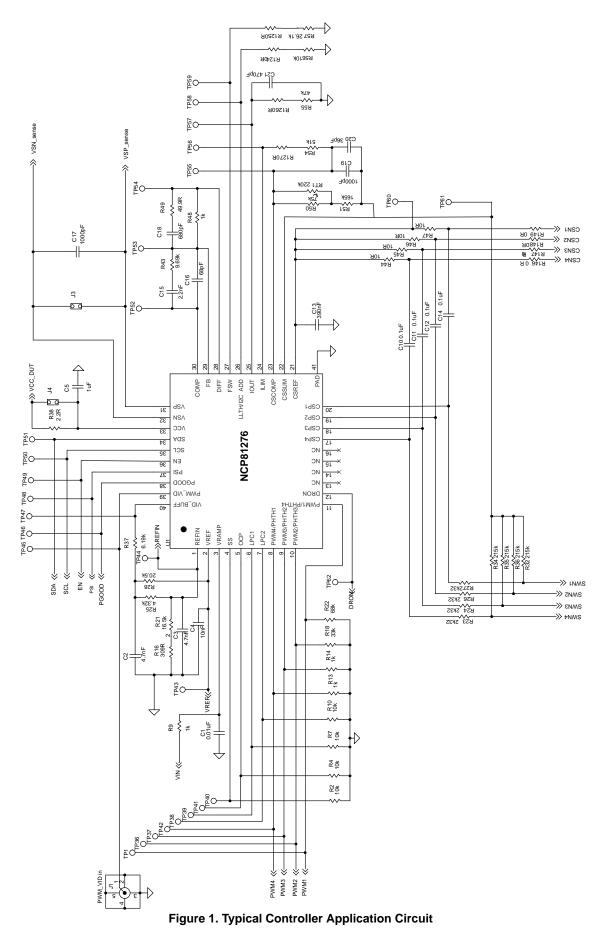

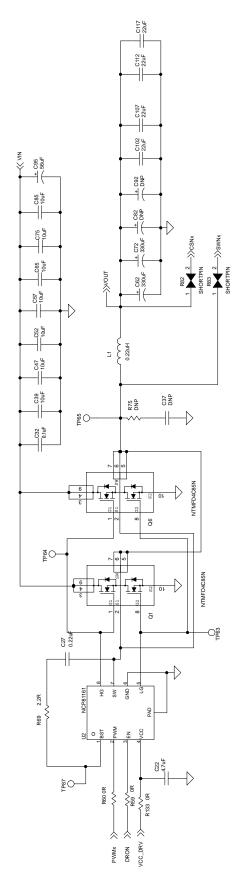

Figure 2. Typical Phase Application Circuit

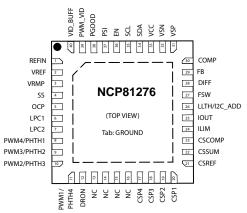

# Table 1. PIN FUNCTION DESCRIPTION

| Pin<br>Number | Pin<br>Name  | Pin<br>Type | Description                                                                                                                                                    |

|---------------|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | REFIN        | I           | Reference voltage input for output voltage regulation.                                                                                                         |

| 2             | VREF         | 0           | 2.0 V output reference voltage. A 10 nF ceramic capacitor is required to connect this pin to ground.                                                           |

| 3             | VRMP         | I           | Feed-forward input of VIN for the ramp slope compensation. The current fed into this pin is used to control of the ramp of PWM slope.                          |

| 4             | SS           | I/O         | Soft Start setting. During startup it is used to program the soft start time with a resistor to ground.                                                        |

| 5             | OCP          | I/O         | Per OCP setting. During startup it is used to program the OCP level per phase and latch off time with a resistor to ground.                                    |

| 6             | LPC1         | I/O         | Low phase count 1. During startup it is used to program the power zone (when PSI is set low) with a resistor to ground.                                        |

| 7             | LPC2         | I/O         | Low phase count 2. During startup it is used to program boot-up power zone (when PSI is set low) with a resistor to ground.                                    |

| 8             | PWM4/PHTH1   | I/O         | PWM 4 output/Phase Shedding Threshold 1. During startup it is used to program the phase shedding threshold 1 (PSI set to mid state) with a resistor to ground. |

| 9             | PWM3/PHTH2   | I/O         | PWM 3 output/Phase Shedding Threshold 2. During startup it is used to program the phase shedding threshold 2 (PSI set to mid state) with a resistor to ground. |

| 10            | PWM2/PHTH3   | I/O         | PWM 2 output/Phase Shedding Threshold 3. During startup it is used to program the phase shedding threshold 3 (PSI set to mid state) with a resistor to ground. |

| 11            | PWM1/PHTH4   | I/O         | PWM 1 output/Phase Shedding Threshold 4. During startup it is used to program the phase shedding threshold 4 (PSI set to mid state) with a resistor to ground. |

| 12            | DRON         | I/O         | Bidirectional gate driver enable for external drivers.                                                                                                         |

| 13            | NC           | N/A         | No connect pin. Please leave floating.                                                                                                                         |

| 14            | NC           | N/A         | No connect pin. Please leave floating.                                                                                                                         |

| 15            | NC           | N/A         | No connect pin. Please leave floating.                                                                                                                         |

| 16            | NC           | N/A         | No connect pin. Please leave floating.                                                                                                                         |

| 17            | CSP4         | I           | Non-inverting input to current balance sense amplifier for phase 4. Pull-up to VCC to disable the PWM4 output.                                                 |

| 18            | CSP3         | I           | Non-inverting input to current balance sense amplifier for phase 3. Pull-up to VCC to disable the PWM3 output.                                                 |

| 19            | CSP2         | I           | Non-inverting input to current balance sense amplifier for phase 2. Pull-up to VCC to disable the PWM2 output.                                                 |

| 20            | CSP1         | I           | Non-inverting input to current balance sense amplifier for phase 1. Pull-up to VCC to disable the PWM1 output.                                                 |

| 21            | CSREF        | I           | Total output current sense amplifier reference voltage input.                                                                                                  |

| 22            | CSSUM        | I           | Inverting input of total current sense amplifier.                                                                                                              |

| 23            | CSCOMP       | 0           | Output of total current sense amplifier.                                                                                                                       |

| 24            | ILIM         | 0           | Over current shutdown threshold setting output. The threshold is set by a resistor between ILIM and to CSCOMP pins.                                            |

| 25            | IOUT         | 0           | Total output current. A resistor to GND is required to provide a voltage drop of 2 V at the maximum output current.                                            |

| 26            | LLTH/I2C_ADD | I           | Load line selection from 0% to 100% and I <sup>2</sup> C address pin.                                                                                          |

| 27            | FSW          | I           | Resistor to ground form this pin sets the operating frequency of the regulator.                                                                                |

| 28            | DIFF         | 0           | Output of the regulators differential remote sense amplifier.                                                                                                  |

| 29            | FB           | I           | Error amplifier inverting (feedback) input.                                                                                                                    |

| 30            | COMP         | 0           | Output of the error amplifier and the inverting input of the PWM comparator.                                                                                   |

| 31            | VSP          |             | Differential Output Voltage Sense Positive terminal.                                                                                                           |

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Description                                                                                                                 |

|---------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| 32            | VSN         | I           | Differential Output Voltage Sense Negative terminal.                                                                        |

| 33            | VCC         | I           | Power for the internal control circuits. A 1 $\mu\text{F}$ decoupling capacitor is requires from this pin to ground.        |

| 34            | SDA         | I/O         | Serial Data bi-directional pin, requires pull-up resistor to VCC.                                                           |

| 35            | SCL         | I           | Serial Bus clock signal, requires pull-up resistor to VCC.                                                                  |

| 36            | EN          | I           | Logic input. Logic high enables regulator output logic low disables regulator output.                                       |

| 37            | PSI         | I           | Power level control 3 level control. Use a current limiting resistor of 100 k $\Omega$ when driving the pin with 5 V logic. |

| 38            | PGOOD       | 0           | Open Drain power good indicator.                                                                                            |

| 39            | PWM_VID     | I           | PWM_VID buffer input.                                                                                                       |

| 40            | VID_BUFF    | 0           | PWM_VID pulse output from internal buffer.                                                                                  |

| 41            | AGND        | GND         | Analog ground and thermal pad, connected to system ground.                                                                  |

# Table 1. PIN FUNCTION DESCRIPTION (continued)

# **Table 2. MAXIMUM RATINGS**

| Rating                                                                            | Pin Symbol                                                 | Min                   | Тур | Max       | Unit |

|-----------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|-----|-----------|------|

| Pin Voltage Range (Note 1)                                                        | VSN                                                        | GND-0.3               |     | GND + 0.3 | V    |

|                                                                                   | VCC                                                        | -0.3                  |     | 6.5       | V    |

|                                                                                   | VRMP                                                       | -0.3                  |     | 25        | V    |

|                                                                                   | PWM_VID                                                    | _0.3<br>(−2, < 50 ns) |     | VCC + 0.3 | V    |

|                                                                                   | All Other Pins<br>with the<br>exception of<br>the DRON Pin | -0.3                  |     | VCC + 0.3 | V    |

| Pin Current Range                                                                 | COMP                                                       | -2                    |     | 2         | mA   |

|                                                                                   | CSCOMP                                                     |                       |     |           |      |

|                                                                                   | DIFF                                                       |                       |     |           |      |

|                                                                                   | PGOOD                                                      |                       |     |           |      |

|                                                                                   | VSN                                                        | -1                    |     | 1         | mA   |

| Moisture Sensitivity Level                                                        | MSL                                                        |                       | 1   |           | -    |

| Lead Temperature Soldering Reflow (SMD Styles Only),<br>Pb-Free Versions (Note 2) | T <sub>SLD</sub>                                           |                       | 260 |           | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All signals referenced to GND unless noted otherwise.

2. For information, please refer to our Soldering and Mounting Techniques Reference Manual, <u>SOLDERRM/D</u>.

# **Table 3. THERMAL CHARACTERISTICS**

| Rating                                                                                     | Symbol           | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Thermal Characteristics, (QFN40, 5 × 5 mm)<br>Thermal Resistance, Junction-to-Air (Note 1) | R <sub>θJA</sub> | _   | 68  | -   | °C/W |

| Operating Junction Temperature Range (Note 2)                                              | TJ               | -40 | -   | 150 | °C   |

| Operating Ambient Temperature Range                                                        | T <sub>A</sub>   | -10 | -   | 100 | °C   |

| Maximum Storage Temperature Range                                                          | T <sub>STG</sub> | -55 | -   | 150 | °C   |

JESD 51–5 (1S2P Direct-Attach Method) with 0 LFM.

JESD 51–7 (1S2P Direct-Attach Method) with 0 LFM.

# Table 4. ELECTRICAL CHARACTERISTICS

(Unless otherwise stated:  $-10^\circ C < T_A < 100^\circ C;$  4.6 V < VCC < 5.4 V;  $C_{VCC}$  = 0.1  $\mu F)$

| Parameter                     | Test Conditions                                | Symbol                 | Min  | Тур | Max  | Unit |

|-------------------------------|------------------------------------------------|------------------------|------|-----|------|------|

| VRMP                          |                                                |                        |      |     | •    |      |

| Supply Range                  |                                                | VRMP                   | 4.5  |     | 20   | V    |

| UVLO                          | VRMP Rising                                    | V <sub>RMPrise</sub>   |      |     | 4.2  | V    |

|                               | VRMP Falling                                   | V <sub>RMPfall</sub>   | 3    |     |      | V    |

| VRMP UVLO Hysteresis          |                                                | V <sub>RMPhyst</sub>   |      | 800 |      | mV   |

| BIAS SUPPLY                   |                                                |                        |      |     |      | •    |

| Supply Voltage Range          |                                                | VCC                    | 4.6  |     | 5.4  | V    |

| VCC Quiescent current         | Enable Low                                     | ICC                    |      |     | 40   | μΑ   |

|                               | 8 Phase Operation                              |                        |      | 50  |      | mA   |

|                               | 1 Phase-DCM Operation                          |                        |      | 10  |      | mA   |

| UVLO Threshold                | VCC Rising                                     | UVLO <sub>Rise</sub>   |      |     | 4.5  | V    |

|                               | VCC Falling                                    | UVLO <sub>Fall</sub>   | 4    |     |      | V    |

| VCC UVLO Hysteresis           |                                                | UVLO <sub>Hyst</sub>   |      | 200 |      | mV   |

| SWITCHING FREQUENCY           |                                                |                        |      |     |      |      |

| Switching Frequency Range     | 8 Phase Configuration                          | F <sub>SW</sub>        | 250  |     | 1200 | kHz  |

| Switching Frequency Accuracy  | F <sub>SW</sub> = 810 kHz                      | $\Delta F_{SW}$        | -4   |     | +4   | %    |

| ENABLE INPUT                  |                                                |                        |      |     |      |      |

| Input Leakage                 | EN = 0 V or VCC                                | ۱L                     | -1.0 |     | 1.0  | μΑ   |

| Upper Threshold               |                                                | V <sub>IH</sub>        | 1.2  |     |      | V    |

| Lower Threshold               |                                                | V <sub>IL</sub>        |      |     | 0.6  | V    |

| DRON                          |                                                |                        |      |     |      |      |

| Output High Voltage           | Sourcing 500 µA                                | V <sub>OH</sub>        | 3.0  |     |      | V    |

| Output Low Voltage            | Sinking 500 μA                                 | V <sub>OL</sub>        |      |     | 0.1  | V    |

| Rise Time                     | CI(PCB) = 20 pF,<br>$\Delta V_0 = 10\%$ to 90% | t <sub>R</sub>         |      | 160 |      | ns   |

| Fall Time                     | CI(PCB) = 20 pF,<br>$\Delta V_0 = 10\%$ to 90% | t <sub>F</sub>         |      | 3   |      | ns   |

| Internal Pull-up Resistance   |                                                | R <sub>PULL-UP</sub>   |      | 2.0 |      | kΩ   |

| Internal Pull-down Resistance | VCC = 0 V                                      | R <sub>PULL_DOWN</sub> |      | 70  |      | kΩ   |

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^\circ C < T_A < 100^\circ C;$  4.6 V < VCC < 5.4 V;  $C_{VCC}$  = 0.1  $\mu F)$

| Parameter                                   | Test Conditions                                                                                                                                              | Symbol                          | Min       | Тур  | Max       | Unit |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------|------|-----------|------|

| PGOOD                                       | •                                                                                                                                                            |                                 |           |      | •         |      |

| Output Low Voltage                          | I <sub>PGOOD</sub> = 10 mA (Sink)                                                                                                                            | V <sub>OL</sub>                 |           |      | 0.4       | V    |

| Leakage Current                             | P <sub>GOOD</sub> = 5 V                                                                                                                                      | ١ <sub>L</sub>                  |           |      | 0.2       | μΑ   |

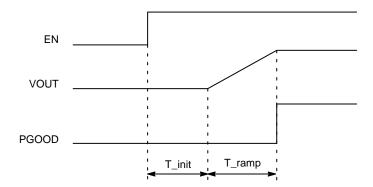

| Output Voltage Initialization Time          |                                                                                                                                                              | T_init                          |           |      | 1.5       | ms   |

| Minimum Output Voltage Ramp<br>Time         |                                                                                                                                                              | T_ramp <sub>MIN</sub>           |           | 0.15 |           | ms   |

| Maximum Output Voltage Ramp<br>Time         |                                                                                                                                                              | T_ramp <sub>MAX</sub>           |           | 10   |           | ms   |

| PROTECTION-OCP, OVP, UVP                    |                                                                                                                                                              |                                 |           |      |           | •    |

| Under Voltage Protection (UVP)<br>Threshold | Relative to REFIN Voltage                                                                                                                                    | UVP                             |           | 300  |           | mV   |

| Under Voltage Protection (UVP)<br>Delay     |                                                                                                                                                              | T <sub>UVP</sub>                |           | 5    |           | μs   |

| Over Voltage Protection (OVP)<br>Threshold  | Relative to REFIN Voltage                                                                                                                                    | OVP                             |           | 400  |           | mV   |

| Over Voltage Protection (OVP)<br>Delay      |                                                                                                                                                              | T <sub>OVP</sub>                |           | 5    |           | μs   |

| PWM OUTPUTS                                 |                                                                                                                                                              |                                 |           |      |           |      |

| Output High Voltage                         | Sourcing 500 μA                                                                                                                                              | V <sub>OH</sub>                 | VCC - 0.2 |      |           | V    |

| Output Mid Voltage                          |                                                                                                                                                              | V <sub>MID</sub>                | 1.9       | 2.0  | 2.1       | V    |

| Output Low Voltage                          | Sinking 500 μA                                                                                                                                               | V <sub>OL</sub>                 |           |      | 0.7       | V    |

| Rise and Fall Time                          | $C_L(PCB) = 50 \text{ pF}, \Delta V_O = 10\% \text{ to}$<br>90% of VCC                                                                                       | t <sub>R</sub> , t <sub>F</sub> |           | 10   |           | ns   |

| Tri-state Output Leakage                    | $G_x = 2.0 \text{ V}, x = 1-8, \text{ EN} = \text{Low}$                                                                                                      | ١ <sub>L</sub>                  | -1.0      |      | 1.0       | μΑ   |

| Minimum On Time                             | FSW = 600 kHz                                                                                                                                                | Ton                             |           | 12   |           | ns   |

| 0% Duty Cycle                               | Comp Voltage when PWM Outputs<br>Remain LOW                                                                                                                  | VCOMP <sub>0%</sub>             |           | 1.3  |           | V    |

| 100% Duty Cycle                             | Comp Voltage when PWM Outputs<br>Remain HIGH                                                                                                                 | VCOMP <sub>100%</sub>           |           | 2.5  |           | V    |

| PWM Phase Angle Error                       | Between Adjacent Phases                                                                                                                                      | ø                               |           | ±15  |           | 0    |

| PHASE DETECTION                             |                                                                                                                                                              |                                 |           |      |           |      |

| Phase Detection Threshold<br>Voltage        | CSP2 to CSP8                                                                                                                                                 | V <sub>PHDET</sub>              |           |      | VCC - 0.1 | V    |

| Phase Detect Timer                          | CSP2 to CSP8                                                                                                                                                 | T <sub>PHDET</sub>              |           | 1.1  |           | ms   |

| ERROR AMPLIFIER                             |                                                                                                                                                              |                                 |           |      |           |      |

| Input Bias Current                          |                                                                                                                                                              | I <sub>BIAS</sub>               | -400      |      | 400       | nA   |

| Open Loop DC Gain                           | $C_L = 20 \text{ pF to GND},$<br>$R_L = 10 \text{ k}\Omega \text{ to GND}$                                                                                   | G <sub>OL</sub>                 |           | 80   |           | dB   |

| Open Loop Unity Gain Bandwidth              | $C_L = 20 \text{ pF to GND},$<br>$R_L = 10 \text{ k}\Omega \text{ to GND}$                                                                                   | GBW                             |           | 20   |           | MHz  |

| Slew Rate                                   | $\begin{array}{l} \Delta V_{IN}$ = 100 mV, G = -10 V/V,<br>$\Delta V_{OUT}$ = 0.75–1.52 V, C <sub>L</sub> = 20 pF to GND, R <sub>L</sub> = 10 k\Omega to GND | SR                              |           | 5    |           | V/µs |

| Maximum Output Voltage                      | I <sub>SOURCE</sub> = 2 mA                                                                                                                                   | V <sub>OUT</sub>                | 3.5       |      |           | V    |

| Minimum Output Voltage                      | I <sub>SINK</sub> = 2 mA                                                                                                                                     | V <sub>OUT</sub>                | 1 1       |      | 1         | V    |

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^\circ C < T_A < 100^\circ C;$  4.6 V < VCC < 5.4 V;  $C_{VCC}$  = 0.1  $\mu F)$

| Parameter                                    | Parameter Test Conditions                                                                                         |                      | Min    | Тур | Max  | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|--------|-----|------|------|

| DIFFERENTIAL SUMMING AMPLI                   | FIER                                                                                                              | I                    | 1      | 1   | •    |      |

| Input Bias Current                           |                                                                                                                   | I <sub>BIAS</sub>    | -400   |     | 400  | nA   |

| VSP Input Voltage                            |                                                                                                                   | V <sub>IN</sub>      | 0      |     | 2    | V    |

| VSN Input Voltage                            |                                                                                                                   | V <sub>IN</sub>      | -0.3   |     | 0.3  | V    |

| -3dB Bandwidth                               | $C_L = 20 \text{ pF to GND},$<br>$R_L = 10 \text{ k}\Omega \text{ to GND}$                                        | BW                   |        | 12  |      | MHz  |

| Closed Loop DC Gain<br>(VSP–VSN to DIFF)     | VSP to VSN = 0.5 to 1.3 V                                                                                         | G                    |        | 1   |      | V/V  |

| Droop accuracy                               | CSREF – DROOP = 80 mV,<br>V <sub>REFIN</sub> = 0.8 V to 1.2 V                                                     | ΔDROOP               | 78     |     | 82   | mV   |

| Maximum Output Voltage                       | I <sub>SOURCE</sub> = 2 mA                                                                                        | V <sub>OUT</sub>     | 3      |     |      | V    |

| Minimum Output Voltage                       | I <sub>SINK</sub> = 2 mA                                                                                          | V <sub>OUT</sub>     |        |     | 0.8  | V    |

| CURRENT SUMMING AMPLIFIER                    |                                                                                                                   |                      |        |     |      |      |

| Offset Voltage                               |                                                                                                                   | V <sub>OS</sub>      | -500   |     | 500  | μV   |

| Input Bias Current                           | CSSUM = CSREF = 1 V                                                                                               | ١L                   | -7.5   |     | 7.5  | μA   |

| Open Loop Gain                               |                                                                                                                   | G                    |        | 80  |      | dB   |

| Current sense Unity Gain<br>Bandwidth        | $C_L = 20 \text{ pF to GND},$<br>$R_L = 10 \text{ k}\Omega \text{ to GND}$                                        | GBW                  | GBW 10 |     |      | MHz  |

| Maximum CSCOMP Output<br>Voltage             | I <sub>SOURCE</sub> = 2 mA                                                                                        | V <sub>OUT</sub> 3.5 |        |     |      | V    |

| Minimum CSCOMP Output Voltage                | I <sub>SINK</sub> = 2 mA                                                                                          | V <sub>OUT</sub>     |        |     | 0.1  | V    |

| CURRENT BALANCE AMPLIFIER                    |                                                                                                                   |                      |        |     |      |      |

| Input Bias Current                           | $CSP_X - CSP_{X+1} = 1.2 V$                                                                                       | I <sub>BIAS</sub>    | -50    |     | 50   | nA   |

| Common Mode Input Voltage<br>Range           | CSP <sub>X</sub> = CSREF                                                                                          | V <sub>CM</sub>      | 0      |     | 2    | V    |

| Differential Mode Input Voltage<br>Range     | CSREF = 1.2 V                                                                                                     | V <sub>DIFF</sub>    | -100   |     | 100  | mV   |

| Closed Loop Input Offset Voltage<br>Matching | CSP <sub>X</sub> = 1.2 V, Measured from the Average                                                               |                      | -1.5   |     | 1.5  | mV   |

| Current Sense Amplifier Gain                 | 0 V < CSP <sub>X</sub> < 0.1 V                                                                                    | G                    | 5.7    | 6.0 |      | V/V  |

| Multiphase Current Sense Gain<br>Matching    | CSREF = CSP = 10 mV to 30 mV                                                                                      | ΔG                   | -3     |     | 3    | %    |

| -3dB Bandwidth                               |                                                                                                                   | BW                   |        | 8   |      | MHz  |

| IOUT                                         |                                                                                                                   |                      |        |     |      |      |

| Input Reference Offset Voltage               | ILIM to CSREF                                                                                                     | V <sub>OS</sub>      | -3     |     | +3   | mV   |

| Output Current Max                           | ILIM Sink Current 20 μA                                                                                           | I <sub>OUT</sub>     |        | 200 |      | μΑ   |

| Current Gain                                 | $ \begin{array}{l} \text{IOUT/ILIM, } R_{LIM} = 20 \text{ k}\Omega, \\ R_{IOUT} = 5 \text{ k}\Omega \end{array} $ | G                    | 9.5    | 10  | 10.5 | A/A  |

| VOLTAGE REFERENCE                            |                                                                                                                   | •                    | •      | •   | -    |      |

| VREF Reference Voltage                       | I <sub>REF</sub> = 1 mA                                                                                           | VREF                 | 1.98   | 2   | 2.02 | V    |

| VREF Reference accuracy                      | $T_{JMIN} < T_J < T_{JMAX}$                                                                                       | ΔVREF                | ĺ      | 1   | 1    | %    |

# Table 4. ELECTRICAL CHARACTERISTICS (continued)

(Unless otherwise stated:  $-10^{\circ}C < T_A < 100^{\circ}C$ ; 4.6 V < VCC < 5.4 V;  $C_{VCC} = 0.1 \mu F$ )

| Parameter                                                      | Test Conditions                                                                                                                                       | Symbol                              | Min  | Тур | Max   | Uni |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|-----|-------|-----|

| PSI                                                            |                                                                                                                                                       |                                     |      |     | •     |     |

| PSI High Threshold                                             |                                                                                                                                                       | V <sub>IH</sub>                     | 1.45 |     |       | V   |

| PSI Mid threshold                                              |                                                                                                                                                       | V <sub>MID</sub>                    | 0.8  |     | 1     | V   |

| PSI Low threshold                                              |                                                                                                                                                       | V <sub>IL</sub>                     |      |     | 0.575 | V   |

| PSI Input Leakage Current                                      | V <sub>PSI</sub> = 0 V                                                                                                                                | ١L                                  | -1   |     | 1     | μA  |

| PWM_VID BUFFER                                                 |                                                                                                                                                       |                                     |      |     | +     |     |

| Upper Threshold                                                |                                                                                                                                                       | V <sub>IH</sub>                     | 1.21 |     |       | V   |

| Lower Threshold                                                |                                                                                                                                                       | VIL                                 |      |     | 0.575 | V   |

| PWM_VID Switching Frequency                                    |                                                                                                                                                       | F <sub>PWM_VID</sub>                | 400  |     | 5000  | kHz |

| Output Rise Time                                               |                                                                                                                                                       | t <sub>R</sub>                      |      | 3   |       | ns  |

| Output Fall Time                                               |                                                                                                                                                       | t <sub>F</sub>                      |      | 3   |       | ns  |

| Rising and Falling Edge Delay                                  | $\Delta t = t_R - t_F$                                                                                                                                | Δt                                  |      | 0.5 |       | ns  |

| Propagation Delay                                              | t <sub>PD</sub> = t <sub>PDHL</sub> = t <sub>PDLH</sub>                                                                                               | t <sub>PD</sub>                     |      | 8   |       | ns  |

| Propagation Delay Error                                        | $\Delta t_{PD} = t_{PDHL} - t_{PDLH}$                                                                                                                 | $\Delta t_{PD}$                     |      | 0.5 |       | ns  |

| REFIN                                                          |                                                                                                                                                       |                                     |      |     | •     |     |

| REFIN Discharge Switch<br>ON-Resistance                        | $I_{\text{REEFIN}(\text{SINK})} = 2 \text{ mA}$                                                                                                       | R <sub>DISCH</sub>                  |      | 10  |       | Ω   |

| Ratio of Output Voltage Ripple<br>Transferred from REFIN/REFIN | $\begin{array}{l} {\sf F}_{PWM\_VID} = 400 \ \text{kHz}, \\ {\sf F}_{SW} \leq 600 \ \text{kHz} \end{array}$                                           | V <sub>ORP/VREFIN</sub>             |      | 10  |       | %   |

| Voltage Ripple                                                 | $\label{eq:F_PWM_VID} \begin{array}{l} \mbox{F}_{PWM\_VID} \mbox{=} 1000 \mbox{ kHz}, \\ \mbox{F}_{SW} \end{tabular} \le 600 \mbox{ kHz} \end{array}$ | V <sub>ORP/VREFIN</sub>             |      | 30  |       |     |

| l <sup>2</sup> C                                               |                                                                                                                                                       | · · ·                               |      |     |       |     |

| Logic High Input Voltage                                       |                                                                                                                                                       | V <sub>IH</sub>                     | 1.7  |     |       | V   |

| Logic Low Input Voltage                                        |                                                                                                                                                       | V <sub>IL</sub>                     |      |     | 0.5   | V   |

| Hysteresis (Note 4)                                            |                                                                                                                                                       |                                     |      | 80  |       | mV  |

| Output Low Voltage                                             | I <sub>SDA</sub> = –6 mA                                                                                                                              | V <sub>OL</sub>                     |      |     | 0.4   | V   |

| Input Current                                                  |                                                                                                                                                       | ΙL                                  | –1   |     | 1     | μΑ  |

| Input Capacitance (Note 4)                                     |                                                                                                                                                       | C <sub>SDA</sub> , C <sub>SCL</sub> |      | 5   |       | pF  |

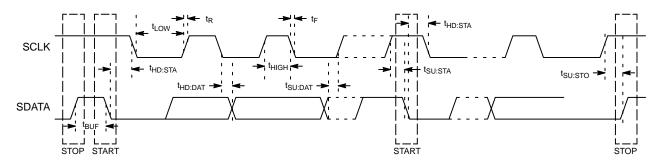

| Clock Frequency                                                | See Figure 3                                                                                                                                          | f <sub>SCL</sub>                    |      |     | 400   | kHz |

| SCL Low Period (Note 4)                                        |                                                                                                                                                       | t <sub>LOW</sub>                    | 1.3  |     |       | μs  |

| SCL High Period (Note 4)                                       |                                                                                                                                                       | t <sub>HIGH</sub>                   | 0.6  |     |       | μs  |

| SCL/SDA Rise Time (Note 4)                                     |                                                                                                                                                       | t <sub>R</sub>                      |      |     | 300   | ns  |

| SCL/SDA Fall Time (Note 4)                                     |                                                                                                                                                       | t <sub>F</sub>                      |      |     | 300   | ns  |

| Start Condition Setup Time (Note 4)                            |                                                                                                                                                       | <sup>t</sup> SU;STA                 | 600  |     |       | ns  |

| Start Condition Hold Time<br>(Note 1, 4)                       |                                                                                                                                                       | thd;sta                             | 600  |     |       | ns  |

| Data Setup Time (Note 2, 4)                                    |                                                                                                                                                       | t <sub>SU;DAT</sub>                 | 100  |     |       | ns  |

| Data Hold Time (Note 2, 4)                                     |                                                                                                                                                       | t <sub>HD;DAT</sub>                 | 300  |     |       | ns  |

| Stop Condition Setup Time<br>(Note 3, 4)                       |                                                                                                                                                       | t <sub>SU;STO</sub>                 | 600  |     |       | ns  |

| Bus Free Time between Stop<br>and Start (Note 4)               |                                                                                                                                                       | t <sub>BUF</sub>                    | 1.3  |     |       | μs  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 1. Time from 10% of SDA to 90% of SCL.

Time from 10% or 90% of SDA to 10% of SCL.

Time from 90% of SCL to 10% of SDA.

4. Guaranteed by design, not production tested.

Figure 3. I<sup>2</sup>C Timing Diagram

Figure 4. Soft Start Timing Diagram

### **Applications Information**

The NCP81276 is a buck converter controller optimized for the next generation computing and graphic processor applications. It contains four PWM channels which can be individually configured to accommodate buck converter configurations up to four phases. The controller regulates the output voltage all the way down to 0 V with no load. Also, the device is functional with input voltages as low as 3.3 V.

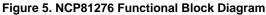

The output voltage is set by applying a PWM signal to the PWM\_VID input of the device. The controller converts the PWM\_VID signal with variable high and low levels into a constant amplitude PWM signal which is then applied to the REFIN pin. The device calculates the average value of this PWM signal and sets the regulated voltage accordingly.

The output voltage is differentially sensed and subtracted from the REFIN average value. The result is biased up to 1.3 V and applied to the error amplifier. Any difference between the sensed voltage and the REFIN pin average voltage will change the PWM outputs duty cycle until the two voltages are identical. The load current is current is continuously monitored on each phase and the PWM outputs are adjusted to ensure adjusted to ensure even distribution of the load current across all phases. In addition, the total load current is internally measured and used to implement a programmable adaptive voltage positioning mechanism.

The device incorporates overcurrent, under and overvoltage protections against system faults.

The communication between the NCP81276 and the user is handled with two interfaces, PWM\_VID to set the output voltage and  $I^2C$  to configure or monitor the status of the controller. The operation of the internal blocks of the device is described in more details in the following sections.

#### **PWM\_VID** Interface

PWM\_VID is a single wire dynamic voltage control interface where the regulated voltage is set by the duty cycle of the PWM signal applied to the controller.

The device controller converts the variable amplitude PWM signal into a constant 2 V amplitude PWM signal while preserving the duty cycle information of the input signal. In addition, if the PWM\_VID input is left floating, the VID\_BUFF output is tri-stated (floating).

The constant amplitude PWM signal is then connected to the REFIN pin through a scaling and filtering network (see Figure 6). This network allows the user to set the minimum and maximum REFIN voltages corresponding to 0% and 100% duty cycle values.

Figure 6. PWM\_VID Interface

The minimum (0% duty cycle), maximum (100% duty cycle) and boot (PWM\_VID input floating) voltages can be calculated with the following formulas:

$$V_{MAX} = V_{REF} \cdot \frac{1}{1 + \frac{R_1 \cdot R_3}{R_2 \cdot (R_1 + R_2)}}$$

(eq. 1)

$$V_{MIN} = V_{REF} \cdot \frac{1}{1 + \frac{R_1 \cdot (R_2 + R_3)}{R_2 \cdot R_3}}$$

(eq. 2)

$$V_{BOOT} = V_{REF} \cdot \frac{1}{1 + \frac{R_1}{R_2}}$$

(eq. 3)

#### Soft Start

Soft start is defined as the transition from Enable assertion high to the assertion of Power good as shown in Figure 4.

The output is set to the desired voltage in two steps, a fixed initialization step of 1.5 ms followed by a ramp-up step where the output voltage is ramped to the final value set by the PWM\_VID interface. During the soft start phase, PGOOD pin is initially set low and will be set high when the output voltage is within regulation and the soft start ramp is complete. The PGOOD signal only de-asserts (pull low) when the controller shuts down due to a fault condition (UVLO, OVP or OCP event). The output voltage ramp-up time is user settable by connecting a resistor between pin SS and GND. The controller will measure the resistance value at power-up by sourcing a 10  $\mu$ A current through this resistor and set the ramp time (t<sub>ramp</sub>) as shown in Table 16.

#### **Remote Voltage Sense**

A high performance true differential amplifier allows the controller to measure the output voltage directly at the load using the VSP (VOUT) and VSN (GND) pins. This keeps the ground potential differences between the local controller ground and the load ground reference point from affecting regulation of the load. The output voltage of the differential amplifier is set by the following equation:

$$\begin{split} \mathsf{V}_{\mathsf{DIFOUT}} &= \left(\mathsf{V}_{\mathsf{VSP}} - \mathsf{V}_{\mathsf{VSN}}\right) + \left(1.3 \ \mathsf{V} - \mathsf{V}_{\mathsf{REFIN}}\right) + \\ &+ \left(\mathsf{V}_{\mathsf{DROOP}} + \mathsf{V}_{\mathsf{CSREF}}\right) \end{split} \tag{eq. 4}$$

Where:

$V_{DIFOUT}$  is the output voltage of the differential amplifier.

$V_{VSP} - V_{VSN}$  is the regulated output voltage sensed at the load.

$V_{REFIN}$  is the voltage at the output pin set by the PWM\_VID interface.

$V_{DROOP} - V_{CSREF}$  is the expected drop in the regulated voltage as a function of the load current (load-line).

1.3 V is an internal reference voltage used to bias the amplifier inputs to allow both positive and negative output voltage for V<sub>DIFOUT</sub>.

#### **Error Amplifier**

A high performance wide bandwidth error amplifier is provided for fast response to transient load events. Its inverting input is biased internally with the same 1.3 V reference voltage as the one used by the differential sense amplifier to ensure that both positive and negative error voltages are correctly handled.

An external compensation circuit should be used (usually type III) to ensure that the control loop is stable and has adequate response.

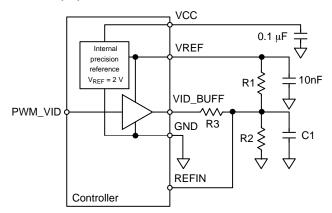

#### Ramp Feed-Forward Circuit

The ramp generator circuit provides the ramp used to generate the PWM signals using internal comparators (see Figure 7) The ramp generator provides voltage feed-forward control by varying the ramp magnitude with respect to the VRMP pin voltage. The PWM ramp time is changed according to the following equation:

$$V_{RAMPpk=pk_{DD}} = 0.1 \cdot V_{VRMP}$$

(eq. 5)

The VRMP pin also has a UVLO function. The VRMP UVLO is only active after the controller is enabled. The VRMP pin is high impedance input when the controller is disabled.

#### **PWM Output Configuration**

By default the controller operates in 4 phase mode, however with the use of the CSP pins the phases can be disabled by connecting the CSP pin to VCC. At power-up the NCP81276 measures the voltage present at each CSP pin and compares it with the phase detection threshold. If the voltage exceeds the threshold, the phase is disabled. The phase configurations that can be achieved by the device are listed in Table 6. The active phase (PWM<sub>X</sub>) information is also available to the user in the phase status register.

### PSI, LPC<sub>X</sub>, PHTH<sub>X</sub>

The NCP81276 incorporates a power saving interface (PSI) to maximize the efficiency of the regulator under various loading conditions. The device supports up to six distinct operation modes, called power zones using the PSI, LPC<sub>X</sub> and PHTH<sub>X</sub> pins (see Table 7). At power-up the controller reads the PSI pin logic state and sources a 10  $\mu$ A current through the resistors connected to the LPC<sub>X</sub> and PHTH<sub>X</sub> pins, measures the voltage at these pins and configures the device accordingly.

The configuration can be changed by the user by writing to the  $LPC_X$  and  $PHTH_X$  configuration registers.

After EN is set high, the NCP81276 ignores any change in the PSI pin logic state until the output voltage reaches the nominal regulated voltage.

When PSI = High, the controller operates with all active phases enabled regardless of the load current. If PSI = Mid, the NCP81276 operates in dynamic phase shedding mode where the voltage present at the IOUT pin (the total load current) is measured every 10  $\mu$ s and compared to the PHTH<sub>X</sub> thresholds to determine the appropriate power zone.

The resistors connected between the PHTH<sub>X</sub> and GND should be picked to ensure that a 10  $\mu$ A current will match the voltage drop at the IOUT pin at the desired load current. Please note that the maximum allowable voltage at the IOUT pin at the maximum load current is 2 V. Any PHTH<sub>X</sub> threshold can be disabled if the voltage drop across the PHTH<sub>X</sub> resistor is  $\geq 2$  V for a 10  $\mu$ A current, the pin is left floating or 0xFF is written to the appropriate PHTH<sub>X</sub> configuration register.

At power-up, the automatic phase shedding mode is only enabled after the output voltage reaches the nominal regulated voltage. When PSI = Low, the controller is set to a fixed power zone regardless of the load current. The LPC2 setting controls the power zone used during boot-up (after EN is set high) while the LPC1 configuration sets the power zone during normal operation. If PSI = Low during power-up, the configuration set by LPC1 is activated only after PSI leaves the low state (set to Mid or High) and set again to the low state.

### LLTH/I2C\_ADD

The LLTH/I2C\_ADD pin enables the user to change the percentage of the externally programmed droop that takes effect on the output. In addition, the LLTH/I2C\_ADD pin sets the I<sup>2</sup>C slave address of the NCP81276. The maximum load line is controlled externally by setting the gain of the current sense amplifier. On power up a 10  $\mu$ A current is sourced from the LLTH/I2C\_ADD pin through a resistor and the resulting voltage is measured. The load line and I<sup>2</sup>C slave address configurations achievable using the external resistor is listed in the table below. The percentage load line can be fine-tuned over the I<sup>2</sup>C interface by writing to the LL configuration register.

| Table 5. Ll | LTH/I2C_ADD | PIN SETTING |

|-------------|-------------|-------------|

|-------------|-------------|-------------|

| —                |                  |                        |  |  |  |  |

|------------------|------------------|------------------------|--|--|--|--|

| Resistor<br>(kΩ) | Load Line<br>(%) | Slave Address<br>(Hex) |  |  |  |  |

| 10               | 100              | 0x20                   |  |  |  |  |

| 23.2             | 0                | 0x20                   |  |  |  |  |

| 37.4             | 100              | 0x30                   |  |  |  |  |

| 54.9             | 0                | 0x30                   |  |  |  |  |

| 78.7             | 100              | 0x40                   |  |  |  |  |

| 110              | 0                | 0x40                   |  |  |  |  |

| 147              | 100              | 0x50                   |  |  |  |  |

| 249              | 0                | 0x50                   |  |  |  |  |

NOTE: 1% tolerance.

# Table 6. PWM OUTPUT CONFIGURATION

|               | Phase         | (√           | Enabled<br>PWM Outputs |      |      |                         |

|---------------|---------------|--------------|------------------------|------|------|-------------------------|

| Configuration | Configuration | CSP1         | CSP2                   | CSP3 | CSP4 | (PWM <sub>X</sub> Pins) |

| 1             | 4 Phase       | $\checkmark$ | 1                      | ✓    | 1    | 1, 2, 3, 4              |

| 2             | 3 Phase       | 1            | √                      | √    | Х    | 1, 2, 3                 |

| 3             | 2 Phase       | $\checkmark$ | 1                      | Х    | Х    | 1, 2                    |

| 4             | 1 Phase       | 1            | Х                      | Х    | Х    | 1                       |

# Table 7. PSI, LPC<sub>X</sub>, PHTH<sub>X</sub> CONFIGURATION (Note 1)

| PSI<br>Logic | LPC <sub>X</sub><br>Resistor |                      | Power Zone (Note 2) |         |         |         |  |  |  |  |

|--------------|------------------------------|----------------------|---------------------|---------|---------|---------|--|--|--|--|

| State        |                              |                      | 4 Phase             | 3 Phase | 2 Phase | 1 Phase |  |  |  |  |

| High         | Disabled                     | Function Disabled    | 0                   | 0       | 0       | 0       |  |  |  |  |

| Low          | 10                           |                      | 0                   | 0       | 0       | 0       |  |  |  |  |

|              | 23.2                         |                      | 0                   | 0       | 0       | 0       |  |  |  |  |

|              | 37.4<br>54.9                 |                      | 2                   | 0       | 0       | 0       |  |  |  |  |

|              |                              |                      | 3                   | 3       | 3       | 0       |  |  |  |  |

|              | 78.7                         |                      | 4                   | 4       | 4       | 4       |  |  |  |  |

| Mid          | Function                     | IOUT > PHTH4         | 0                   | 0       | 0       | 0       |  |  |  |  |

|              | Disabled                     | PTHT4 > IOUT > PHTH3 | 0                   | 0       | 0       | 0       |  |  |  |  |

|              |                              | PHTH3 > IOUT > PHTH2 | 2                   | 0       | 0       | 0       |  |  |  |  |

|              |                              | PHTH2 > IOUT > PHTH1 | 3                   | 3       | 3       | 0       |  |  |  |  |

|              |                              | IOUT < PHTH1         | 4                   | 4       | 4       | 4       |  |  |  |  |

1. 1% tolerance.

2. Power zone 4 is DCM @100 kHz switching frequency, while zones 0 to 3 are CCM.

# Table 8. PHASE SHEDDING CONFIGURATIONS

|            |                          | PWM O        | utput Status (🗸 : | = Enabled, X = D | Disabled) |

|------------|--------------------------|--------------|-------------------|------------------|-----------|

| Power Zone | PWM Output Configuration | PWM1         | PWM2              | PWM3             | PWM4      |

| 0          | 4 Phase                  | 1            | 1                 | 1                | 1         |

| 2          |                          | ✓            | Х                 | ✓                | Х         |

| 3          |                          | ✓            | Х                 | Х                | Х         |

| 4          |                          | ✓            | Х                 | Х                | Х         |

| 0          | 3 Phase                  | ✓            | 1                 | ✓                | Х         |

| 3          |                          | ✓            | Х                 | Х                | Х         |

| 4          |                          | ✓            | Х                 | Х                | Х         |

| 0          | 2 Phase                  | 1            | 1                 | Х                | Х         |

| 3          |                          | ✓            | Х                 | Х                | Х         |

| 4          |                          | $\checkmark$ | Х                 | Х                | Х         |

| 0          | 1 Phase                  | 1            | х                 | х                | Х         |

| 4          |                          | ✓            | Х                 | Х                | Х         |

#### **Power Zone Transition/Phase Shedding**

The power zones supported by the NCP81276 are set by the resistors connected to the LPC<sub>X</sub> pins (PSI = Low) or PHTH<sub>X</sub> pins (PSI = Mid).

When PSI is set to the Mid-state, the NCP81276 employs a phase shedding scheme where the power zone is automatically adjusted for optimal efficiency by continuously measuring the total output current (voltage at the IOUT pin) and compare it with the PHTH<sub>X</sub> thresholds. When the comparison result indicates that a lower power zone number is required (an increase in the IOUT value), the controller jumps to the required power zone immediately. A decrease in IOUT that indicates that the controller needs to switch into a higher power zone number, the transition will be executed with a delay of 200 µs set by the phase shed delay configuration register. The value of the delay can be adjusted by the user in steps of 10 µs if required. To avoid excessive ripple on the output voltage, all power zone changes are gradual and include all intermediate power zones between the current zone and the target zone set by the comparison of the output current with the PHTH<sub>X</sub> thresholds, each transition introducing a programmable 200 µs delay. To avoid false changes from one power zone to another caused by noise or short IOUT transients, the comparison between IOUT and PHTH<sub>X</sub> threshold uses hysteresis. The switch to a lower power zone is executed if IOUT exceeds the PHTH<sub>X</sub> threshold values while a transition to a higher power zone number is only executed if IOUT is below PHTH<sub>X</sub>-Hysteresis value. The hysteresis value is set to 0x10h and can be changed by the user by writing to the phase shedding configuration register. If a power zone/PHTH<sub>X</sub> threshold is disabled, the controller will skip it during the power zone transition process.

When PSI = Low and the user requires to change the power zone, the transition to the new power zone is identical to the transition process used when PSI is set to the Mid-state. The only exception is when the target power zone is disabled in automatic phase shedding mode. In this case, the controller will automatically enable the target power zone and allow the transition. When the controller is set to automatic phase shedding, the power zone will be automatically disabled.

### **Switching Frequency**

A programmable precision oscillator is provided. The clock oscillator serves as the master clock to the ramp generator circuit. This oscillator is programmed by a resistor to ground on the FSW pin. The FSW pin provides approximately 2 V out and the source current is mirrored into the internal ramp oscillator. The oscillator frequency is approximately proportional to the current flowing in the resistor. Table 19 lists the switching frequencies that can be set using discrete resistor values for each phase configuration. Also, the switching frequency information is available in the FSW configuration register and it can be changed by the user by writing to the FSW configuration register.

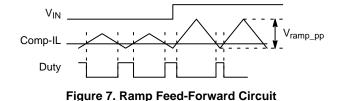

#### **Total Current Sense Amplifier**

The controller uses a patented approach to sum the phase currents into a single temperature compensated total current signal (Figure 8).

This signal is then used to generate the output voltage droop, total current limit, and the output current monitoring functions. The total current signal is floating with respect to CSREF. The current signal is the difference between CSCOMP and CSREF. The REF(n) resistors sum the signals from the output side of the inductors to create a low impedance virtual ground.

The amplifier actively filters and gains up the voltage applied across the inductors to recover the voltage drop across the inductor series resistance (DCR). RTH is placed near an inductor to sense the temperature of the inductor. This allows the filter time constant and gain to be a function of the NTC's resistance (RTH) and compensate for the change in the DCR with temperature.

The DC gain equation for the current sensing:

Figure 8. Total Current Summing Amplifier

Set the gain by adjusting the value of the RPH resistors. The DC gain should be set to the output voltage droop. If the voltage from CSCOMP to CSREF is less than 100 mV at the maximum output current IOUT<sub>MAX</sub> then it is recommend increasing the gain of the CSCOMP amp. This is required to provide a good current signal to offset voltage ratio for the ILIMIT pin. The NTC should be placed near the inductor used by phase 1. The output voltage droop should be set with the droop filter divider.

The pole frequency in the CSCOMP filter should be set equal to the zero from the output inductor. This allows the circuit to recover the inductor DCR voltage drop current signal. It is best to fine tune this filter during transient testing.

$$F_{Z} = \frac{DCR@25C}{2 \cdot \pi \cdot L_{Phase}}$$

(eq. 7)

### Programming the Current Limit ILIM

The current limit thresholds are programmed with a resistor between the ILIMIT and CSCOMP pins. The ILIMIT pin mirrors the voltage at the CSREF pin and mirrors the sink current internally to IOUT (reduced by the IOUT Current Gain) and the current limit comparators. The 100% current limit trips if the ILIMIT sink current exceeds 10  $\mu$ A for 50  $\mu$ s. The 150% current limit trips with minimal delay if the ILIMIT sink current exceeds 15  $\mu$ A. Set the value of the current limit resistor based on the CSCOMP–CSREF voltage as shown below.

$$RILIM = \frac{V_{CSCOMP-CSREF@ILIMIT}}{10 \,\mu A} \qquad (eq. 8)$$

or

$$RILIM = \frac{\frac{RCS2 + \frac{RCS1 \cdot RTH}{RCS1 + RTH}}{RPH} \cdot I_{OUT_{LIMIT}} \cdot DCR}{10 \text{ uA}} \quad (eq. 9)$$

#### Programming DROOP

The signals CSCOMP and CSREF are differentially summed with the output voltage feedback to add precision voltage droop to the output voltage.

$$Droop = DCR \cdot \frac{(RCS1 \parallel RTH) + RCS2}{RPH} \quad (eq. 10)$$

#### **Programming IOUT**

The IOUT pin sources a current in proportion to the ILIMIT sink current. The voltage on the IOUT pin is monitored by the internal A/D converter and should be scaled with an external resistor to ground such that a load equal to system max current generates a 2 V signal on IOUT. A pull-up resistor to VCC can be used to offset the IOUT signal positive if needed.

$$R_{IOUT} = \frac{2.0 \text{ V} \cdot \text{RILIM}}{\frac{\text{RCS2} + \frac{\text{RCS1} \cdot \text{RTH}}{\text{RCS1} + \text{RTH}}}{10 \cdot \frac{\text{RCS2} + \text{RTH}}{\text{RPH}} \cdot I_{OUT_{MAX}} \cdot \text{DCR}}$$

(eq. 11)

# PROTECTIONS

#### OCP

The device incorporates an over current protection mechanism to shut down and latch off to protect against damage due to an over current event. The current limit threshold set by the ILIM pin on a full system basis.

The current limit thresholds are programmed with a resistor between the ILIMIT and CSCOMP pins. The ILIMIT pin mirrors the voltage at the CSREF pin and mirrors the sink current internally to IOUT (reduced by the IOUT Current Gain) and the current limit comparators. Set the value of the current limit resistor based on the CSCOMP–CSREF voltage as shown in the Programming the Current Limit ILIM section.

In addition to the total current protection, the device incorporates an OCP function on a per phase basis by continuously monitoring the CSPX–CSREF voltage. The per-phase OCP limit is selected on startup when a 10  $\mu$ A current is sourced from the OCP. The resulting voltage read on the pin selects both the max per phase current and delay time (see Table 9). These can also be programmed over I<sup>2</sup>C (see Table 17).

| Table 9. | PER | PHASE | OCP | SETTINGS |

|----------|-----|-------|-----|----------|

|----------|-----|-------|-----|----------|

| Resistance<br>(kΩ) | Per Phase Voltage<br>(mV) | Latch Off Delay<br>(ms) |

|--------------------|---------------------------|-------------------------|

| 10                 | 65                        | 4                       |

| 14.7               | 75                        | 4                       |

| 20                 | 100                       | 4                       |

| 26.1               | 134                       | 4                       |

| 33.2               | 65                        | 6                       |

| 41.2               | 75                        | 6                       |

| 49.9               | 100                       | 6                       |

| 60.4               | 134                       | 6                       |

| 71.5               | 65                        | 8                       |

| 84.5               | 75                        | 8                       |

| 100                | 100                       | 8                       |

| 118.3              | 134                       | 8                       |

| 136.6              | 65                        | 10                      |

| 157.7              | 75                        | 10                      |

| 182.1              | 100                       | 10                      |

| 249                | 134                       | 10                      |

NOTE: 1% tolerance.

# Under Voltage Lock-Out (VCC UVLO)

VCC is constantly monitored for the under voltage lockout (UVLO) During power up both the VRMP and the VCC pin are monitored Only after both pins exceed their individual UVLO threshold will the full circuit be activated and ready for the soft start ramp.

#### **Over Voltage Protection**

An output voltage monitor is incorporated into the controller. During normal operation, if the output voltage is 400 mV over the REFIN value, the PGOOD pin will go low, the DRON will assert low and the PWM outputs are set low. The limit will be clamped at 2 V if REFIN is driven above 2 V. The outputs will remain disabled until the power is cycled or the EN pin is toggled.

# I<sup>2</sup>C Interface

The controller is connected to this bus as a slave device, under the control of a master controller.

Data is sent over the serial bus in sequences of nine clock pulses: eight bits of data followed by an acknowledge bit from the slave device. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, because a low-to-high transition when the clock is high might be interpreted as a stop signal. The number of data bytes that can be transmitted over the serial bus in a single read or write operation is limited only by what the master and slave devices can handle.

The serial bus protocol operates as follows:

- 1. The master initiates data transfer by establishing a START condition, defined as a high-to-low transition on the serial data line SDA while the serial clock line, SCL, remains high. This indicates that an address/data stream will follow. All slave peripherals connected to the serial bus respond to the START condition, and shift in the next eight bits, consisting of a 7-bit address (MSB first) plus an R/W bit, which determines the direction of the data transfer, i.e., whether data will be written to or read from the slave device. The peripheral whose address corresponds to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the Acknowledge Bit. All other devices on the bus now remain idle while the selected device waits for data to be read from or written to it. If the R/W bit is a 0, the master will write to the slave device. If the R/W bit is a 1, the master will read from the slave device.

- 2. Data is sent over the serial bus in sequences of nine clock pulses, eight bits of data followed by an Acknowledge Bit from the slave device. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, as a low-to-high transition when the clock is high may be interpreted as a STOP signal. The number of data bytes that can be transmitted over the serial bus in a single READ or WRITE operation is limited only by what the master and slave devices can handle.

- 3. When all data bytes have been read or written, stop conditions are established. In WRITE mode, the master will pull the data line high during the 10<sup>th</sup> clock pulse to assert a STOP condition. In READ mode, the master device will override the acknowledge bit by pulling the data line high during the low period before the ninth clock pulse. This is known as No Acknowledge. The master will then take the data line low during the low period before the tenth clock pulse, then high during the tenth clock pulse to assert a STOP condition.

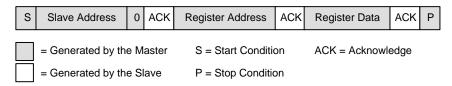

4. Any number of bytes of data may be transferred over the serial bus in one operation, but it is not possible to mix read and write in one operation because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation. To write data to one of the device data registers or read data from it, the Address Pointer Register must be set so that the correct data register is addressed, and then data can be written into that register or read from it. The first byte of a write operation always contains an address that is stored in the Address Pointer Register. If data is to be written to the device, the write operation contains a second data byte that is written to the register selected by the address pointer register. The device address is sent over the bus followed by R/W set to 0. This is followed by two data bytes. The first data byte is the address of the internal data register to be written to, which is stored in the Address Pointer Register. The second data byte is the data to be written to the internal data register.

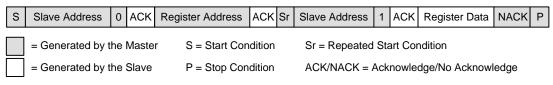

# **READ A SINGLE WORD**