# WPC8763L Notebook Embedded Controller with SPI™ Flash Interface

## **General Description**

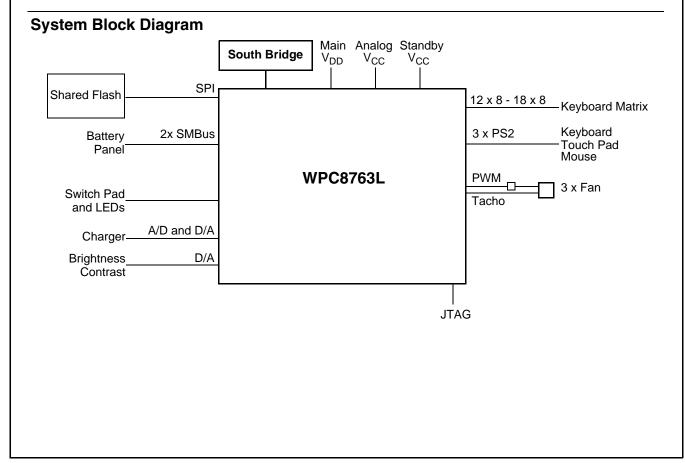

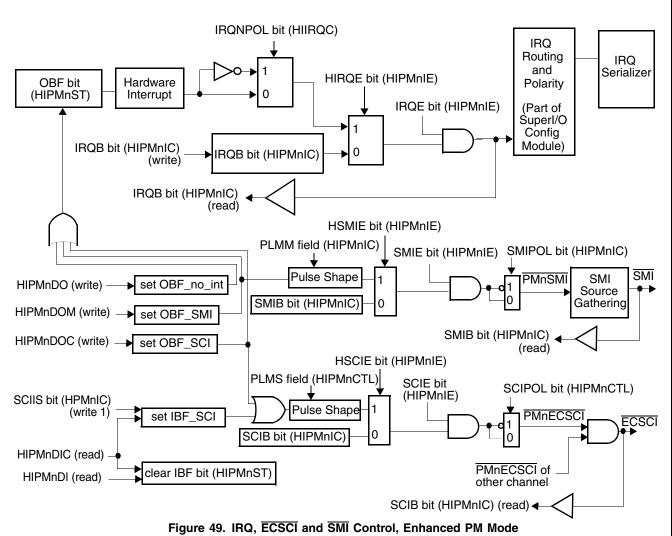

The Winbond WPC8763L is a highly integrated embedded controller (EC) with an embedded RISC core and integrated advanced functions. It is targeted for a wide range of portable applications.

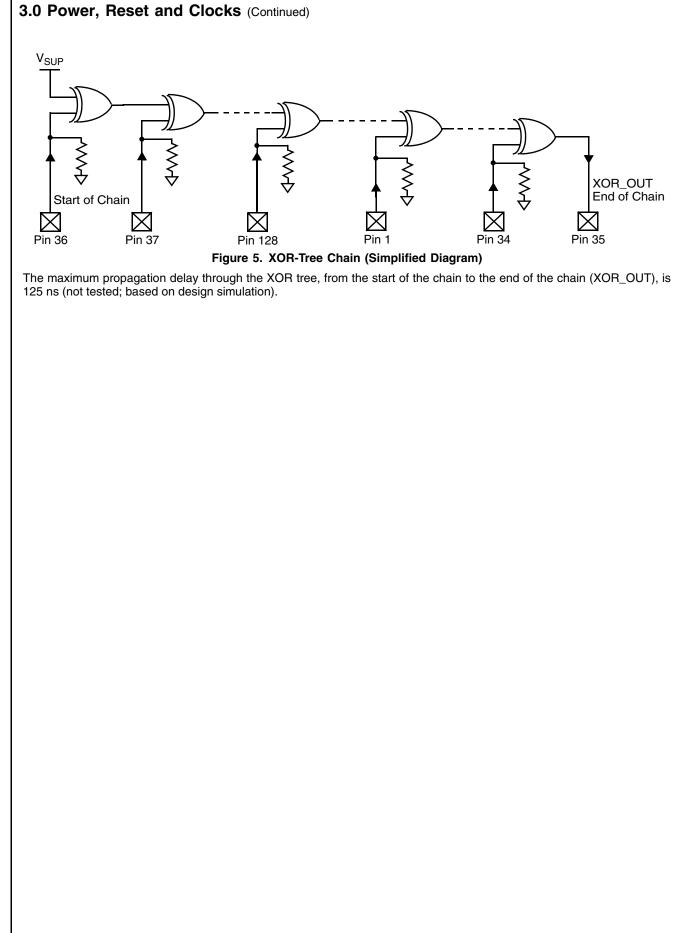

The WPC8763L incorporates the CompactRISC<sup>®</sup> CR16CPlus core (a high-performance 16-bit RISC processor), on-chip ROM and RAM memories, system support functions and a Flash Interface Unit (FIU) that interfaces directly with external SPI flash memory devices.

System support functions include: watchdog, PWM, timers, interrupt control, General-Purpose I/O (GPIO) with internal keyboard matrix scanning, PS/2<sup>®</sup> interface, SMBus<sup>®</sup> interface, UART, high-accuracy analog-to-digital (ADC) and digital-to-analog (DAC) converters for battery charging, system control, system health monitoring and analog controls.

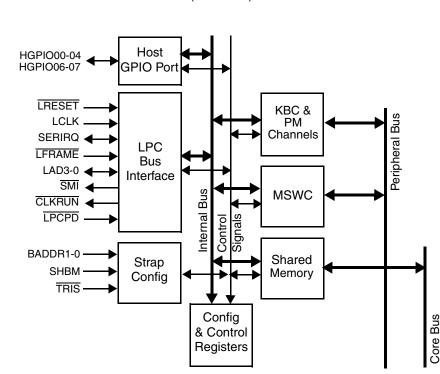

The WPC8763L interfaces with the host via an LPC interface.

The WPC8763L is PC01 and ACPI compliant, and offers a single-chip solution for the most commonly used notebook PC I/O peripherals.

## **Outstanding Features**

- Shared BIOS flash memory

- Support for SPI flash memories

- Flash page programing support

- High-accuracy, high-speed ADC

- Up to 88 GPIO ports (including keyboard scanning) with a variety of wake-up events

- 16-bit RISC core, with up to 4 Mbytes of external address space, running at up to 25 MHz

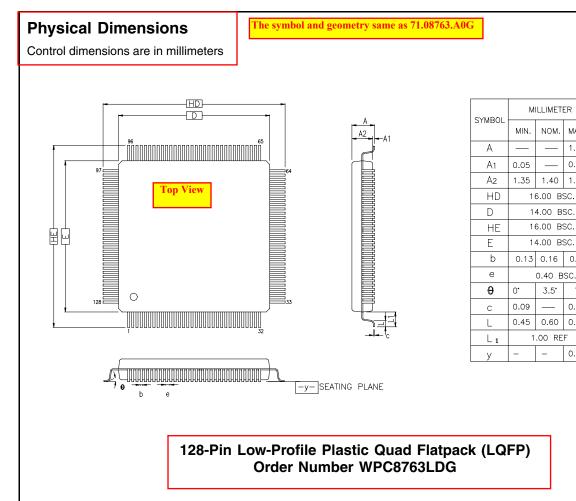

- 128-pin LQFP package

## Features

#### **Embedded Controller Features**

- Processing Unit

- CompactRISC CR16CPlus 16-bit embedded RISC processor core (the "core")

- Up to 4 Mbytes of external address space

- Internal Memory

- 1 Kbyte of ROM

- 4 Kbytes of on-chip RAM

- All memory types can hold both code and data

- Flash Interface Unit (FIU)

- Up to 4 Mbytes of code and data

- Hardware-protected boot zone block protection

- SPI External Memory

- Up to 32 Mbits

- Fast Read mode

- Page programing support

- Configurable clock rate

- Field upgradeable

- Shared Memory Controller (SHM)

- Supports BIOS (flash) memory sharing with PC host

- Supports host-controlled code download and update

- Memory access protection

#### LPC System Interface

- Based on Intel's LPC Interface Specification Revision 1.1, August 2002

- I/O, Memory and 8-bit Firmware Memory read and write cycles, Firmware Memory writes may insert wait cycles

- Bootable Memory Support

- Base Address (BADDR1-0) straps to determine the base address of the index-data register pair

- Alternate base address configurable by the core

- LPCPD and CLKRUN support

#### Embedded Controller System Features

- Host Interface

- Comprises host interface channels, typically used for KBC and ACPI Private or Shared EC channels

- 8042 KBC-standard interface (legacy 60h, 64h)

- Two PM interface ports (legacy 62h, 66h; 68h, 6Ch)

- ACPI EC with either Shared or Private interface through the PM interface

- Two Mailbox areas for host-core communication, up to 4 Kbytes each; maximum 4 Kbytes total

- Generates IRQ, SMI and SCI

- Provides IRQ1 and IRQ12 support

- Provides Fast Gate A20 and Fast Host reset via firmware

- Interrupt Control Unit (ICU)

- 31 maskable vectored interrupts (of which eight are external)

- General-purpose external interrupt inputs through MIWU

- Enable and pending indication for each interrupt

- Non-maskable interrupt input

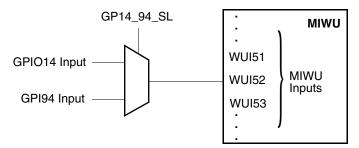

- Multi-Input Wake-Up (MIWU)

- Up to 40 wake-up or interrupt inputs

- Generates wake-up event to PMC (Power Management Controller)

- Generates interrupts to ICU

- User-selectable trigger conditions

- Internal Keyboard Matrix Scanning

- Up to 18 open-collector outputs (at least 12)

- Eight Schmitt inputs with internal pull-ups

- General-Purpose I/O (GPIO) Ports

- 64 port pins

- I/O pins individually configured as input or output

- Configurable internal pull-up / pull-down resistors

- Outputs individually configured as push-pull or open-drain

- Two echo inputs with wake-enabled interrupts

- Additional 12 GPIOs with wake-enabled interrupts

- Four GPIOs capable of 12 mA sink current

- Seven GPIOs are accessible to the host

- Optional low-cost external GPIO expansion through the SensorPath interface

- PS/2 Interface

- Three external ports: can be used for keyboard, mouse and an additional pointing device

- Byte-level handling via hardware accelerator

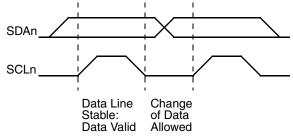

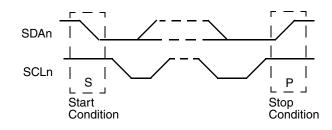

- Two SMBus (SMB) Interface Modules; each module:

- Is Intel SMBus, Philips I<sup>2</sup>C<sup>®</sup> and ACCESS,bus compatible

- Is SMBus master and slave

- Supports up to two simultaneous slave addresses

- Supports polling- and interrupt-controlled operations

- Generates a wake-up signal on detection of a Start condition while in Idle mode

- Supports an optional internal pull-up on SDA and SCL pins

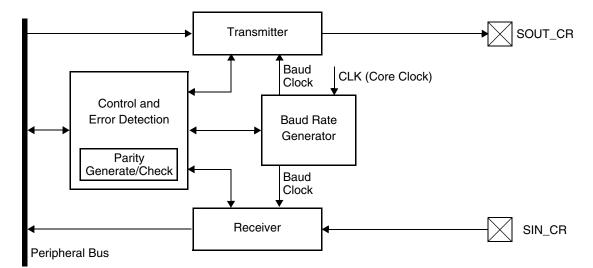

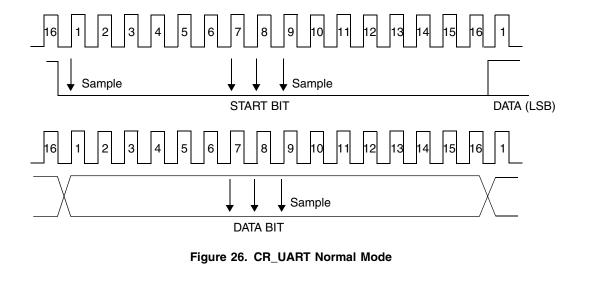

- Core Universal Asynchronous Receiver-Transmitter (CR\_UART) Module

- A full-duplex UART channel

- Programmable baud rate

- Data transfer via interrupt or polling

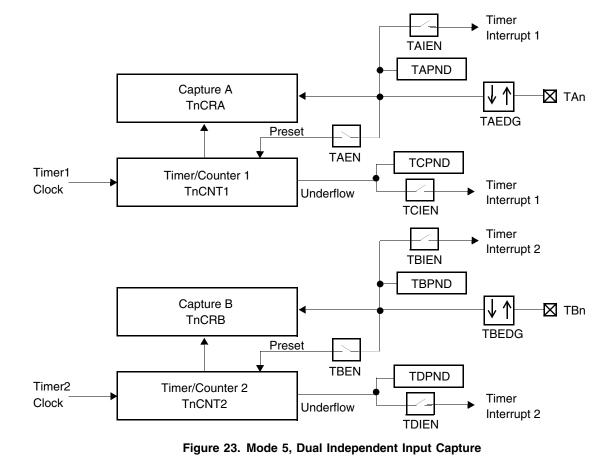

- Two 16-bit Multi-Function Timer (MFT16) Modules: each module has:

- Two 16-bit timers with a 5-bit prescaler

- Pulse Width Modulation (PWM), Capture and Timer/Counter modes

- Capture inputs with programmable edge detection

- An interrupt on compare match

## Features (Continued)

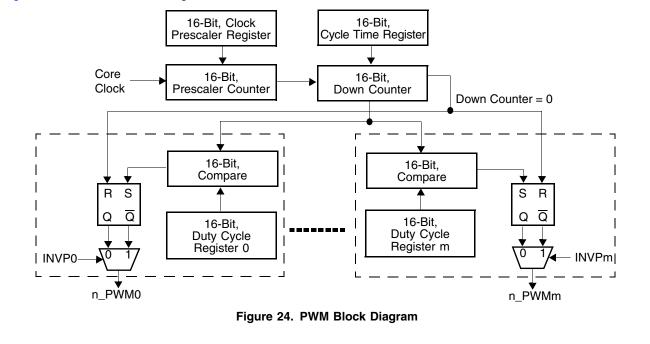

- Two Pulse Width Modulation (PWM) Modules

- Group A\_PWM: two outputs

- Group B\_PWM: one output

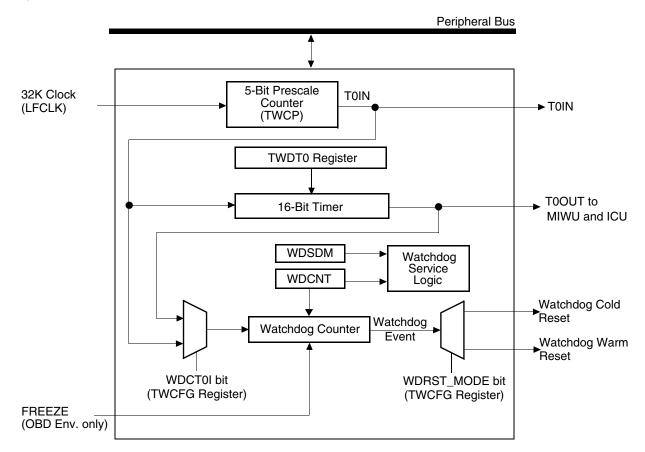

- Timer and Watchdog (TWD)

- 16-bit periodic interrupt timer with 30 μs resolution and 5-bit prescaler for system tick and periodic wake-up tasks

- 8-bit watchdog timer with enable/disable

- "Watchdog occurred" flag

- Two watchdog reset options: warm or cold

- SensorPath<sup>™</sup> Bus Interface

- Single Wire bus master

- Supports up to seven slave devices

- x1, x4 SensorPath clock rate support

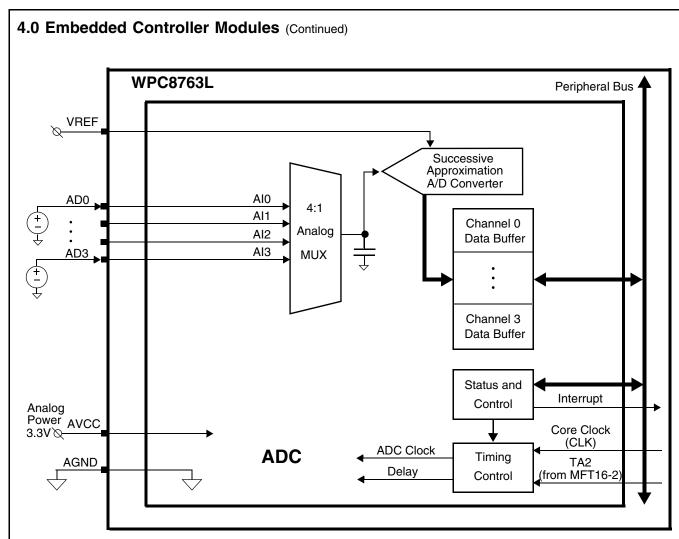

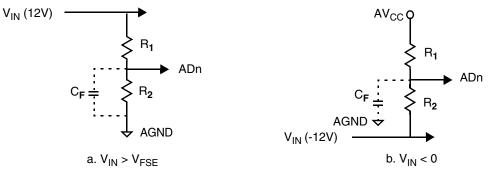

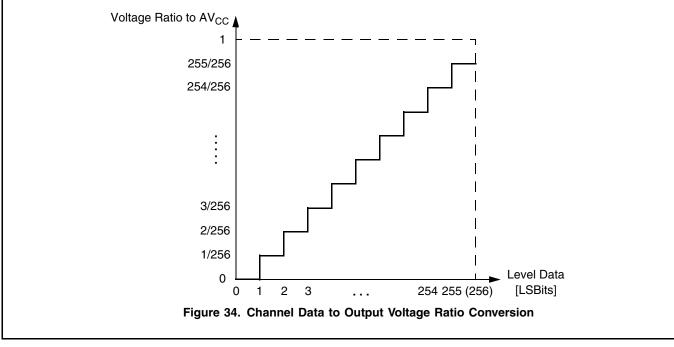

- Analog-to-Digital Converter (ADC)

- Four channels, with 8-bit resolution

- 125 μs conversion time

- External voltage reference

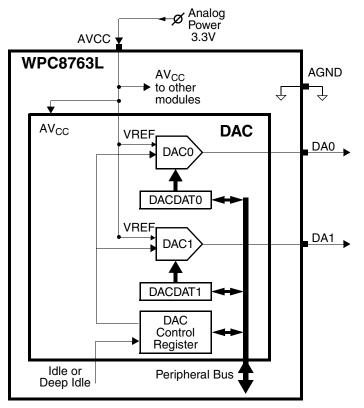

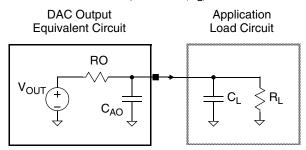

- Digital-to-Analog Converter (DAC)

- Two channels, 8-bit resolution

- 1  $\mu$ s conversion time for 50 pF load

- Full output range from AGND to AVCC

- Development Support

- Interface to debugger via Nexus 5001 interface

- D Physical connection using JTAG

- On-board Debug mode with eight hardware breakpoints

- Embedded memory programing via JTAG with content read protection

- Core Access to Host Modules

- Enabled via lock mechanism

## **Host Function Features**

- Mobile System Wake-Up Control (MSWC)

- Software-controlled off events

- Event routing to IRQ, SMI or PWUREQ

- Supports Microsoft<sup>®</sup> Advanced Power Management (APM) Specifications Revision 1.2, February 1996

— Generates the System Management Interrupt (SMI)

- PC01 Rev 1.0 and ACPI 3.0 Compliant

- PnP configuration register structure

- Flexible resource allocation for all logical devices

- Relocatable base address

- □ 15 IRQ routing options

#### **Clocking, Supply and Package Information**

- Strap Input-Controlled Operating Modes:

- Shared BIOS memory mode

- TRI-STATE<sup>®</sup> mode

- Development mode

- Clocks

- Single 32.768 KHz crystal oscillator

- On-chip high-frequency clock generator

- Either 32.768 KHz or CR16CPlus clock out

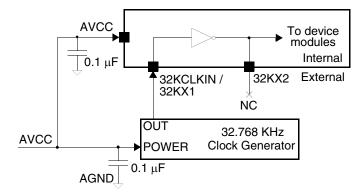

- Testability

- XOR-tree structure includes all device pins (except supply, A/D, D/A, and crystal oscillator pins), selected at power-up by strap inputs

- TRI-STATE device pins, selected at power-up by strap input (TRIS)

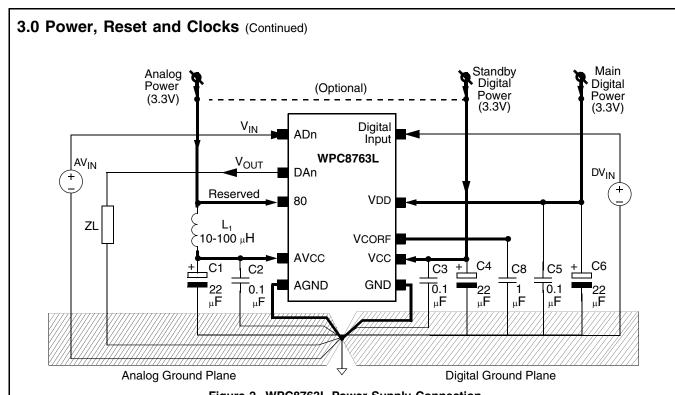

- Power Supply

- 3.3V supply operation

- 5V tolerance and back-drive protection on all pins (except crystal oscillator, A/D, D/A, LPC bus, and SPI flash pins)

- Separate supply for host I/F (V<sub>DD</sub>) and EC functions (V<sub>CC</sub>)

- Reduced power consumption capability

- Software- or hardware-switched power modes:

- Active mode

- □ Active mode executing WAIT

- 🗅 Idle

- Deep Idle

- Automatic wake-up on system events

- Package Options

- 128-pin LQFP package

| <b>Revision Date</b>      | Status                  | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 4, 2006           | Revision 0.96           | First Preliminary Datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| March 12, 2007            | Revision 1.0            | <ol> <li>Datasheet revision. List of changes:         <ol> <li>In cover page and Features:                 <ol> <li>In cover page and Features:</li></ol></li></ol></li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

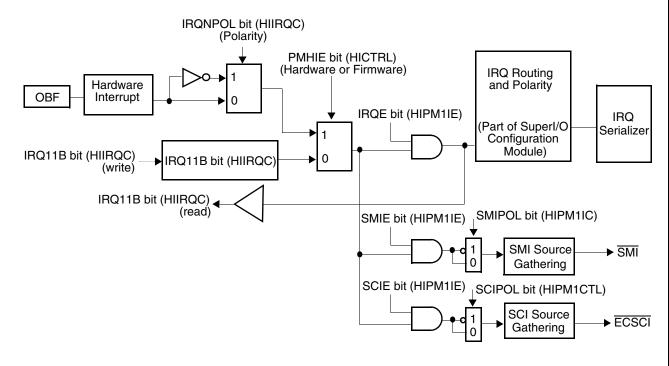

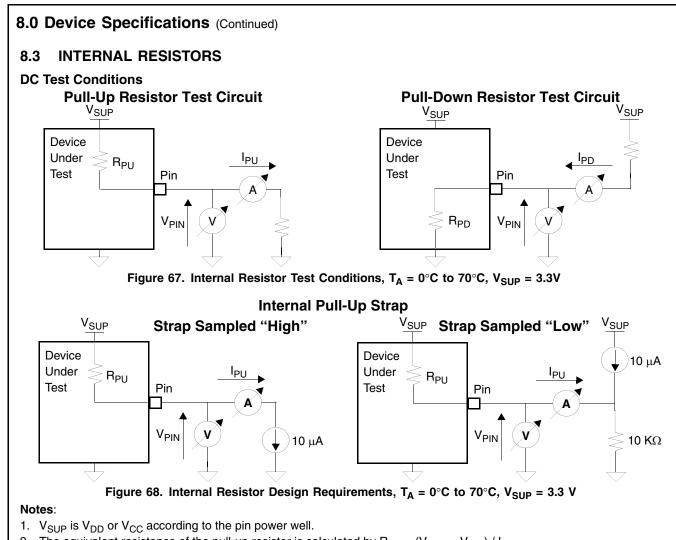

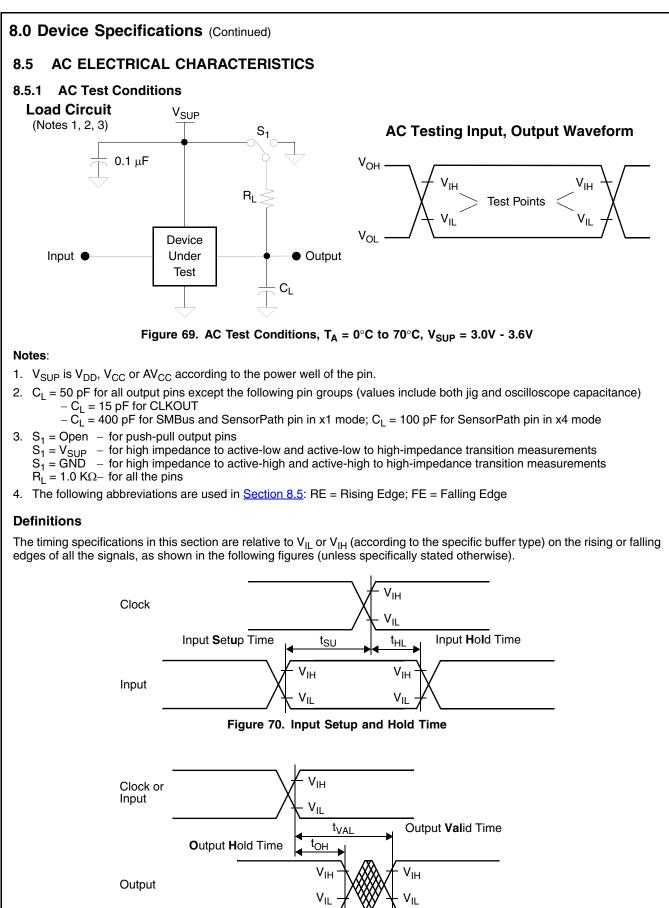

| March 12, 2007<br>(cont.) | Revision 1.0<br>(cont.) | <ul> <li>Datasheet revision. List of changes (cont.):</li> <li>6. In PWM Block Diagram, reversed the "R" and "S" inputs of the flip-flops.</li> <li>7. In SPI, Features, changed the data clock rate to 10 MHz.</li> <li>8. In PM Channels: <ul> <li>8.1 In Enhanced PM Mode, IRQ, ECSCI and SMI Control figure, changed the signal names related to the SMI output.</li> <li>8.2 To the description of SCIPOL bit (HIPMnCTL register) and SMIPOL bit (HIPMnI register), added recommendation to use active low polarity setting.</li> </ul> </li> <li>9. In MSWC Core registers, MSWCTL1 register, added clarification to LPCRSTA bit.</li> <li>10. In Booter Data, Header Contents table, updated footnote #2.</li> <li>11. In Power Supply Current Consumption updated the I<sub>DD</sub>, I<sub>DDLP</sub>, I<sub>CC</sub> and I<sub>CCW</sub> parameter</li> <li>12. In DC Characteristics of Pins: <ul> <li>12.1 Added Leakage Current section.</li> <li>12.2 In Notes and Exceptions, updated item #1 and removed items #4 and #5 (the are replaced by the new Leakage Current section).</li> </ul> </li> <li>13. In Internal Resistors, changed the Min. Max. values for the R<sub>PU80</sub> and R<sub>PD80</sub> parameters</li> <li>14. In DAC Characteristics: <ul> <li>14.1 Changed the values of output resistance (R<sub>S</sub>).</li> </ul> </li> </ul> |

| Tabl  | e of C   | ontent           | S                                                    |     |

|-------|----------|------------------|------------------------------------------------------|-----|

| Featu | ires     |                  |                                                      | 2   |

| Datas | sheet Re | evision R        | ecord                                                | 4   |

| 1.0   | Intro    | duction          |                                                      |     |

|       | 1.1      | GENER            | AL DESCRIPTION                                       | .18 |

|       |          | 1.1.1            | System Connections                                   | 18  |

|       |          | 1.1.2            | Power Management                                     | 18  |

|       | 1.2      | INTERN           | IAL ARCHITECTURE                                     | 18  |

|       | 1.3      | OPERA            | TING ENVIRONMENTS                                    | .19 |

|       |          | 1.3.1            | IRE Environment                                      | .19 |

|       |          | 1.3.2            | OBD Environment                                      | 19  |

|       | 1.4      | MEMOF            | אר MAP                                               | .19 |

|       |          | 1.4.1            | Core Address Domain Memory Map                       | 19  |

|       |          | 1.4.2            | Host Address Domain Memory Map                       | 20  |

|       |          | 1.4.3            | Core Access to Host Modules                          | 20  |

| 2.0   | Signa    | al/Pin D         | escription and Configuration                         |     |

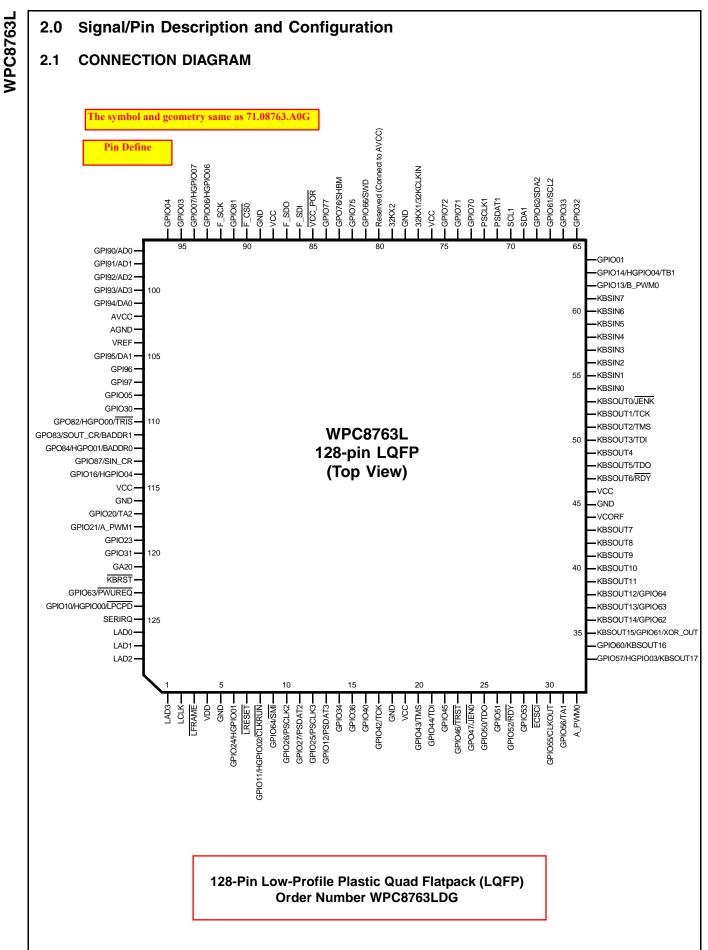

|       | 2.1      | CONNE            | CTION DIAGRAM                                        | 22  |

|       | 2.2      | BUFFEF           | R TYPES                                              | 23  |

|       | 2.3      | PIN MU           | LTIPLEXING                                           | 23  |

|       | 2.4      | DETAIL           | ED SIGNAL/PIN DESCRIPTIONS                           | .25 |

|       |          | 2.4.1            | Host Interface                                       | 25  |

|       |          | 2.4.2            | SPI Flash Interface                                  | 26  |

|       |          | 2.4.3            | Internal Keyboard Scan                               | 26  |

|       |          | 2.4.4            | General-Purpose I/O (GPIO)                           | 27  |

|       |          | 2.4.5            | Host General-Purpose I/O (HGPIO)                     | 28  |

|       |          | 2.4.6            | Analog Interface                                     | 28  |

|       |          | 2.4.7            | PS/2 Interface                                       |     |

|       |          | 2.4.8            | SMBus Interface                                      |     |

|       |          | 2.4.9            | Timers and PWM                                       |     |

|       |          | 2.4.10           | SensorPath Interface                                 |     |

|       |          | 2.4.11           | CR_UART                                              |     |

|       |          | 2.4.12           |                                                      |     |

|       |          | 2.4.13           | Miscellaneous                                        |     |

|       |          | 2.4.14<br>2.4.15 | Clocks                                               |     |

|       |          | 2.4.15           | Power and Ground                                     |     |

|       | 0.5      |                  |                                                      |     |

|       | 2.5      |                  | IAL PULL-UP AND PULL-DOWN RESISTORS                  |     |

|       |          | 2.5.1<br>2.5.2   | Internal Keyboard Scan<br>General-Purpose I/O (GPIO) |     |

|       |          | 2.5.2            | Host General-Purpose I/O (HGPIO)                     |     |

|       |          | 2.5.3            | PS/2 Interface                                       |     |

|       |          | 2.5.5            | SMBus Interface                                      |     |

|       |          | 2.5.6            | Timers                                               |     |

|       |          | 2.5.7            | SensorPath Interface                                 |     |

WPC8763L

5

| Tab | le of ( | Content  | <b>ts</b> (Continued)                                                                            |    |

|-----|---------|----------|--------------------------------------------------------------------------------------------------|----|

|     |         | 2.5.8    | JTAG                                                                                             |    |

|     |         | 2.5.9    | Strap Configuration and Testing                                                                  |    |

|     | 2.6     | SVSTE    | EM CONFIGURATION                                                                                 |    |

|     | 2.0     | 2.6.1    | System Configuration Registers                                                                   |    |

|     |         | 2.0.1    | Register Map                                                                                     |    |

|     |         |          | Device Control Register (DEVCNT)                                                                 |    |

|     |         |          | Straps Status Register (STRPST)                                                                  |    |

|     |         |          | Reset Control and Status Register (RSTCTL)                                                       |    |

|     |         |          | Device Alternate Function 0 Register (DEVALT0)                                                   |    |

|     |         |          | Device Alternate Function 1 Register (DEVALT1)                                                   |    |

|     |         |          | Device Alternate Function 2 Register (DEVALT2)                                                   |    |

|     |         |          | Device Alternate Function 3 Register (DEVALT3)<br>Device Alternate Function 4 Register (DEVALT4) |    |

|     |         |          | Device Alternate Function 5 Register (DEVALT4)                                                   |    |

|     |         |          | Device Alternate Function 6 Register (DEVALT6)                                                   |    |

|     |         |          | Device Alternate Function 7 Register (DEVALT7)                                                   |    |

|     |         |          | Device Alternate Function 8 Register (DEVALT8)                                                   |    |

|     |         |          | Device Alternate Function 9 Register (DEVALT9)                                                   |    |

|     |         |          | GPIO Event Select 1 Register (GES1)                                                              |    |

|     |         |          | Device Pull-Up Enable 0 Register (DEVPU0)                                                        |    |

|     |         |          | Device Pull-Up Enable 1 Register (DEVPU1)                                                        |    |

| 3.0 | Pow     | ver, Res | set and Clocks                                                                                   |    |

|     | 3.1     | POWE     | R                                                                                                |    |

|     |         | 3.1.1    | Power Planes                                                                                     |    |

|     |         | 3.1.2    | Power States                                                                                     |    |

|     |         | 3.1.3    | Power Connection and Layout Guidelines                                                           |    |

|     | 3.2     | RESET    | ۲ SOURCES AND TYPES                                                                              |    |

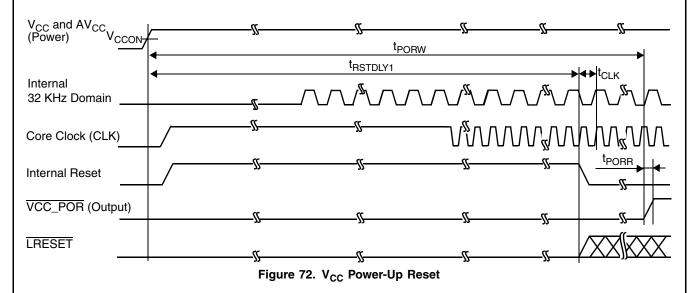

|     |         | 3.2.1    | V <sub>CC</sub> Power-Up Reset                                                                   |    |

|     |         | 3.2.2    | VCC POR Input Reset                                                                              |    |

|     |         | 3.2.3    | Watchdog Cold Reset and Debugger Cold Reset                                                      |    |

|     |         | 324      | Watchdog Warm Reset and Debugger Warm Reset                                                      |    |

|     |         | 3.2.5    | Valendeg Warn reset and Debugger Warn reset                                                      |    |

|     |         | 3.2.5    | Host Hardware Reset                                                                              |    |

|     |         |          | VCC POR Generation                                                                               |    |

|     |         | 3.2.7    | _                                                                                                |    |

|     | 3.3     | CLOC     | COMAINS                                                                                          |    |

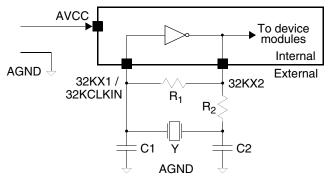

|     |         | 3.3.1    | 32 KHz Clock Domain Generation                                                                   |    |

|     |         |          | Internal Oscillator                                                                              | -  |

|     |         |          | External Oscillator                                                                              |    |

|     | 3.4     | TESTA    | ABILITY SUPPORT                                                                                  |    |

|     |         | 3.4.1    | ICT                                                                                              |    |

|     |         | 3.4.2    | XOR-Tree Testing                                                                                 | 53 |

| 4.0 | Emb     | bedded   | Controller Modules                                                                               |    |

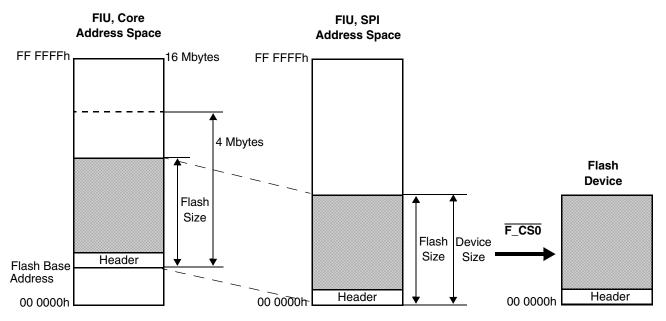

|     | 4.1     | FLASH    | I INTERFACE UNIT (FIU)                                                                           |    |

| 1   |         | 4.1.1    | Overview                                                                                         |    |

| 1   |         | 4.1.2    | FIU Core Bus Interface                                                                           |    |

|     |         | 4.1.3    | SPI Flash Interface                                                                              |    |

| 1   |         |          |                                                                                                  |    |

WPC8763L

| ~        |

|----------|

| <u> </u> |

| σ        |

| C        |

| $\infty$ |

| N        |

| ົ        |

| ω        |

|          |

| Table of C | ontent | ts (Continued)                                                                      |    |

|------------|--------|-------------------------------------------------------------------------------------|----|

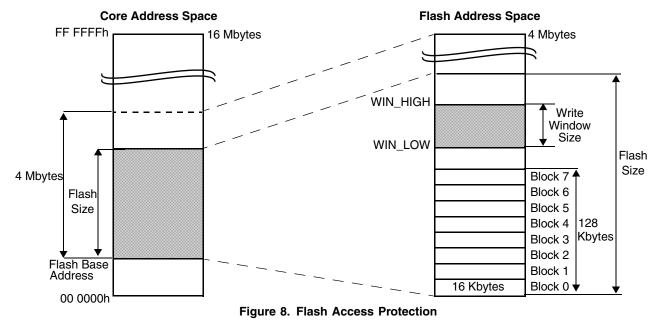

|            | 4.1.4  | Access Protection                                                                   | 57 |

|            | 4.1.5  | Low Power Support                                                                   | 58 |

|            | 4.1.6  | FIU Registers                                                                       |    |

|            |        | FIU Configuration Register (FIU_CFG)                                                |    |

|            |        | Burst Configuration Register (BURST_CFG)                                            |    |

|            |        | FIU Response Configuration Register (RESP_CFG)                                      |    |

|            |        | Core Firmware Boot Block Protection Register (CFBB_PROT)                            | 60 |

|            |        | Flash Access Window 3-1, Low Limit Registers (FWIN3-1_LOW)                          |    |

|            |        | Flash Access Window 3-1, High Limit Register (FWIN3-1_HIGH)                         |    |

|            |        | Protection Lock Register (PROT_LOCK)                                                |    |

|            |        | Protection and Lock Clear Register (PROT_CLEAR)                                     |    |

|            |        | SPI Flash Configuration Register (SPI_FL_CFG)                                       |    |

|            |        | UMA Code Byte Register (UMA_CODE)                                                   |    |

|            |        | UMA Address Byte 2-0 Register (UMA_AB2-0)<br>UMA Data Byte 3-0 Register (UMA_DB3-0) |    |

|            |        | UMA Control and Status Register (UMA_CTS)                                           |    |

|            |        | UMA Extended Control and Status Register (UMA_ECTS)                                 |    |

|            | 4.1.7  | Usage Hints                                                                         |    |

|            |        | 5                                                                                   |    |

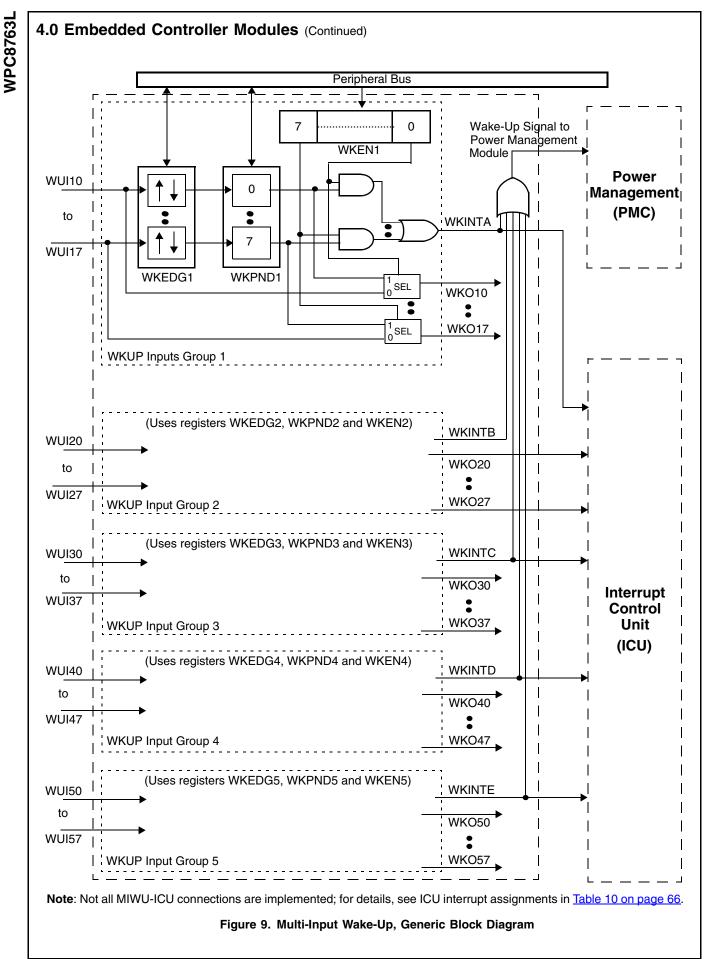

| 4.2        |        | -INPUT WAKE-UP (MIWU)                                                               |    |

|            | 4.2.1  | Features                                                                            |    |

|            | 4.2.2  | Operation                                                                           |    |

|            | 4.2.3  | MIWU Registers                                                                      | 69 |

|            |        | Edge Detection Register (WKEDG1)                                                    | 70 |

|            |        | Edge Detection Register (WKEDG2)                                                    |    |

|            |        | Edge Detection Register (WKEDG3)                                                    |    |

|            |        | Edge Detection Register (WKEDG4)                                                    |    |

|            |        | Edge Detection Register (WKEDG5)                                                    |    |

|            |        | Pending Register (WKPND1)<br>Pending Register (WKPND2)                              |    |

|            |        | Pending Register (WKPND3)                                                           |    |

|            |        | Pending Register (WKPND4)                                                           |    |

|            |        | Pending Register (WKPND5)                                                           |    |

|            |        | Enable Register (WKEN1)                                                             |    |

|            |        | Enable Register (WKEN2)                                                             | 71 |

|            |        | Enable Register (WKEN3)                                                             |    |

|            |        | Enable Register (WKEN4)                                                             |    |

|            |        | Enable Register (WKEN5)                                                             |    |

|            |        | Pending Clear Register (WKPCL1)                                                     |    |

|            |        | Pending Clear Register (WKPCL2)                                                     |    |

|            |        | Pending Clear Register (WKPCL3)<br>Pending Clear Register (WKPCL4)                  |    |

|            |        | Pending Clear Register (WKPCL4)<br>Pending Clear Register (WKPCL5)                  |    |

|            | 4.2.4  |                                                                                     |    |

|            |        | Usage Hints                                                                         |    |

| 4.3        | INTER  | RUPT CONTROL UNIT (ICU)                                                             |    |

|            | 4.3.1  | Features                                                                            | 74 |

|            | 4.3.2  | Non-Maskable Interrupt (NMI)                                                        | 74 |

|            | 4.3.3  | Maskable Interrupts                                                                 | 75 |

|            | 4.3.4  | ICU Registers                                                                       |    |

|            |        | Interrupt Vector Register (IVCT)                                                    |    |

|            |        | NMI Status Register (NMISTAT)                                                       |    |

|            |        | External NMI Interrupt Control and Status Register (EXNMI)                          |    |

| S      |

|--------|

| 9      |

| $\sim$ |

| ω      |

| C      |

| Ā      |

| >      |

| >      |

| Table of | Conten  | <b>ts</b> (Continued)                                                         |     |

|----------|---------|-------------------------------------------------------------------------------|-----|

|          |         | Interrupt Status Register 0 (ISTAT0)                                          |     |

|          |         | Interrupt Status Register 1 (ISTAT1)                                          |     |

|          |         | Interrupt Enable and Mask Register 0 (IENAM0)                                 | 79  |

|          |         | Interrupt Enable and Mask Register 1 (IENAM1)                                 |     |

|          |         | Edge Interrupt Clear Register 0 (IECLR0)                                      |     |

|          |         | Edge Interrupt Clear Register 1 (IECLR1)                                      | 80  |

|          | 4.3.5   | Usage Hints                                                                   | 80  |

| 4.4      | GENE    | RAL-PURPOSE I/O (GPIO) PORTS                                                  | 81  |

|          | 4.4.1   | Features                                                                      | 81  |

|          | 4.4.2   | GPIO Port Functional Description                                              | 81  |

|          | 4.4.3   | Non-Standard GPIO Ports                                                       |     |

|          | 4.4.4   | GPIO Ports Memory Map                                                         |     |

|          | 4.4.5   | GPIO Port Registers                                                           |     |

|          |         | Port GPIOx Data Out Register (PxDOUT)                                         |     |

|          |         | Port GPIOx Data In Register (PxDIN)                                           |     |

|          |         | Port GPIOx Direction Register (PxDIR)                                         |     |

|          |         | Port GPIOx Pull-Up or Pull-Down Enable Register (PxPULL)                      |     |

|          |         | Port GPIOx Pull-Up/Down Selection Register (PxPUD)                            |     |

|          |         | Port GPIOx Drive Enable by VDD Present (PxENVDD)                              |     |

|          | 4.4.6   | Power-Up Configuration                                                        | 85  |

| 4.5      | KEYBO   | DARD SCAN                                                                     |     |

|          | 4.5.1   | Overview                                                                      |     |

|          | 4.5.2   | Keyboard Scan Registers                                                       |     |

|          |         | Keyboard Scan In Register (KBSIN)                                             |     |

|          |         | Keyboard Scan In Pull-Up Enable Register (KBSINPU)                            |     |

|          |         | Keyboard Scan Out 0 Register (KBSOUT0)                                        |     |

|          |         | Keyboard Scan Out 1 Register (KBSOUT1)                                        |     |

| 4.6      |         | EM GLUE FUNCTIONS                                                             |     |

|          | 4.6.1   | GPIO Echo Function                                                            |     |

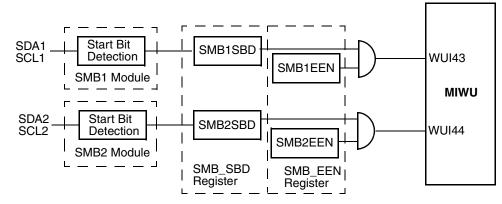

|          | 4.6.2   | SMBus Wake-Up Support                                                         |     |

|          | 4.6.3   | System Glue Registers                                                         |     |

|          |         | Input to Output Echo Enable Register (IOEE)                                   |     |

|          |         | SMBus Start Bit Detection Register (SMB_SBD)                                  |     |

|          |         | SMBus Event Enable Register (SMB_EEN)                                         | 90  |

| 4.7      | PS/2 II | NTERFACE                                                                      |     |

|          | 4.7.1   | Features                                                                      | -   |

|          | 4.7.2   | General Description                                                           |     |

|          | 4.7.3   | Operating With the Shift Mechanism Disabled                                   | 92  |

|          | 4.7.4   | Operating With the Shift Mechanism Enabled                                    | 93  |

|          | 4.7.5   | PS/2 Interface Registers                                                      |     |

|          |         | PS/2 Data Register (PSDAT)                                                    |     |

|          |         | PS/2 Status Register (PSTAT)                                                  |     |

|          |         | PS/2 Control Register (PSCON)                                                 |     |

|          |         | PS/2 Output Signal Register (PSOSIG)                                          |     |

|          |         | PS/2 Input Signal Register (PSISIG)<br>PS/2 Interrupt Enable Register (PSIEN) |     |

| 4.0      | N 41 11 |                                                                               |     |

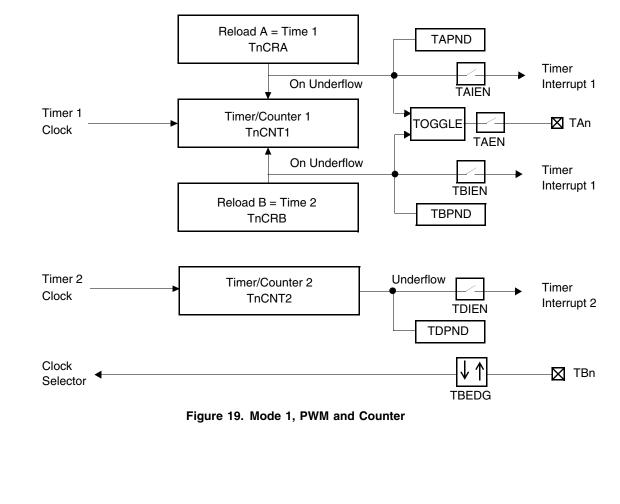

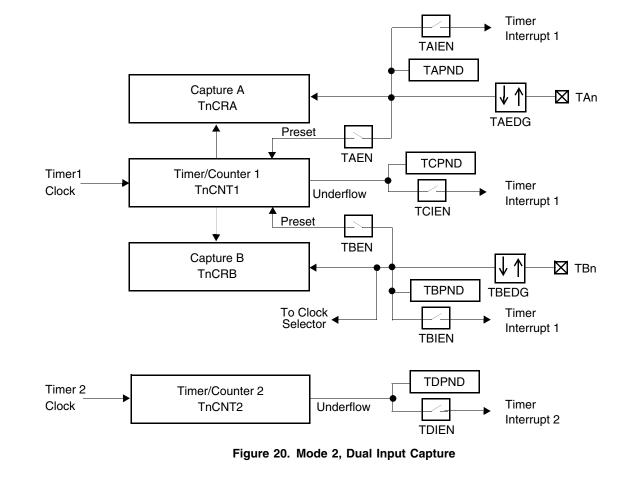

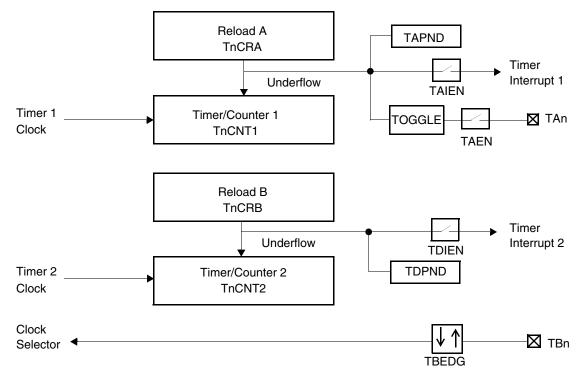

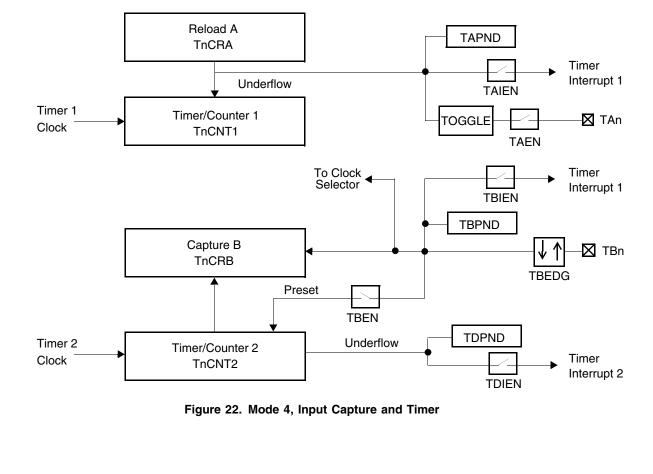

| 4.8      |         | I-FUNCTION 16-BIT TIMER (MFT16)                                               |     |

|          | 4.8.1   | Features                                                                      | 101 |

|          |         |                                                                               |     |

| Ū        |

|----------|

| õ        |

| 328      |

| <u>ü</u> |

| Table of C | ontent | S (Continued)                                                          |     |

|------------|--------|------------------------------------------------------------------------|-----|

|            | 4.8.2  | Clock Source Unit                                                      | 102 |

|            | 4.8.3  | Timer/Counter and Control Unit                                         |     |

|            | 4.8.4  | Compare Function                                                       | 109 |

|            | 4.8.5  | Timer Interrupts                                                       |     |

|            | 4.8.6  | Timer I/O Functions                                                    |     |

|            | 4.8.7  | Operation in Development System                                        |     |

|            | 4.8.8  | MFT16 Registers                                                        |     |

|            |        | Timer/Counter Register 1 (TnCNT1)                                      | 111 |

|            |        | Reload/Capture Register A (TnCRA)                                      |     |

|            |        | Reload/Capture Register B (TnCRB)                                      |     |

|            |        | Timer/Counter Register 2 (TnCNT2)<br>Clock Prescaler Register (TnPRSC) |     |

|            |        | Clock Unit Control Register (Tri TISC)                                 |     |

|            |        | Timer Mode Control Register (TnMCTRL)                                  |     |

|            |        | Timer Interrupt Control Register (TnICTRL)                             |     |

|            |        | Timer Interrupt Clear Register (TnICLR)                                |     |

|            |        | Timer Interrupt Enable Register (TnIEN)<br>Compare Register A (TnCPA)  |     |

|            |        | Compare Register B (ThCPB)                                             |     |

|            |        | Compare Configuration Register (TnCPCFG)                               |     |

| 4.9        | PULSE  | WIDTH MODULATOR (PWM)                                                  | 118 |

|            | 4.9.1  | Features                                                               |     |

|            | 4.9.2  | Functional Description                                                 | 118 |

|            | 4.9.3  | Cycle Time and Duty Cycle Calculation                                  | 119 |

|            | 4.9.4  | Power Modes                                                            | 119 |

|            | 4.9.5  | PWM Registers                                                          | 119 |

|            |        | Clock Prescaler Register (PRSCn)                                       | 119 |

|            |        | Cycle Time Register (CTRn)                                             |     |

|            |        | PWM Control Register (PWMCTLn)                                         |     |

|            |        | Duty Cycle Registers 0 to 1 (DCRmn)                                    |     |

| 4.10       |        | JNIVERSAL ASYNCHRONOUS RECEIVER-TRANSMITTER (CR_UART)                  |     |

|            | 4.10.1 | Features                                                               |     |

|            | 4.10.2 | Functional Overview                                                    |     |

|            | 4.10.3 | Functional Description                                                 |     |

|            |        | Normal Mode Attention Mode                                             |     |

|            |        | Diagnostic Mode                                                        |     |

|            |        | Frame Format Selection                                                 |     |

|            |        | Baud Rate Generator                                                    |     |

|            |        | Interrupts<br>Break Generation and Detection                           |     |

|            |        | Parity Generation and Detection                                        |     |

|            |        | Freeze Mode                                                            |     |

|            | 4.10.4 | CR_UART Registers                                                      | 127 |

|            |        | Transmit Data Buffer Register (UTBUF)                                  | 127 |

|            |        | Receive Data Buffer Register (URBUF)                                   |     |

|            |        | Interrupt Control Register (UICTRL)                                    |     |

|            |        | Status Register (USTAT)<br>Frame Select Register (UFRS)                |     |

|            |        | Mode Select Register (UMDSL)                                           |     |

|            |        | - · · /                                                                |     |

| Table of C | Content | S (Continued)                                                                      |  |

|------------|---------|------------------------------------------------------------------------------------|--|

|            |         | Baud Rate Divisor Register (UBAUD)                                                 |  |

|            |         | Baud Rate Prescaler Register (UPSR)                                                |  |

|            | 4.10.5  | Usage Hints                                                                        |  |

|            |         | Calculating the Baud Rate                                                          |  |

| 4.11       | TIMER   | AND WATCHDOG (TWD)                                                                 |  |

|            | 4.11.1  | Features                                                                           |  |

|            | 4.11.2  | Functional Description                                                             |  |

|            | 4.11.3  | TWD Registers                                                                      |  |

|            |         | Timer and Watchdog Configuration Register (TWCFG)                                  |  |

|            |         | Timer and Watchdog Clock Prescaler Register (TWCP)<br>TWD Timer 0 Register (TWDT0) |  |

|            |         | TWD Timer of Register (TWDTo)                                                      |  |

|            |         | Watchdog Count Register (WDCNT)                                                    |  |

|            |         | Watchdog Service Data Match Register (WDSDM)                                       |  |

|            | 4.11.4  | Usage Hints                                                                        |  |

| 4.12       | ANALO   | G TO DIGITAL CONVERTER (ADC)                                                       |  |

|            | 4.12.1  | Features                                                                           |  |

|            | 4.12.2  | Functional Description                                                             |  |

|            | 4.12.3  | Voltage Measurement                                                                |  |

|            | 4.12.4  | ADC Operation                                                                      |  |

|            | 4.12.5  | ADC Registers                                                                      |  |

|            |         | ADC Status Register (ADCSTS)                                                       |  |

|            |         | ADC Configuration Register (ADCCNF)                                                |  |

|            |         | ADC Timing Control Register (ATCTL)<br>ADC Single Channel Address (ASCADD)         |  |

|            |         | ADC Scan Channels Select (ADCCS)                                                   |  |

|            |         | Channel n Data Buffer (CHNnDAT)                                                    |  |

|            | 4.12.6  | Usage Hints                                                                        |  |

| 4.13       | DIGITA  | L TO ANALOG CONVERTER (DAC)                                                        |  |

|            | 4.13.1  | Features                                                                           |  |

|            | 4.13.2  | Functional Description                                                             |  |

|            | 4.13.3  | D/A Conversion                                                                     |  |

|            | 4.13.4  | Operation                                                                          |  |

|            | 4.13.5  | DAC Registers                                                                      |  |

|            |         | DAC Control Register (DACCTRL)                                                     |  |

|            |         | DAC Data Channel 0-1 Registers (DACDAT0-1)                                         |  |

|            | 4.13.6  | Usage Hints                                                                        |  |

| 4.14       |         | S (SMB) INTERFACE                                                                  |  |

|            | 4.14.1  | Features                                                                           |  |

|            | 4.14.2  | Functional Description                                                             |  |

|            | 4.14.3  | Master Mode                                                                        |  |

|            | 4.14.4  | Slave Mode                                                                         |  |

|            | 4.14.5  | Power-Down                                                                         |  |

|            | 4.14.6  | SDA and SCL Pin Configuration                                                      |  |

|            | 4.14.7  | SMB Clock Frequency Configuration                                                  |  |

|            | 4.14.8  | SMB Registers                                                                      |  |

|            |         | SMB Serial Data Register (SMBnSDA)                                                 |  |

WPC8763L

| Table of C | ontents | S (Continued)                                                                |     |

|------------|---------|------------------------------------------------------------------------------|-----|

|            |         | SMB Status Register (SMBnST)                                                 |     |

|            |         | SMB Control Status Register (SMBnCST)                                        |     |

|            |         | SMB Control Register 1 (SMBnCTL1)                                            |     |

|            |         | SMB Own Address Register (SMBnADDR1, SMBnADDR2)                              |     |

|            |         | SMB Control Register 2 (SMBnCTL2)                                            |     |

|            |         | SMB Control Register 3 (SMBnCTL3)                                            |     |

|            | 4.14.9  | Usage Hints                                                                  |     |

| 4.15       | SENSO   | RPATH BUS INTERFACE (SPB)                                                    | 167 |

|            | 4.15.1  | Overview                                                                     | 167 |

|            | 4.15.2  | Functional Description                                                       | 167 |

|            | 4.15.3  | SPB Module Registers                                                         | 169 |

|            |         | Register Map                                                                 |     |

|            |         | SPB Control Register (SPB_CTL)                                               | 170 |

|            |         | SPB Bus Status Register (SPB_BUST)                                           |     |

|            |         | SPB Wake Status Register (SPB_WKST)                                          |     |

|            |         | SPB Internal Address Register (SPB_INTA)                                     |     |

|            |         | SPB Data Byte 0 Register (SPB_DAT_0)                                         |     |

|            |         | SPB Data Byte 1 Register (SPB_DAT_1)                                         |     |

|            |         | SPB Data Byte 2 Register (SPB_DAT_2)<br>SPB Data Byte 3 Register (SPB_DAT_3) |     |

|            |         | SPB Configuration Register (SPB_CFG)                                         |     |

|            |         | SPB Clock Configuration Register (CLK_CFG)                                   |     |

| 4.16       |         | IP RAM                                                                       |     |

|            |         |                                                                              |     |

| 4.17       |         | IP ROM                                                                       |     |

| 4.18       |         | R MANAGEMENT CONTROLLER (PMC)                                                |     |

|            | 4.18.1  | Features                                                                     | 177 |

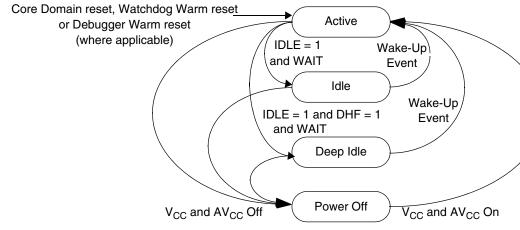

|            | 4.18.2  | The Core Domain Power Modes                                                  |     |

|            | 4.18.3  | Switching Between Power Modes                                                | 178 |

|            | 4.18.4  | PMC Registers                                                                |     |

|            |         | Power Management Controller Status Register (PMCSR)                          | 179 |

|            | 4.18.5  | Usage Hints                                                                  |     |

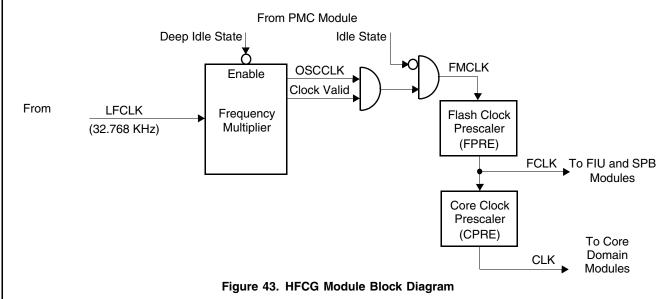

| 4.19       | HIGH-F  | REQUENCY CLOCK GENERATOR (HFCG)                                              |     |

|            | 4.19.1  | Features                                                                     | 181 |

|            | 4.19.2  | Functional Description                                                       | 181 |

|            | 4.19.3  | HFCG Registers                                                               |     |

|            |         | HFCG Control Register (HFCGCTRL)                                             |     |

|            |         | HFCGM Low Value Register (HFCGML)                                            |     |

|            |         | HFCGM High Value Register (HFCGMH)                                           |     |

|            |         | HFCGN Value Register (HFCGN)<br>HFCG Prescaler Register (HFCGP)              |     |

|            | 4.19.4  | Usage Hints                                                                  |     |

| 4.00       | -       | C C C C C C C C C C C C C C C C C C C                                        |     |

| 4.20       | 4.20.1  | OPMENT AND DEBUG SUPPORT                                                     |     |

|            |         | Debugger Interface (SDI+)                                                    |     |

|            | 4.20.2  | Debugger Reset Types                                                         |     |

|            | 4.20.3  | Freezing Events                                                              |     |

|            | 4.20.4  | Debugger Interface, Core Registers                                           |     |

|            |         | Register Map Debugger Interface JTAG Device ID (DBG_DID)                     |     |

|            |         |                                                                              |     |

11

| က |

|---|

| ശ |

|   |

| œ |

| Ö |

| é |

| < |

|   |

| Tabl | le of ( | Content        | S (Continued)                                                                                               |     |

|------|---------|----------------|-------------------------------------------------------------------------------------------------------------|-----|

|      |         |                | Debug Freeze Enable 1 Register (DBGFRZEN1)                                                                  | 188 |

|      |         | 4.20.5         | Usage Hints                                                                                                 |     |

|      | 4.21    | COBE           | BUS WATCHER                                                                                                 | 190 |

|      | 7.61    | 4.21.1         | General Description                                                                                         |     |

|      |         | 4.21.2         | Functional Description                                                                                      |     |

|      |         | 4.21.3         | Core Bus Watcher Registers                                                                                  |     |

|      |         | 4.21.0         | Register Map                                                                                                |     |

|      |         |                | Watcher Address Register (WADR)                                                                             |     |

|      |         |                | Watcher Status Register (WSTAT)                                                                             |     |

|      |         |                | Watcher Interrupt Clear Register (WICLR)                                                                    |     |

|      |         |                | Watcher Control Register (WCNTRL)                                                                           |     |

| 5.0  | Hos     | t-to-EC        | Interface Modules                                                                                           |     |

|      | 5.1     | KEYBC          | DARD AND MOUSE CONTROLLER INTERFACE                                                                         | 193 |

|      |         | 5.1.1          | Features                                                                                                    | 193 |

|      |         | 5.1.2          | General Description                                                                                         | 193 |

|      |         | 5.1.3          | Host Interface Registers                                                                                    | 196 |

|      |         |                | Data Out Buffer Register (DBBOUT, Legacy 60h)                                                               |     |

|      |         |                | Status Register (STATUS, Legacy 64h)                                                                        |     |

|      |         |                | Data In Buffer Register (DBBIN, Legacy 60h)                                                                 |     |

|      |         |                | Command In Buffer Register (COMAND, Legacy 64h)                                                             |     |

|      |         | 5.1.4          | Core Interface Registers                                                                                    |     |

|      |         |                | Core Interface Register Map                                                                                 |     |

|      |         |                | Host Interface Control Register (HICTRL)<br>Host Interface IRQ Control Register (HIIRQC)                    |     |

|      |         |                | Host Interface Keyboard/Mouse Status Register (HIKMST)                                                      |     |

|      |         |                | Host Interface Keyboard Data Out Buffer Register (HIKDO)                                                    |     |

|      |         |                | Host Interface Mouse Data Out Buffer Register (HIMDO)                                                       |     |

|      |         |                | Host Interface Keyboard/Mouse Data In Buffer Register (HIKMDI)                                              |     |

|      | 5.2     | POWE           | R MANAGEMENT (PM) CHANNELS                                                                                  |     |

|      |         | 5.2.1          | Features                                                                                                    |     |

|      |         | 5.2.2          | General Description                                                                                         |     |

|      |         |                | Host Addresses                                                                                              |     |

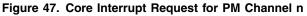

|      |         |                | Core Interrupts                                                                                             |     |

|      |         |                | Host Interrupt Generation Modes                                                                             |     |

|      |         |                | Status Read<br>Host Data Read from Host Interface Power Management Channel                                  |     |

|      |         | 5.2.3          | Host PM Registers                                                                                           |     |

|      |         | 5.2.3<br>5.2.4 | Core PM Registers                                                                                           |     |

|      |         | 5.2.4          | Core PM Register Map                                                                                        |     |

|      |         |                | Host Interface PM n Status Register (HIPMnST)                                                               |     |

|      |         |                | Host Interface PM n Data Out Buffer (HIPMnDO)                                                               |     |

|      |         |                | Host Interface PM n Data In Buffer (HIPMnDI)                                                                |     |

|      |         |                | Host Interface PM n Data Out Buffer with SCI (HIPMnDOC)                                                     |     |

|      |         |                | Host Interface PM n Data Out Buffer with SMI (HIPMnDOM)                                                     |     |

|      |         |                | Host Interface PM n Data In Buffer with SCI (HIPMnDIC)                                                      |     |

|      |         |                | Host Interface PM n Control Register (HIPMnCTL)<br>Host Interface PM n Interrupt Control Register (HIPMnIC) |     |

|      |         |                | Host Interface PM n Interrupt Enable Register (HIPMnIE)                                                     |     |

|      | 5.3     | CORF           | ACCESS TO HOST MODULES                                                                                      |     |

|      | 0.0     | SOUL           |                                                                                                             |     |

Table of Contents (Continued)

| Ş  |

|----|

| Õ  |

| Ô, |

| 6  |

| ٽ  |

|    |

|                 | 5.3.1  | Core Access to Host Module Registers                                                                                           | 212        |

|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------|------------|

|                 |        | Indirect Host I/O Address Register (IHIOA)                                                                                     | 212        |

|                 |        | Indirect Host Data Register (IHD)                                                                                              |            |

|                 |        | Lock Host Access Register (LKSIOHA)                                                                                            |            |

|                 |        | Access Lock Violation Register (SIOLV)                                                                                         |            |

|                 |        | Core to Host Modules Access Enable Register (CRSMAE)<br>Module Control Register (SIBCTRL)                                      |            |

| 5.4             | SHARE  | D MEMORY (SHM)                                                                                                                 |            |

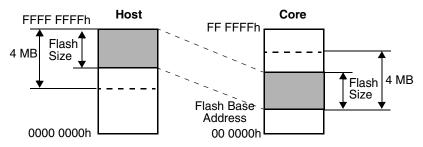

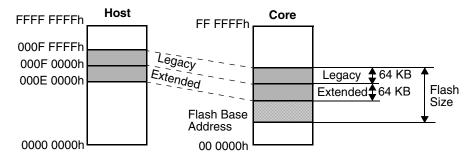

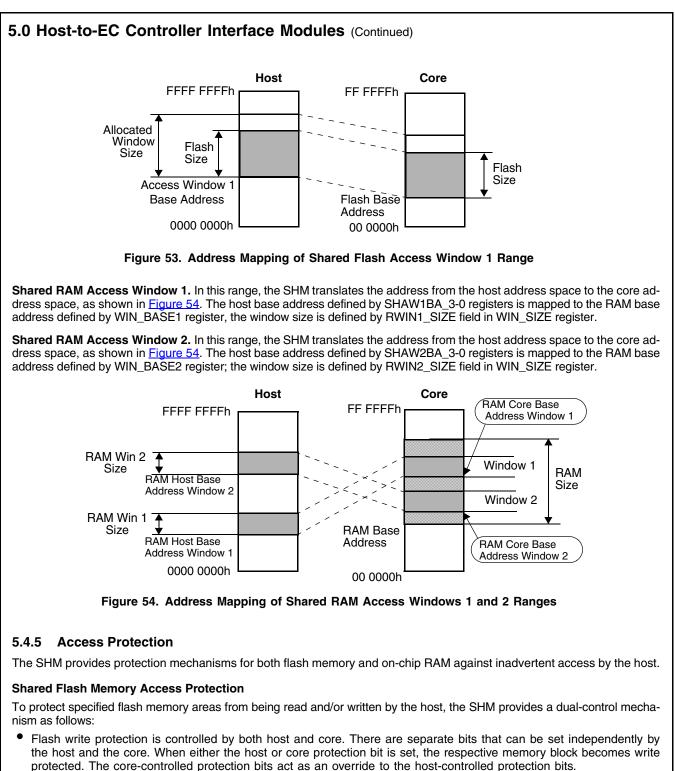

| J. <del>T</del> | 5.4.1  | Overview                                                                                                                       |            |

|                 | 5.4.2  | LPC Bus Transactions                                                                                                           |            |

|                 | 5.4.3  |                                                                                                                                |            |

|                 |        | Address Range Detection and Operation                                                                                          |            |

|                 | 5.4.4  | Host to Core Address Mapping                                                                                                   |            |

|                 | 5.4.5  | Access Protection                                                                                                              |            |

|                 | 5.4.6  | Response to Host Access                                                                                                        |            |

|                 | 5.4.7  | Transaction Types                                                                                                              |            |

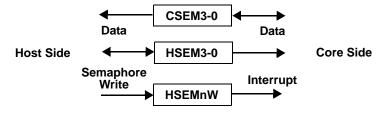

|                 | 5.4.8  | Host-Core Synchronization                                                                                                      | 221        |

|                 |        | Semaphore Interface                                                                                                            |            |

|                 | 5.4.9  | SHM Host Registers                                                                                                             |            |

|                 |        | Shared Memory Host Access Protect 0-3 Register (SMHAP0-3)                                                                      |            |

|                 |        | Shared Access Window 1-2, Semaphore Register (SHAW1-2_SEM)                                                                     |            |

|                 | 5.4.10 | SHM Core Registers                                                                                                             |            |

|                 |        | Shared Memory Core Register Map                                                                                                |            |

|                 |        | Shared Memory Core Status Register (SMC_STS)                                                                                   |            |

|                 |        | Shared Memory Core Control Register (SMC_CTL)                                                                                  |            |

|                 |        | Flash Memory Size Register (FLASH_SIZE)<br>FWH ID on LPC Bus Register (FWH_ID_LPC)                                             |            |

|                 |        | RAM Windows Protection Register (WIN_PROT)                                                                                     |            |

|                 |        | RAM Windows Size Register (WIN_SIZE)                                                                                           |            |

|                 |        | Shared Access Window 1-2, Semaphore Register (SHAW1-2_SEM)                                                                     |            |

|                 |        | RAM Window 1 Base Register (WIN_BASE1)                                                                                         |            |

|                 |        | RAM Window 2 Base Register (WIN_BASE2)                                                                                         |            |

|                 |        | Shared Memory Core Override Read Protect Register 0 (SMCORP0)                                                                  |            |

|                 |        | Shared Memory Core Override Read Protect Register 1 (SMCORP1)                                                                  |            |

|                 |        | Shared Memory Core Override Read Protect Register 2 (SMCORP2)<br>Shared Memory Core Override Read Protect Register 3 (SMCORP3) |            |

|                 |        | Shared Memory Core Override Write Protect Register 0 (SMCONP3)                                                                 |            |

|                 |        | Shared Memory Core Override Write Protect Register 1 (SMCOWP1)                                                                 |            |

|                 |        | Shared Memory Core Override Write Protect Register 2 (SMCOWP2)                                                                 |            |

|                 |        | Shared Memory Core Override Write Protect Register 3 (SMCOWP3)                                                                 |            |

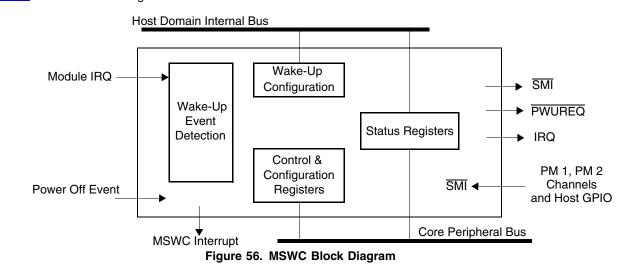

| .5              | MOBILI | E SYSTEM WAKE-UP CONTROL (MSWC)                                                                                                |            |

|                 | 5.5.1  | Features                                                                                                                       |            |

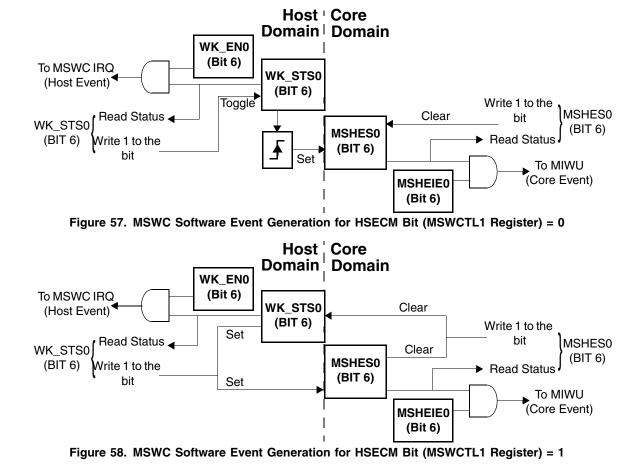

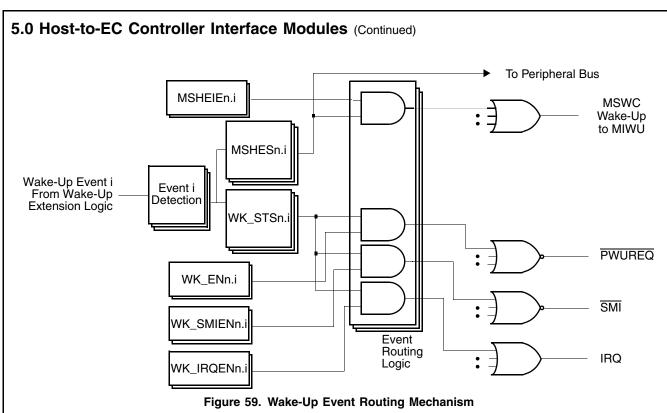

|                 | 5.5.2  | Wake-Up Event Detection and Status Bits                                                                                        |            |

|                 | 5.5.3  | Wake-Up Output Events                                                                                                          |            |

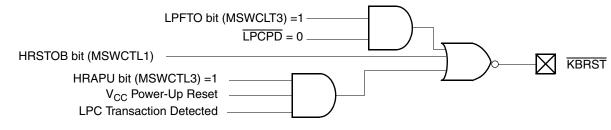

|                 | 5.5.4  | Other MSWC Controlled Elements                                                                                                 |            |

|                 | 5.5.5  | MSWC Host Registers                                                                                                            |            |

|                 |        | Wake-Up Event Status Register 0 (WK_STS0)                                                                                      |            |

|                 |        | Wake-Up Events Enable Register (WK_EN0)                                                                                        |            |

|                 |        |                                                                                                                                |            |

|                 |        | Wake-Up Configuration Register (WK_CFG)                                                                                        |            |

|                 |        |                                                                                                                                | 238<br>238 |

**WPC8763L**

| Tabl | e of C | Content | S (Continued)                                                                                                            |     |

|------|--------|---------|--------------------------------------------------------------------------------------------------------------------------|-----|

|      |        |         | Wake-Up Event Routing to SMI Enable Register 0 (WK_SMIEN0)<br>Wake-Up Event Routing to IRQ Enable Register 0 (WK_IRQEN0) |     |

|      |        | 5.5.6   | MSWC Core Registers                                                                                                      | 241 |

|      |        |         | MSWC Control Status Register 1 (MSWCTL1)                                                                                 | 241 |

|      |        |         | MSWC Control Status Register 2 (MSWCTL2)                                                                                 |     |

|      |        |         | MSWC Control Status Register 3 (MSWCTL3)                                                                                 |     |

|      |        |         | Host Configuration Base Address Low (HCBAL)                                                                              |     |

|      |        |         | Host Configuration Base Address High (HCBAH)<br>MSWC Interrupt Enable Register 2 (MSIEN2)                                |     |

|      |        |         | MSWC Host Event Status Register 0 (MSHES0)                                                                               |     |

|      |        |         | MSWC Host Event Interrupt Enable Register (MSHEIE0)                                                                      |     |

|      |        | 5.5.7   | Usage Hints                                                                                                              | 245 |

| 6.0  | Host   | t Modul | les and Host Interface                                                                                                   |     |

|      | 6.1    | DEVIC   | E ARCHITECTURE AND CONFIGURATION                                                                                         | 246 |

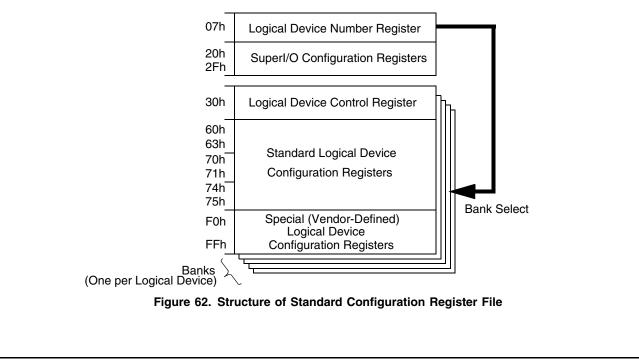

|      | •••    | 6.1.1   | Configuration Structure and Access                                                                                       |     |

|      |        | 6.1.2   | Standard Configuration Registers                                                                                         |     |

|      |        | 6.1.3   | Default Configuration Setup                                                                                              |     |

|      |        | 6.1.4   | Module Control                                                                                                           |     |

|      |        | 6.1.5   | Address Decoding                                                                                                         |     |

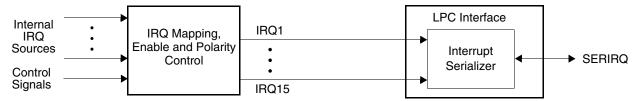

|      |        | 6.1.6   | LPC Interface                                                                                                            |     |

|      |        | 6.1.7   | Interrupt Serializer                                                                                                     |     |

|      |        | 6.1.8   | Protection                                                                                                               |     |

|      |        | 6.1.9   | SuperI/O Configuration Registers                                                                                         |     |

|      |        | 0.1.9   | SuperI/O ID Register (SID)                                                                                               |     |

|      |        |         | SuperI/O Configuration 1 Register (SIOCF1)                                                                               |     |

|      |        |         | SuperI/O Configuration 5 Register (SIOCF5)                                                                               |     |

|      |        |         | SuperI/O Revision ID Register (SRID)                                                                                     |     |

|      |        |         | SuperI/O Configuration D Register (SIOCFD)                                                                               | 256 |

|      |        | 6.1.10  | Mobile System Wake-Up Control (MSWC) Configuration                                                                       | 257 |

|      |        |         | Logical Device 4 (MSWC) Configuration                                                                                    | 257 |

|      |        | 6.1.11  | Keyboard and Mouse Interface (KBC) Configuration                                                                         | 258 |

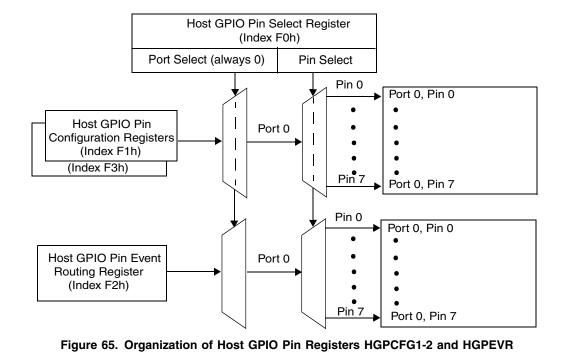

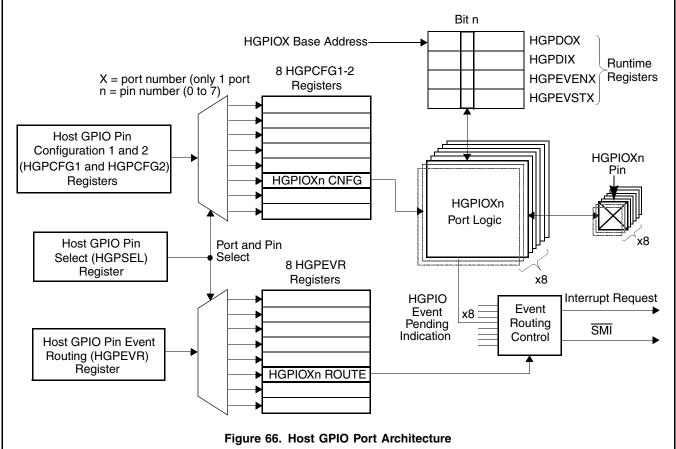

|      |        | 6.1.12  | Host GPIO (HGPIO) Configuration                                                                                          | 259 |

|      |        |         | Host GPIO Pin Select Register (HGPSEL)                                                                                   |     |

|      |        |         | Host GPIO Pin Configuration Register 1 (HGPCFG1)                                                                         |     |

|      |        |         | Host GPIO Event Routing Register (HGPEVR)                                                                                |     |

|      |        | 0 4 4 0 | Host GPIO Pin Configuration Register 2 (HGPCFG2)                                                                         |     |

|      |        | 6.1.13  | Shared Memory (SHM) Configuration                                                                                        |     |

|      |        |         | Shared Memory Configuration Register (SHM_CFG)<br>Shared Access Windows Configuration Register (WIN_CFG)                 |     |

|      |        |         | Shared Windows 1, Base Address 0 Register (SHAW1BA_0)                                                                    |     |

|      |        |         | Shared Window 1, Base Address 1 Register (SHAW1BA_1)                                                                     |     |

|      |        |         | Shared Window 1, Base Address 2 Register (SHAW1BA_2)                                                                     |     |

|      |        |         | Shared Window 1, Base Address 3 Register (SHAW1BA_3)                                                                     |     |

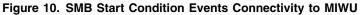

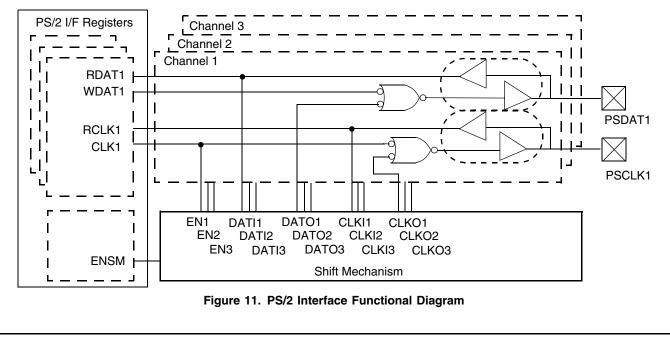

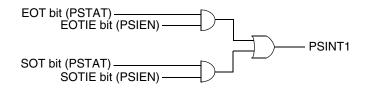

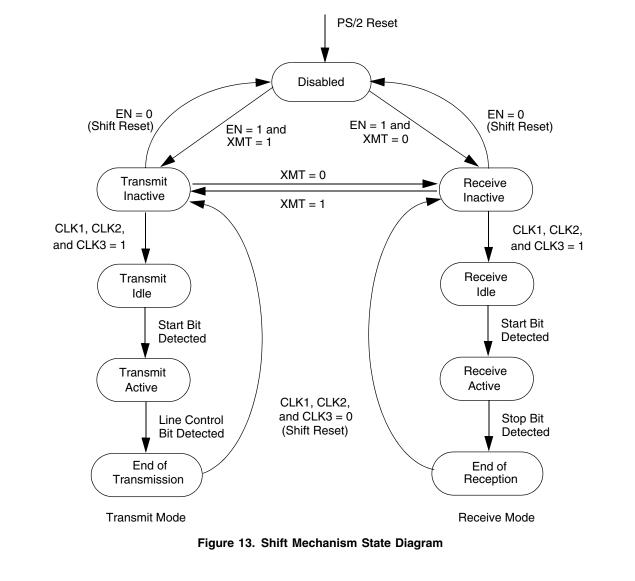

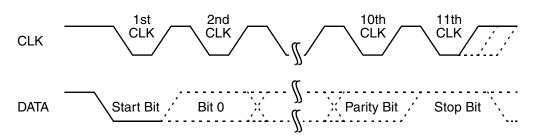

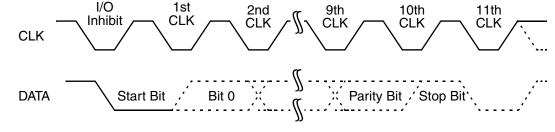

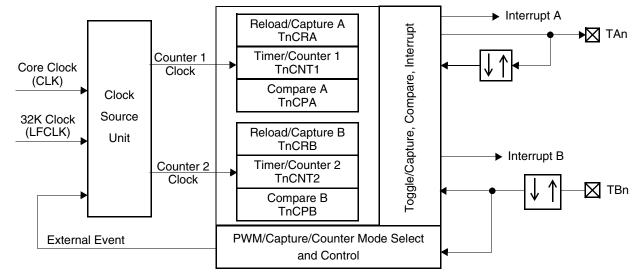

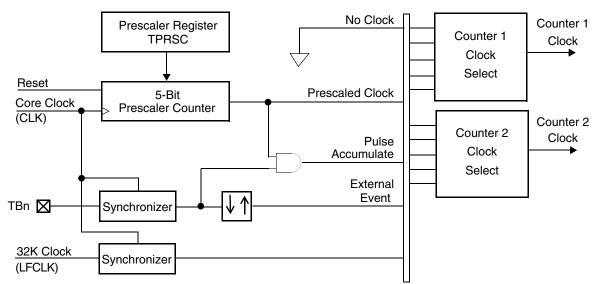

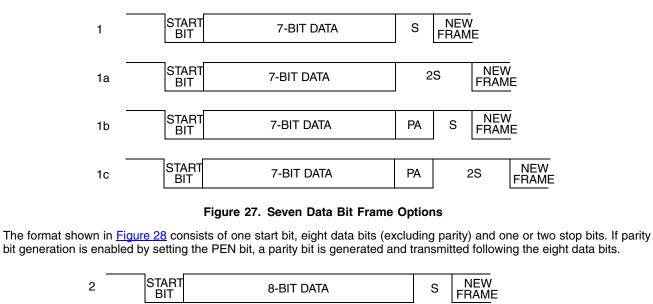

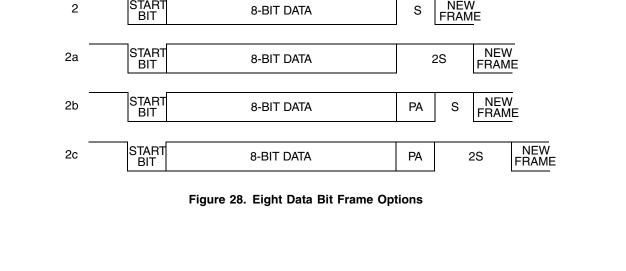

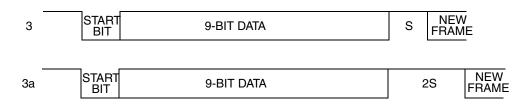

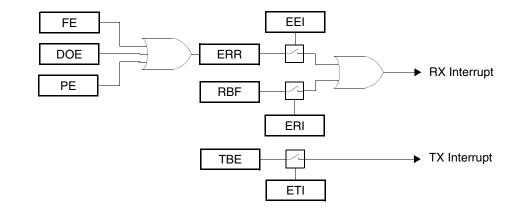

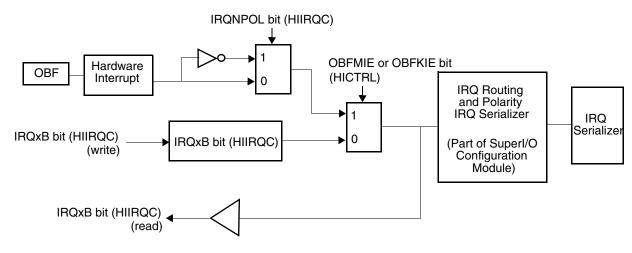

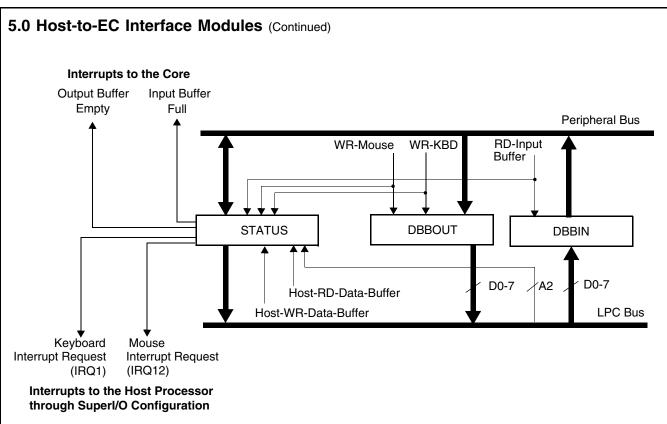

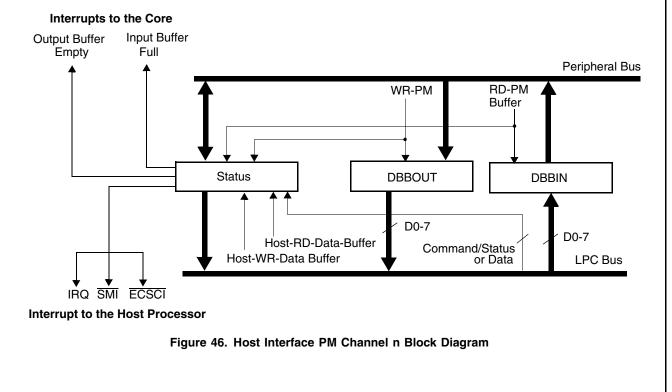

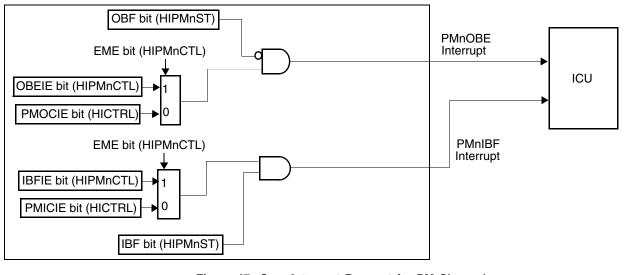

|      |        |         | Shared Window 2, Base Address 0 Register (SHAW2BA_0)                                                                     |     |