# **MPS Confidential - For Compulab Use Only**

# **MP2940A** Digital Multi-phase Controller With PMBus Interface for IMVP8/9

# DESCRIPTION

The MP2940A is a single rail, multi-phase digital VR controller compliant with IMVP8/IMVP9 for Intel microprocessors. It works with MPS's Intelli-Phase products to complete a multi-phase VR solution with minimum external components. It also can be configured to single phase operation.

The MP2940A provides on-chip MTP to store application configurations. Its configurations and fault information are easy to program or monitor through a PMBus interface. The MP2940A can monitor and report output current through Intelli-Phase CS output.

The MP2940A is based on a unique, digital multiphase, non-linear control to provide fast load transient response with minimum output capacitors. With only one power loop control method for both steady state and load transient, the loop compensation parameter is very easy to configure.

# FEATURES

- Configurable Phase Number

- Intel IMVP8 and IMVP9 Compliant

- PVID Interface to Support VccAUX

- PMBus Compliant

- Serial VID Interface for Programming and Monitoring

- Built-In MTP to Store Customer Configuration

- Automatic Loop Compensation

- Auto Phase-Shedding to Improve Overall Efficiency

- Phase-to-Phase Active Current Balancing

- Input/Output Voltage and Power, and Output Current Monitoring

- Regulator Temperature Monitoring

- UVLO/OVP/UVP/OCP/OTP/RVP with Options of No Action, Latch, Retry, or Hiccup

- Digital Programmable Load Line

- RoHS Compliant 4x4 TQFN-28

# APPLICATIONS

- Ultra-Book Core

- High Performance Notebook Core

- Tablet Core

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

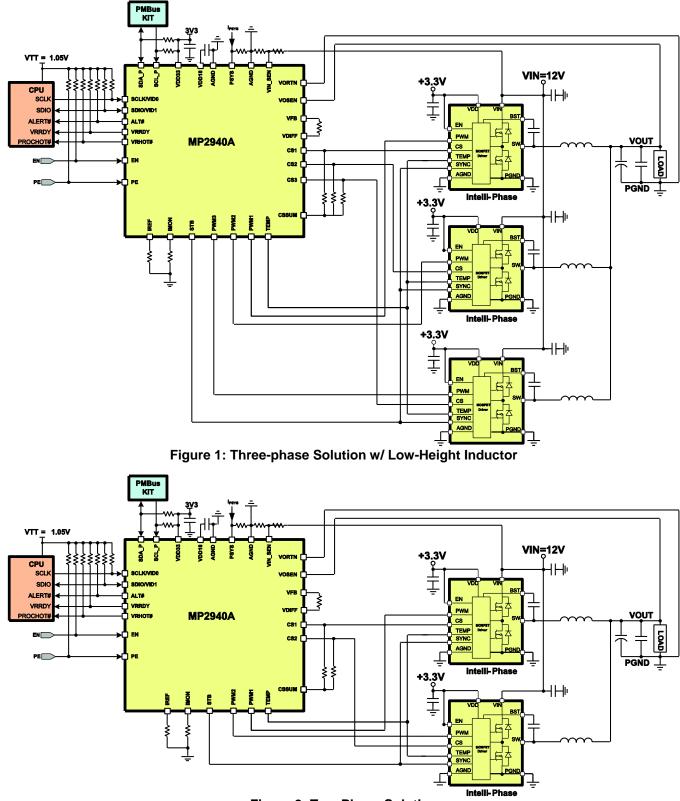

# **TYPICAL APPLICATION**

Figure 2: Two-Phase Solution

# **ORDERING INFORMATION**

|   | Part Number*     | Package           | Top Marking |

|---|------------------|-------------------|-------------|

| Μ | P2940AGRT-xxxx** | TQFN-28 (4mmx4mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP2940AGRT-xxxx–Z);

\*\* "xxxx" is the configuration code identifier for the register settings stored in the internal non-volatile memory (NVM). Each "x" can be a hexadecimal value between 0 and F. Please work with an MPS FAE to create this unique number.

# **TOP MARKING**

# MPSYWW

# M2940A

## LLLLLL

MPS: MPS prefix Y: Year code WW: Week code M2940A: Part number LLLLLL: Lot number

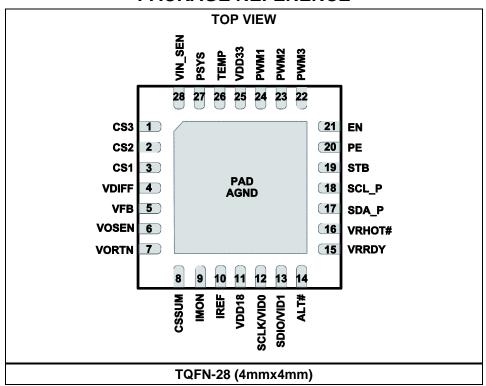

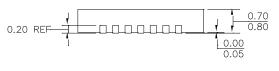

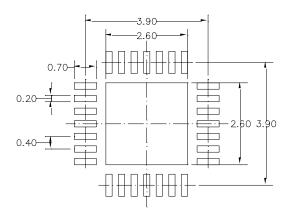

# **PACKAGE REFERENCE**

# **PIN FUNCTIONS OF MP2940A**

| Pin # | Name      | I/O     | Description                                                                                                                                                                                                                                                                                         |  |

|-------|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | CS3       | A [I]   | Phase3 current sense inputs. Float CS of the unused phase.                                                                                                                                                                                                                                          |  |

| 2     | CS2       | A [I]   | Phase2 current sense inputs. Float CS of the unused phase.                                                                                                                                                                                                                                          |  |

| 3     | CS1       | A [I]   | Phase1 current sense inputs. Float CS of the unused phase.                                                                                                                                                                                                                                          |  |

| 4     | VDIFF     | A[O]    | Differential remote sense amplifier output.                                                                                                                                                                                                                                                         |  |

| 5     | VFB       | A [I/O] | <b>Feedback of VR.</b> VFB sources a current proportional to the sensed output current ( $I_{droop}$ ). This current flows through the resistor between VFB and VDIFF to create a voltage drop proportional to the load current. Select a resistor between VDIFF and VFB to set a proper load line. |  |

| 6     | VOSEN     | A[I]    | <b>Positive remote voltage sense input.</b> VOSEN is connected directly to the VR output voltage at the load and should be routed differentially with VORTN.                                                                                                                                        |  |

| 7     | VORTN     | A[I]    | <b>Remote voltage sensing return input of VR.</b> VORTN is connected directly to ground at the load and should be routed differentially with VOSEN.                                                                                                                                                 |  |

| 8     | CSSUM     | A [I]   | <b>Total phase current monitor for VR AVP.</b> Connect the active phase CS signal into CSSUM through current sense resistors.                                                                                                                                                                       |  |

| 9     | IMON      | A [I/O] | <b>Analog total load current signal of VR.</b> IMON sources a current proportional to the sensed total load current from CS_SUM. Connect an external resistor from IMON to AGND to program the gain.                                                                                                |  |

| 10    | IREF      | A [I/O] | Internal bias current set. Connect an $61.9k\Omega$ resistor from IREF to GND.                                                                                                                                                                                                                      |  |

| 11    | VDD18     | A [I/O] | <b>1.8V LDO output for internal digital power supply.</b> Connect a 1µF bypass capacitor to AGND.                                                                                                                                                                                                   |  |

| 12    | SCLK/VID0 | D [I]   | <b>Multi-functional pin.</b> When this pin is selected to support the SVID interface, this in will source a synchronous clock from the CPU. The frequency range is from 0MHz to 26MHz. When this pin is selected to support the PVID for the VccAUX ail, it is VID0.                                |  |

| 13    | SDIO/VID1 | D [I/O] | <b>Aulti-functional pin.</b> When this pin is selected to support the SVID interface, it eceives or drives the Data signal for the SVID bus. When it is selected to support he PVID for the VccAUX rail, it is VID1.                                                                                |  |

| 14    | ALT#      | D [O]   | lert pin. Open drain output. Alert signal from VID controller to CPU.                                                                                                                                                                                                                               |  |

| 15    | VRRDY     | D [O]   | <b>'R ready output of the controller.</b> Open drain output that signals when the utput voltage is outside of the proper operating range. The VCCIO rail is xpected for pull up; however, some systems may pull up to a maximum voltage f 3.3V, with external pull-up resistors.                    |  |

| 16    | VRHOT#    | D [O]   | <b>Voltage regulator thermal throttling logic output.</b> Open drain output. This pin actively pulls low if the monitored temperature exceeds the programmed VRHOT# temperature threshold.                                                                                                          |  |

| 17    | SDA_P     | D [I/O] | Data signal between the PMBus controller and VID controller.                                                                                                                                                                                                                                        |  |

| 18    | SCL_P     | D [I]   | Source synchronous clock from the PMBus Controller.                                                                                                                                                                                                                                                 |  |

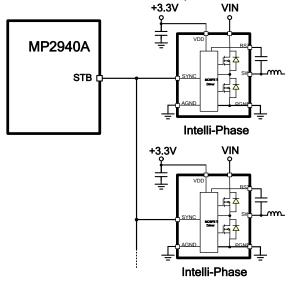

| 19    | STB       | D[O]    | Digital output to indicate Intelli-Phase to enter low power mode.                                                                                                                                                                                                                                   |  |

| 20    | PE        | D[I]    | <b>Program enable.</b> Program the enable input for system configuration through the PMBus when EN is OFF, pull low to AGND with a $0\Omega$ register if not used.                                                                                                                                  |  |

| 21    | EN        | D [I]   | Enable control for the controller.                                                                                                                                                                                                                                                                  |  |

| 22    | PWM3      | D [O]   | Tri-state logic-level PWM outputs. Each output is connected to the input of                                                                                                                                                                                                                         |  |

| 23    | PWM2      | D [O]   | Intelli-Phase's PWM pin.<br>The logic levels are 0V for low logic and 3.3V for high logic.                                                                                                                                                                                                          |  |

| 24    | PWM1      | D [O]   | The output is set to tri-state to shut down both the high-side MOSFET and low-<br>side MOSFET of Intelli-Phase.                                                                                                                                                                                     |  |

# PIN FUNCTIONS OF MP2940A (continued)

| Pin # | Name    | I/O   | Description                                                                                                                                                                                                                        |  |

|-------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 25    | VDD33   | A [I] | <b>3V power supply input.</b> Connect a 4.7µF bypass capacitor to the ground.                                                                                                                                                      |  |

| 26    | TEMP    | A [I] | <b>Analog signal from VR to VID controller.</b> TEMP indicates the power stage temperature. Connect all of Intelli-Phase's VTEMP pins together to produce the maximum junction temperature and then connect to MP2940A's TEMP pin. |  |

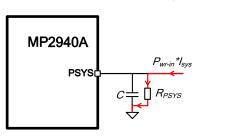

| 27    | PSYS    | A[I]  | <b>Total system input power monitor.</b> A current proportional to the system power flows out from a sensor and goes to ground through an R <sub>PSYS</sub> .                                                                      |  |

| 28    | VIN_SEN | A[I]  | Input voltage sense. Connect VIN_SEN to VIN through a 1/16 divider network.                                                                                                                                                        |  |

| PAD   | AGND    | I/O   | Analog ground.                                                                                                                                                                                                                     |  |

# **ABSOLUTE MAXIMUM RATINGS** <sup>(1)</sup>

| VDD330.3V to +4.0 V                                       |

|-----------------------------------------------------------|

| VDD180.3V to +2.0 V                                       |

| VORTN–0.3V to +0.3 V                                      |

| CS1/2/3, PWM1/2/3, VFB, VDIFF, VOSEN,                     |

| VRRDY, VRHOT#, SCL_P, SDA_P, PE, EN,                      |

| SCLK/VID0, SDIO/VID1, TEMP0.3V to +3.6 V                  |

| All Other Pins–0.3V to +1.8 V                             |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ |

|                                                           |

| Junction Temperature150°C                                 |

| Lead Temperature                                          |

| Storage Temperature –65°C to +150°C                       |

| Recommended Operating Conditions <sup>(3)</sup>           |

| VDD33+3.15V to +3.4V                                      |

Operating Junction Temp. (T<sub>J</sub>). -40°C to +125°C

# Thermal Resistance $^{(4)}$ $\theta_{JA}$ $\theta_{JC}$

TQFN-28(4mmX4mm) ...... 42 ...... 9.... °C/W

Notes:

- 1. Exceeding these ratings may damage the device.

- 2. The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature.

- 3. The device is not guaranteed to function outside of its operating conditions.

- 4. Measured on JESD51-7, 6-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

VDD33 = 3.3V, EN = 1V,  $T_J$  =25°C, unless otherwise noted.

| Parameter                         | Symbol                              | Condition                                                      | Min  | Тур    | Max  | Units |

|-----------------------------------|-------------------------------------|----------------------------------------------------------------|------|--------|------|-------|

| REMOTE SENSE AMPLIFI              | ER                                  | ·                                                              |      | ·      |      | ·     |

| Bandwidth <sup>(5)</sup>          | GBW(RSA)                            |                                                                |      | 20     |      | MHz   |

| VORTN current                     | I <sub>RTN1,2</sub>                 | EN=1V; V <sub>OSEN</sub> =3V; V <sub>ORTN</sub> =0V            |      | -25    | -50  | μA    |

| VOSEN current                     | I <sub>VOSEN1,2</sub>               | EN=1V; V <sub>ORTN</sub> =0V; V <sub>OSEN</sub> =3V            |      | 50     | 100  | μA    |

| OSCILLATOR                        |                                     | · · · · ·                                                      |      |        |      |       |

| Frequency                         | f <sub>osc</sub>                    | I <sub>REF</sub> =1.23V; R <sub>IREF</sub> =61.9kΩ             | 1.5  | 1.5625 |      | MHz   |

| SYSTEM INTERFACE CON              |                                     | JTS                                                            |      |        |      |       |

| EN/PE                             |                                     |                                                                |      | -      |      |       |

| Input low voltage                 | VIL <sub>(EN)</sub>                 |                                                                |      |        | 0.4  | V     |

| Input high voltage                | VIH <sub>(EN)</sub>                 |                                                                | 0.8  |        |      | V     |

| Enable high leakage               | IIH <sub>(EN)</sub>                 | EN=2V                                                          |      |        | 3.6  | μA    |

| Input low voltage                 | VIL <sub>(PE)</sub>                 |                                                                |      |        | 0.8  | V     |

| Input high voltage                | VIH <sub>(PE)</sub>                 |                                                                | 2.4  |        |      | V     |

| PE high leakage                   | IIH <sub>(PE)</sub>                 | PE=3.6V                                                        |      |        | 2.0  | μA    |

| Enable delay                      | TA                                  | EN high to SVID ready                                          |      | 1.5    |      | ms    |

| THERMAL THROTTLING (              | ONTROL                              |                                                                |      |        |      |       |

| VRHOT# low output<br>impedance    |                                     | Ivrhot#=20mA                                                   |      | 8      | 12   | Ω     |

| VRHOT# high leakage current       |                                     | V <sub>RHOT</sub> =1.8V                                        | -3   |        | 3    | μA    |

| IMON OUTPUT                       |                                     |                                                                |      |        |      | 1     |

| Current gain accuracy             | I <sub>MON</sub> /I <sub>CS_S</sub> | Measured from $I_{CS_SUM}$ to $I_{MON}$ , $I_{CS_SUM} = 1.2mA$ |      | 1:32   |      | A/A   |

| Digital lout error                |                                     |                                                                |      | +/-1   |      | %     |

| COMPARATOR                        |                                     |                                                                |      |        |      | •     |

| Propagation delay <sup>(5)</sup>  | t <sub>PD</sub>                     |                                                                |      | 10     |      | ns    |

| Common-mode range <sup>(5)</sup>  |                                     |                                                                | 0    |        | 2.74 | V     |

| <b>COMPARATOR</b> (Protectio      | n)                                  |                                                                |      |        |      |       |

| Under-voltage threshold           | V <sub>DIFF(UV)</sub>               | Relative to reference DAC voltage                              |      | -150   |      | mV    |

| Over-voltage threshold            | V <sub>DIFF(OV2)</sub>              | Relative to reference DAC voltage                              |      | 200    |      | mV    |

|                                   | V <sub>DIFF(OV1)</sub>              | OVP1 DAC voltage                                               |      |        | 2.54 | V     |

| PWM1~3, STB OUTPUTS               |                                     |                                                                |      |        |      | •     |

| Output low voltage                | Vol (PWM)                           | I <sub>PWM(SINK)</sub> = 400 µA                                |      | 10     | 200  | mV    |

| Output high voltage               | Voh (PWM)                           | IPWM(SOURCE) = -400 $\mu$ A                                    | 3.15 |        |      | V     |

| Rise and fall time <sup>(5)</sup> |                                     | C = 10pF                                                       |      | 10     |      | ns    |

MP2940A Rev. 1.0 2/6/2019

# ELECTRICAL CHARACTERISTICS (continued)

VDD33 = 3.3V, EN = 1V,  $T_J$  =25°C, unless otherwise noted.

| Parameter                                    | Symbol                    | Condition                                            | Min  | Тур  | Max  | Units |

|----------------------------------------------|---------------------------|------------------------------------------------------|------|------|------|-------|

| PWM/STB<br>tri-state leakage                 |                           | PWM = 1.5V; EN = 0V                                  | -1   |      | 1    | μA    |

| INTERNAL LDO OUTPUT                          |                           |                                                      |      |      |      |       |

| LDO output voltage                           | VDD18                     | Load = 0mA                                           |      | 1.8  |      | V     |

| LDO regulator load<br>capability             | Ivdd18                    | Voltage drop - 40mV                                  | 30   | 40   |      | mA    |

| VDD33 SUPPLY                                 |                           |                                                      |      |      |      |       |

| Supply voltage range                         | VDD33                     |                                                      | 3.15 | 3.3  | 3.4  | V     |

|                                              |                           | EN=PE=high, VDD33=3.6V                               |      | 7    |      | mA    |

| Supply current                               |                           | EN= PE=low, VDD33=3.6V                               |      | 100  |      | μA    |

|                                              |                           | EN=PE=high, VDD33=3.6V,<br>PS4, T <sub>A</sub> =25°C |      | 140  |      | μA    |

| UVLO threshold voltage                       | VDD33uv<br>LO             | VDD33 is rising                                      |      | 2.88 |      | V     |

| UVLO hysterisis <sup>(5)</sup>               | VDD33 <sub>UV</sub><br>LO | VDD33 is falling                                     |      | 75   |      | mV    |

| SVID Interface <sup>(5)</sup>                |                           |                                                      |      |      |      |       |

| CPU interface voltage                        | VIL                       | Logic low                                            |      |      | 0.45 | V     |

| (SDIO, SCLK)                                 | VIH                       | Logic high                                           | 0.65 |      |      | V     |

| Termination resistance<br>(SDIO, SCLK, ALT#) | R <sub>PU</sub>           |                                                      | 50   | 55   |      | Ω     |

| Leakage current<br>(SDIO, SCLK, ALT#)        | IL                        | 0V to VTT                                            | -10  |      | 10   | μA    |

| Pad capacitance<br>(SDIO, SCLK, ALT#)        | CPAD                      |                                                      |      |      | 4    | pF    |

| Pin capacitance<br>(SDIO, SCLK, ALT#)        | CPIN                      |                                                      |      |      | 5    | pF    |

| Buffer on resistance<br>(SDIO, SCLK, ALT#)   | R <sub>ON</sub>           |                                                      | 4    |      | 13   | Ω     |

| Maximum voltage<br>(SDIO, SCLK, ALT#)        | V <sub>MAX</sub>          | Transient voltage including ringing                  | -0.3 |      | 2.1  | V     |

| Slew rate<br>(SDIO, SCLK, ALT#)              |                           | 2nH, 4pF load                                        | 0.5  |      | 2    | V/ns  |

| ADC                                          |                           |                                                      |      |      |      |       |

| Voltage range                                |                           |                                                      | 0    |      | 1.6  | V     |

| ADC resolution <sup>(5)</sup>                |                           |                                                      |      | 10   |      | Bits  |

| DNL <sup>(5)</sup>                           |                           |                                                      |      | 1    |      | LSB   |

| Sample rate <sup>(5)</sup>                   |                           |                                                      |      | 780  |      | kHz   |

# ELECTRICAL CHARACTERISTICS (continued)

VDD33 = 3.3V, EN = 1V, T<sub>J</sub> = $25^{\circ}$ C, unless otherwise noted.

| Parameter                           | Symbol    | Condition                           | Min  | Тур | Max  | Units |

|-------------------------------------|-----------|-------------------------------------|------|-----|------|-------|

| DAC (Reference Voltage for          | or Vout)  | · · ·                               |      | •   |      | •     |

| Range                               |           |                                     |      | 1.6 |      | V     |

| Resolution/LSB <sup>(5)</sup>       |           |                                     |      | 5   |      | mV    |

| DAC (Vout Calibration)              |           | · · · · · ·                         |      |     |      |       |

| Range                               |           |                                     |      | 320 |      | mV    |

| Resolution <sup>(5)</sup>           |           |                                     |      | 8   |      | bit   |

| DAC (Protection for Per Pl          | nase OCP  | )                                   |      | •   | •    | •     |

| Range                               |           | Adjustable via PMBus                | 1.28 |     | 2.54 | V     |

| Resolution/LSB                      |           |                                     |      | 10  |      | mV    |

| DAC (Protection for OVP1)           | )         |                                     |      |     |      |       |

| Range                               |           | Adjustable via PMBus                | 0    |     | 2.54 | V     |

| Resolution/LSB                      |           |                                     |      | 20  |      | mV    |

| PMBus DC Characteristics            | S (SDA_P, | SCL_P)                              |      | 1   | 1    | 1     |

| Input high voltage                  | VIH       | SCL_P, SDA_P                        | 2.3  |     |      | V     |

| Input low voltage                   | VIL       | SCL_P, SDA_P                        |      |     | 0.8  | V     |

| Input leakage current               |           | SCL_P, SDA_P, ALT_P                 | -10  |     | 10   | μA    |

| Output low voltage                  | Vol       | ALT_P sinks 2mA                     |      |     | 400  | mV    |

| Maximum voltage <sup>(5)</sup>      | Vmax      | Transient voltage including ringing | -0.3 | 3.3 | 3.6  | V     |

| Pin Capacitance <sup>(5)</sup>      | CPIN      |                                     |      |     | 10   | pF    |

| PMBus Timing Characteris            | stics (5) |                                     |      |     |      | -     |

| Operating frequency range           |           |                                     | 10   |     | 2000 | kHz   |

| Bus free time                       |           | Between stop and start condition    | 0.5  |     |      | μs    |

| Holding time                        |           |                                     | 0.26 |     |      | μs    |

| Repeated start condition setup time |           |                                     | 0.26 |     |      | μs    |

| Stop condition setup time           |           |                                     | 0.26 |     |      | μs    |

| Data hold time                      |           |                                     | 0    |     |      | ns    |

| Data setup time                     |           |                                     | 50   |     |      | ns    |

| Clock low time out                  |           |                                     | 25   |     | 35   | ms    |

| Clock low period                    |           |                                     | 0.5  |     |      | μs    |

| Clock high period                   |           |                                     | 0.26 |     | 50   | μs    |

| Clock/data fall time                |           |                                     |      |     | 120  | ns    |

| Clock/data rise time                |           |                                     |      |     | 120  | ns    |

Notes:

5. Guaranteed by design or characterization data, not tested in production.

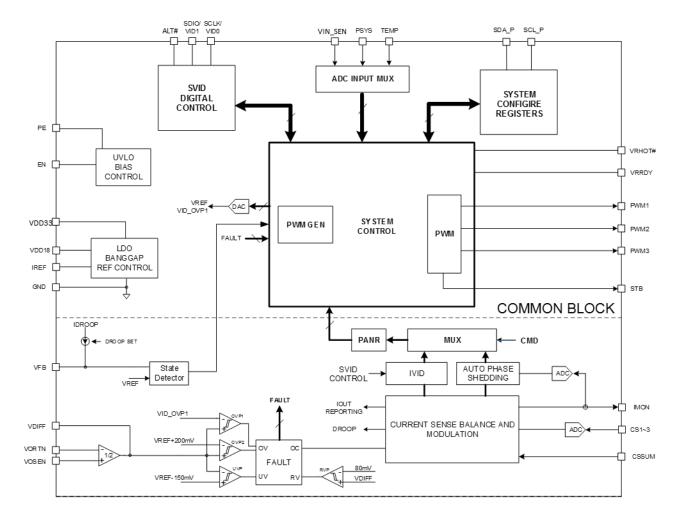

# **BLOCK DIAGRAM**

Figure 3: System Functional Block

# **OPERATION**

The MP2940A is a single rail, multi-phase digital VR controller compliant with IMVP8/IMVP9 for Intel microprocessors. It can adaptively shed phases and add phases according to the load current to improve VR efficiency. It contains blocks of precision DAC and ADC, a differential remote voltage sense amplifier, a current sense amplifier. internal loop compensation, VR\_READY monitoring, temperature monitoring, and a PMBus/SVID interface. MTP for custom configuration fault protection features include: Vin under-voltage lockout (UVLO), over-current protection (OCP), over-voltage protection (OVP), under-voltage protection (UVP), overtemperature protection (OTP), and reverse voltage protection (RVP).

## Phase Configuration

MP2940A supports multiple The phases depending on different applications/platforms; it can be configured up to 3 phases via the PMBus register MFR\_PHASE\_CFG (CAh[2:0]) See Table 1.

#### Table 1: Phase Configuration and Active PWM Pins

| MFR_PHASE_<br>CFG [2:0] | Active PWM Pins |

|-------------------------|-----------------|

| 011                     | 1,2,3           |

| 010                     | 1,2             |

| 001                     | 1               |

| others                  | Not supported   |

## **PMBus Address**

To support multiple VR devices used with the same PMBus interface, there is a PMBus address for every device. The PMBus address is a 7 bit code, which is setup by the register. The register SHUTLEVEL\_ADDRPMBUS (E1h[6:0]) can be used to program the PMBus address.

## **Power On Sequence**

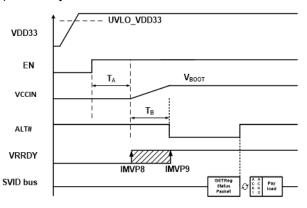

The MP2940A is supplied by a +3.3V voltage for an analog circuit. The system will be reset by the internal power-on reset signal (POR). After the system comes out of POR, the data in MTP will be loaded to the registers to configure VR operation. The initialization process will take about 0.5ms + delay time Marked at T<sub>A</sub> (see Figure 4), and then execute the soft-start process to charge the output capacitor with the SetVID Slow slew rate until the reference reaches the target boot voltage. T<sub>B</sub> (see Figure 4) is set by VBOOT/Slow.

Figure 4: Start-Up Sequence

The MP2940A supports both IMVP8 and IMVP9 with different VRRDY assert time settings; the VRRDY signal will assert either when the SVID interface is ready to receive CPU commands (IMVP8), or when the VR reaches the boot voltage level (IMVP9).

MP2940A The also provides additional programmable EN delay by setting registers MFR EN DLY and MFR EN FILT TIME. The T<sub>A</sub> time can be set longer than the 0.5ms, TA=0.5ms+MFR EN DLY+MFR EN FILT TIM E. See the register map for how to program the delay time.

When the boot voltage is set to 0, the PWM remains in tri-state until a valid SVID voltage is received. The controller then ramps the voltage to the target value and asserts ALERT#.

# Steady State and Switching Frequency

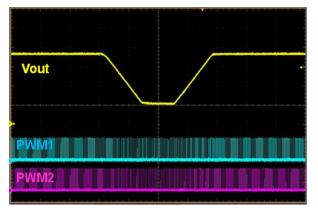

The MP2940A applies a digital non-linear control to provide a fast transient response and easy loop compensation. The duty cycle of each active phase's PWM updates in real-time according to the input voltage and reference voltage under the set switching frequency. The active phases will be automatically interleaved during the steady state. At the steady state, the switching frequency is set at MFR\_FS\_VBOOT (E5h[14:8]).

The MP2940A adaptively changes the switching frequency of an individual phase during load transient to achieve super fast transient performance with minimum BOM cost.

## **Power State Change**

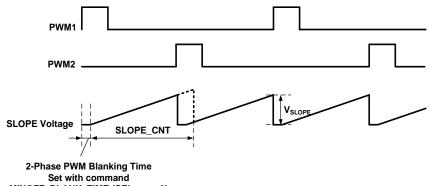

The SVID bus can change the VR into different power states (PS0, PS1, PS2, PS3, and PS4) to achieve optimized efficiency on various load conditions. These states are entered by programming the power state register using SVID's SetPS command. The VR optimizes its power loss to flatten the efficiency curve over the operating current range, with the Power State commands issued by the processor. In PS0 mode, all phases run in CCM. In PS1 mode, only one phase runs in CCM; other phases are in tristate. In PS2 mode, only one phase is running in the diode emulation mode, and the switching frequency falls down automatically to save the power loss at light load. See Table 2 for details on how the phases act at different power states.

During the dynamic VID transition issued by SVID commands like SetVID\_Fast or SetVID\_Slow, the power state will be changed to PS0 by default and runs in full-phase PWM mode. After the output is well regulated to the new target voltage, the power state will stay in PS0 mode until the processor sends a new command to change the power state.

| PS State | Active Phase  | CCM/DCM |

|----------|---------------|---------|

| PS0      | All Phase PWM | ССМ     |

| PS1      | One Phase PWM | ССМ     |

| PS2      | One Phase PWM | DCM     |

| PS3      | One Phase PWM | DCM     |

| PS4      | All OFF       |         |

Table 2: Power State and Phase Activities

## Reference

The MP2940A supports both 5mV VID step and 10mV VID step for IMVP8 and IMVP9 with only one DAC to generate REF. There is a control bit (MFR\_STEP\_SEL) in the E4h register that chooses the VID step. If this control bit is set to 1, then the output (VREF) of the DAC is shown as equation (1). Equation (2) shows how to get VREF when the control bit is written to 0.

$$VREF = (VID + 49)/2*5mV$$

(1)

$$VREF = (VID + 19)/2 * 10mV$$

(2)

# **Output Voltage Sense**

The output voltages are remotely sensed with  $\frac{1}{2}$  gain differential amplifiers. The sensed output

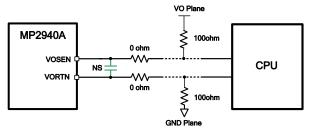

voltages are used for close loop compensation, OV/UV protection, and PMBus monitoring. A proper "package sense" (see Figure 5) is recommended to enclose the board parasitics within the feedback loop of the VR to achieve noise rejection and performance optimization. Two  $0\Omega$  resistors are placed close to the MP2940A.

Figure 5: Output Remote Sense

To avoid errant operation or board damage when the CPU is absent, two  $100\Omega$  catch-up resistors are placed with connection to the Vo and PGND plane to get the output feedback even if the CPU is absent.

## Input Voltage Sense

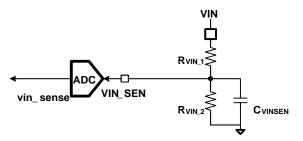

The input power supply voltage is sampled at the VIN\_SEN pin and used for the output voltage regulation as the feed-forward control, Vin\_UVLO, Vin\_OVP fault protection, and monitoring via PMBus. Use two resistors connected to the input voltage and a 10nF bypass capacitor to get a 1/16 divider for VIN\_SEN (see Figure 6). The default value is  $R_{VIN_1}=2M\Omega$  and  $R_{VIN_2}=133K\Omega$ .

Figure 6: VIN Sense Network

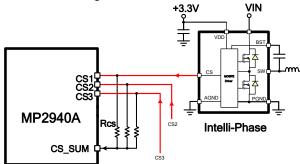

## **Current Sense**

The MP2940A works with the MPS Intelli-Phase to sense per phase inductor current and the total current (see Figure 7). The cycle-by-cycle current information is used for phase current balancing, over-current protection, and load line setting. The current sense gain is Kcs for Intelli-Phase products. The resistor  $R_{CS}$  is connected from CS to CS\_SUM. CS\_SUM is a 1.23V constant voltage, which is capable of sinking small currents to provide voltage shifts that meet the operating voltage range of CS.

Different Intelli-Phase products have different operating voltage ranges for CS:  $V_{CS\_MIN}$  and  $V_{CS\_MAX}$ . Refer to each Intelli-Phase's datasheet to determine the minimum and maximum operating voltage range. Use equation (3) to determine a proper  $R_{CS}$  value:

$$V_{cs_{MIN}} < I_{cs}R_{cs} + 1.23V < V_{cs_{MAX}}$$

(3)

$I_{cs} = IL \times Kcs$

By pairing with Intelli-Phase, the MP2940A doesn't need temperature compensation and impendence matching to achieve accurate current sensing.

Figure 7: Phase Current Sense with 3-phase Configuration

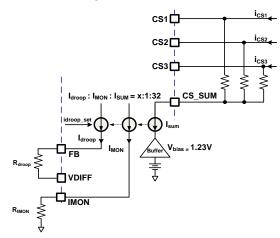

## **IMON and IDROOP**

The current flowing out from IMON is 1/32 of the filtered CS\_SUM; it is named ISUM. Place a resistor from IMON to ground to generate a voltage proportional to the output current. The IMON voltage is sampled and converted by ADC and then stored in the lout register, which is scaled to ICCMAX = ADC full range (FFh). The IMON voltage will get to its max data,  $V_{IMON_Max}$ , when the output current reaches ICCMAX.

The IMON voltage can be calculated with equation (4)

$$V_{\rm IMON} = \frac{I_{\rm OUT} \times K_{\rm CS} \times R_{\rm IMON}}{32}$$

(4)

Where:

Kcs is the current sense gain of Intelli-phase.

$I_{OUT}$  is the output current.

R<sub>IMON</sub> is the IMON resistor.

V<sub>IMON\_Max</sub>=1.6\*8/11 V.

The  $R_{\text{IMON}}$  can be set with lout=ICCMAX, and VIMON=V\_{\text{IMON}\\_\text{MAX}}

$$R_{IMON} = \frac{32 \times V_{IMON\_Max}}{I_{CCMAX} \times K_{CS}} \quad (5)$$

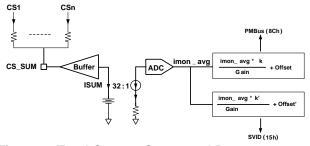

Figure 8 shows the MP2940A IMON sense, and Idroop block diagram.

## Figure 8: Current Sense Imon/ Idroop

## Static Load Line Setting

The MP2940A uses a resistor between VFB and VDIFF to set the static load line. The droop current (default 1/8 of ISUM) flowing through the droop resistor from VFB to VDIFF generates the droop voltage. Given the application requirements for  $R_{LL}$  load line regulation,  $R_{droop}$  can be calculated according to equation (6) considering the 1/2 gain on the output remote sense.

$$R_{DROOP} = \frac{R_{LL}}{2 \times K_{CS} \times K_{Droop}}$$

(6)

Where  $K_{CS}$  is the current sense gain of the Intelli-Phase mentioned above. For the MP86901x series, the  $K_{CS}$  default value is 10µA/A.  $K_{Droop}$  is the gain of the droop current mirror, the default is 8/8\*1/8.

## Digital Programmable Load Line

## Table 3: Digital Load Line Trim

| IDROOP_SET [3:0] | Idroop Gain                  |

|------------------|------------------------------|

| 0000 b           | 0                            |

| 0001 b           | 4/8 * 1/8* Isuм              |

| 0010 b           | 5/8 * 1/8* Isuм              |

| 0011 b           | 6/8 * 1/8* І <sub>Ѕ∪М</sub>  |

| 0100 b           | 7/8 * 1/8* I <sub>SUM</sub>  |

| 0101 b (Default) | 8/8 * 1/8* Isuм              |

| 0110 b           | 9/8 * 1/8* Isuм              |

| 0111 b           | 10/8 * 1/8* I <sub>SUM</sub> |

| 1000 b           | 11/8 * 1/8* I <sub>SUM</sub> |

| 1001 b           | 12/8 * 1/8* І <sub>SUM</sub> |

| 1010 b           | 13/8 * 1/8* І <sub>Ѕ∪М</sub> |

| 1011b            | 14/8 * 1/8* I <sub>SUM</sub> |

| 1100 b           | 15/8 * 1/8* І <sub>Ѕ∪М</sub> |

| 1101 b           | 16/8 * 1/8* І <sub>Ѕ∪М</sub> |

| 1110 b           | 17/8 * 1/8* I <sub>SUM</sub> |

| 1111 b           | 18/8 * 1/8* І <sub>ЅUM</sub> |

In addition to the load line setting from the external droop resistor, the MP2940A provides a digital programmable load line trim by register-idroop\_set(1Bh[3:0]). The droop current mirror gain of the MP2940A is shown in Table 3. The load line can be changed through the PMBus and stored in MTP. With digital load line, users can change the droop without replacing the external droop resistor. The default value of idroop\_set is 0001b, which presents a 1/8 gain to  $I_{SUM}$ .

# **IOUT Report**

The lout register 15h in the SVID register reports to the processor to avoid exceeding the thermal design point and maximum current capability of the system. The MP2940A applies a userprogrammable register which contains the gain, MFR\_IMON\_SVID\_GAIN (FCh[7:0]) and a signed current offset MFR\_IMON\_SVID\_OFFSET (**FCh[14:8]**) on the SVID lout reporting. The two programmable parameters allow users to match the IMON scaling to the design's Voltage Regulator Tolerance Band (VRTOB) calculation. This provides the most accurate current reporting across the entire load range and maximizes the performance of Intel turbo. Customers can reduce gain or offset to under report the total current to the CPU for better performance. Refer to the register map for details on how to configure the register **FCh**.

The PMBus lout register 8Ch is also used for total current protection. If the auto-phase shedding function is enabled via the PMBus, the total current report also will be used to determine whether to enter or exit the phase shedding mode to flatten the overall efficiency over the operating current range. Register IOUT\_CAL\_GAIN(38h[10:0]) and IOUT\_CAL\_OFFSET(39h[5:0]) are used to program the PMBus lout report gain and offset to ensure the MP2940A tracks the load current efficiently (see Figure 9).

Figure 9: Total Current Sense and Report

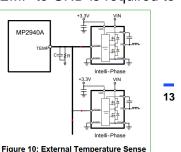

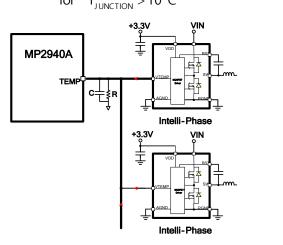

# **Temperature Sense**

MP2940A The measures the external temperature by connecting all the Intelli-Phase VTEMP pins (see Figure 10). The voltage of the MP2940A TEMP pin is the highest voltage among the Intelli-Phase, which indicates the highest temperature of the VR power system. The sensed temperature is used for an overtemperature fault protection, or asserting the SVID thermal alert or VRHOT# signal for the processor. A 49.9KQ resistor in parallel with a 1µF capacitor from TEMP to GND is required to discharge TEMP.

VTEMP of Intelli-Phase is a voltage output proportional to the junction temperature. The junction temperature can be calculated using equation (7).

$$T_{JUNCTION} = \frac{V_{TEMP} + 100 \text{mV}}{10 \text{mV} / ^{\circ} \text{C}}$$

(7)

for T\_\_\_\_\_\_> 10°C

Figure 10: External Temperature Sense

For example, if the VTEMP voltage is 700mV, the junction temperature of that Intelli-Phase is 80°C. VTEMP cannot go below 0V, so it will read 0V for a junction temperature lower than 10°C.

# **Dynamic VID (DVID)**

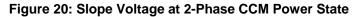

The MP2940A supports a Dynamic VID change when it receives SetVID (fast/slow/decay) commands.

The VID slew rate of SetVID Fast is set by register VID STEP NUM (FAh[7:6]), which is equal to the VID increase or decrease per step. VID\_SR\_CNT(FAh[5:0]) defines the duration of time for the VID change one time. The fast slew rate can be calculated from the equation (8).

$$SlewRate = \frac{(VID_STEP_NUM+1) \times VID_STEP}{VID_SR_CNT \times 100ns}$$

(8)

Where VID\_STEP\_NUM is programmable from 0~3, VID STEP is programmable to either 5mV or 10mV, according to the requirement of the CPU, and VID SR CNT is programmable in the range of 1 to 63. If VID\_STEP\_NUM is 1, VID STEP is 5mV and VID SR CNT is 3, so the slew rate is 33.3mV/µs.

The SetVID\_Slow slew rate is decided by register F9h[3:0], which can be programmed to 1/2, 1/4, 1/8 or 1/16 of the SetVID Fast. The

slew rate for SetVID Decay is determined by the load current and output capacitor bank.

FDh sets the Alert# assert time for DVID, a delay time can be added, which helps the MP2940A meet the Intel spec. Refer to the register map for details on how to configure the register FDh.

When DVID rises, the inductor current will rise to charge the output capacitors. This current will introduce a big positive droop voltage due to the load line, resulting in an output voltage lower than the target voltage, which may cause the output voltage to exceed the minimum regulation tolerance budget 1µs after Alert# asserts. The MP2940A can be programmed to ramp up more VID steps by register (FAh[10:8]). After VID ramps to the target voltage, it will keep this VID voltage for the time set bv MFR\_PLATFORM\_TIME (F1h[11:6]). VID will fall back to the target VID voltage to cause the output voltage to rise into the regulation tolerance budget (TOB) as required by the Intel spec. Please refer to register map for the configuration.

When the output voltage is ramping down, the inductor current will become smaller to discharge the output capacitors, which will continue to discharge the output capacitors when the ramping ends. This may lead to output undershoot because of the droop voltage increase. It needs a duration of time for the inductance current to balance the load current. resulting in output voltage undershoot.

Figure 11. DVID Rise and Fall

The MP2940A applies a low-pass filter for the VID-DAC to smooth the reference voltage when the output voltage is ramping down.

Figure 11 shows the output voltage when SetVID\_Fast rises after the previous SetVID\_Fast fall is finished.

# Programmable Audible Noise Reduction (PANR)

VR audible noise has been an issue for more than a decade. This issue is mainly caused by the capacitor flex with the voltage fluctuation at a certain frequency within the audible range. The MP2940A provides a control algorithm (PANR) to mitigate the voltage fluctuation within the range of audible frequency. This function can be activated by an enable bit. Two registers are available to program this function. If a SetVID down step is larger than a certain amplitude defined by register X, this command will be delayed for a certain time defined by register Y.

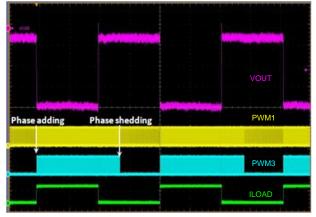

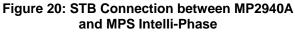

#### Auto-Phase Shedding (APS)

The MP2940A provides the auto-phase shedding function to improve the efficiency at PS0 state, according to the comparison between the total current report and the programmable threshold.

There are 3 types of registers to configure the auto-phase shedding function:

- MFR\_1PHL (**BBh[8:4]**) sets the phase shedding level. It is 1 phase at the CCM level. 2~3 phase CCM's level is MFR\_1PHL \* phase num. 1 phase DCM's level is fixed to 5A.

- 2. MFR\_PHASE\_HYS (**BBh[3:0]**) sets the hysteresis current value when phase adding.

- 3. phs\_drop\_dly (**30h[8:6]**) sets the delay time for the phase shedding action after the system's total current detected is smaller than the phase shedding threshold. Once the total current is higher than the phase adding

threshold, idle phases will be added immediately. Please refer to the register map for the auto-phase shedding and adding configurations.

Table 4 and Table 5 list the phase shedding/adding entry conditions based on the current report.

In addition to the basic requirements listed in Table 4 and 5, the instructions below should be followed to improve the transient condition:

- 1. When the configured full phase number is smaller than the phase adding number, the system will run in full phase.

- The DVID process will run in full phase if the VR receives the SetVID\_Fast orSetVID\_Slow command from the processor, regardless if the auto-phase shedding function is enabled or disabled. The phase shedding process starts after the VR is settled.

- A load step up that causes VFB to fall below REFF – 15mV will trigger VR running in full phase to avoid the output voltage undershoot.

Figure 12: Phase Shedding and Adding Process

#### Table 4: Phase Number when Phase Adding Based on the Current Report (lout)

| Condition                                                        | Phase Number                      |

|------------------------------------------------------------------|-----------------------------------|

| 2*MFR_1PHL + MFR_PHASE_HYS ≤ lout                                | 3 phase CCM or full(<3) phase CCM |

| 1*MFR_1PHL + MFR_PHASE_HYS ≤ lout<br>< 2*MFR_1PHL+ MFR_PHASE_HYS | 2 phase CCM or full(<2) phase CCM |

| 5A + MFR_PHASE_HYS ≤ lout<br>< 1*MFR_1PHL+ MFR_PHASE_HYS         | 1 phase CCM                       |

| lout < 5A + MFR_PHASE_HYS                                        | 1 phase DCM                       |

#### Table 5: Phase Number when Phase Shedding Based on the Current Report (lout)

| Condition                     | Phase Number                      |

|-------------------------------|-----------------------------------|

| 2*MFR_1PHL < lout             | 3 phase CCM or full(<3) phase CCM |

| 1*MFR_1PHL < lout≤ 2*MFR_1PHL | 2 phase CCM or full(<2) phase CCM |

| 5A < lout≤ 1*MFR_1PHL         | 1 phase CCM                       |

| lout ≤ 5A                     | 1 phase DCM                       |

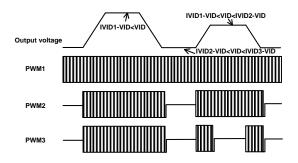

#### IVID

The MP2940A supports an IVID function (defined in the IMVP8 spec) for automatic phase shedding and optimization, regardless if the PS state is required.

There are 2 types of registers for the IVID function:

- 1. IVIDx-VID: Only updated with the processor, which guarantees the current values are written in the IVIDx-I register.

- 2. IVIDx-I: Default setup by the VR vendor and can be rewritten by the processor. The registers reflect the maximum instantaneous current for the phase number being defined.

The IVID registers need to work with MFR 1PHL and MFR PHASE HYS registers to determine the active phase number. Table 6 lists the operation condition and the phase number.

In addition to the basic rules listed in Table 6, the VR also needs to follow the rules listed in the auto-phase shedding function section to improve the transient condition.

Figure 13 shows the IVID process. It uses the time set by register MFR IVID VALID\_WAITTIME (F9h[15:8]) to start reducing the phase number after VR is

settled, and phase adding immediately after receiving the SetVID command.

Figure 13: IVID Process when DVID

When the auto-phase shedding and IVID function are both enabled, the IVID function determines the phase number first, according to Table 6 based on the VID, then VR starts phase shedding according to Table 6 based on the current report.

To set up the auto-phase shedding and IVID functions, follow the steps below:

- the 1. Set MFR 1PHL up and MFR PHASE HYS according to the best efficiency performance of the Intelli-phase

- 2. Set up the IVID1-I, IVID2-I and IVID3-I according to the load application.

| Condi                                                                        | Condition                                    |                                                         |  |

|------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|--|

| VID> IVID1-VID                                                               |                                              | Full phase CCM                                          |  |

| IVIDx-VID≥ VID> IVID(x+1)-<br>VID(x=1,2) or IVID3-VID≥ VID                   | (n-1)*MFR_1PHL< IVIDx-I ≤<br>n*MFR_1PHL(n>1) | n phase CCMor<br>Full( <n) ccm<="" phase="" td=""></n)> |  |

| $VIDx-VID \ge VID > IVID(x+1)-VID$<br>(x=1,2) or $VID3-VID \ge VID$          | 5A< IVIDx-I ≤ 1*MFR_1PHL                     | 1 phase CCM                                             |  |

| $\frac{ V Dx-V D  V D   V D(x+1)-V D }{(x=1,2) \text{ or }  V D3-V D  V D }$ | IVIDx-I ≤ 5A                                 | 1 phase DCM                                             |  |

#### Table 6: Phase Shedding and Adding Based on the VID

## PMBus and SVID Communication

The MP2940A supports real time monitoring for the VR operation parameters and status monitoring with the PMBus and SVID interface. Table 7 lists the monitored parameters.

Table 7: PMBus and SVID Monitored Parameters

| Parameter      | PMBus | SVID |

|----------------|-------|------|

| Output Voltage | ×     | ×    |

| Output Current | ×     | ×    |

| Temperature    | ×     | ×    |

| Input Voltage  | ×     | ×    |

| Input Power    | ×     | ×    |

| Phase current  | ×     |      |

| OV             | ×     |      |

| OC             | ×     | ×    |

| UV             | ×     |      |

| OT             | ×     | ×    |

| CML            | ×     |      |

## Vin Protection:

The MP2940A adopts programmable Vin protection with the following protection thresholds programmed into the related PMBus registers.

The VR will tri-state shut off immediately if the sensed input voltage is below VIN\_OFF (**36h[7:0]**. It restarts when the sensed input voltage is above VIN\_ON (**35h[7:0]**) with Vin UVLO non-latch mode.

The VR will latch if the sensed input voltage is above VIN\_OV\_FAULT\_LIMIT (**55h[7:0]**) when the Vin OVP is set to latch mode.

The VR is warned if the input voltage is below VIN\_UV\_WARNING\_LIMIT (**58h[7:0]**).

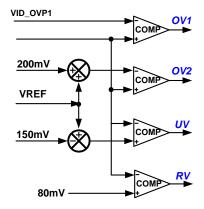

## **Over-Voltage Protection (OVP)**

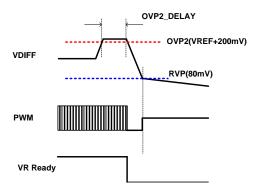

The OVP circuit monitors the output voltage for an over-voltage condition. The over-voltage signals generation is shown in Figure 14.

There are two levels of over-voltage protection.

OVP2 is the first level of over-voltage protection. When the detected output voltage is 400mV higher than the reference voltage, the controller triggers OV protection after a certain delay time; the OVP2 action will latch PWM low on to discharge the output until the output drops below 160mV (RVP triggered). OVP2 is defined as REF+200mV for the 1/2 gain of the output voltage to VDIFF. Figure 15 shows the VR behavior when OVP2 is triggered.

#### Figure 14: OVP and RVP Trigger Threshold

To avoid a false trigger, the OVP2 is blanked during soft start and shutdown, and the VID transition period (including SetVID Fast/Slow/ Decay). It sets PS4 as well.

The OVP2 default is latch off in normal IMVP8/9 applications. Additional modes like retry and hiccup mode are available to be set by register MFR\_OVP2\_SET\_MODE (F1h[5:4]). The OVP delay time is set by register OVP2 DELAYTIME (F7h[11:6]).

OVP1 is the second level of over-protection protection. It is set by OVP\_DA\_LIMIT(**F6h[7:0]**). This is an absolute OV threshold, which is active whenever the controller is enabled, regardless of operation/fault conditions. In the event of an OVP1 condition, the PWMs are latched low to turn off the high-side MOSFETs and turn on the low-side MOSFETs to discharge the output voltage. The OVP1 latch can only be reset by EN or toggling VCC.

Figure 15: OVP and RVP Fault Protection

## **Reverse Voltage Protection (RVP)**

During an OVP period, the LS will remain on to make the inductor current go negative. A large reverse inductor current may cause negative output voltages that harm the processor and other output components. In addition to OV protection, the MP2940A implements a reverse voltage protection (RVP) to avoid the negative voltage ringing after the OV logic is triggered. Once the VDIFF voltage drops below 80mV, the MP2940A will trigger the RVP by latching all PWM outputs to tri-state. The reverse inductor current can quickly reset to 0A by dissipating the energy in the inductor to the input DC voltage source through a forward-biased body diode of the high-side MOSFETs (see Figure 15).

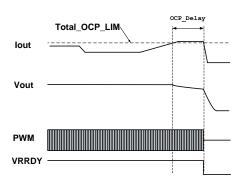

## **Over-Current Protection (OCP)**

The MP2940A provides a programmable total current protection to stop the VR from operating at an extremely heavy load; it will be triggered if the sensed average total output current is higher OC triaaer than the level MFR OCP SET LEVEL (EEH[6:0]). Once the sensed lout is over the set OCP level, with a set MFR OCP SET DELAY TIME delav time (EEH[13:8]), the part will turn off both the HS and LS FETs by setting the PWM to tri-state. Figure 16 shows the diagram of the OCP process for total current protection.

Figure 16: OC Protection for Total Current

The total OCP limit and delay time is set at register EEh. The OCP set point is recommended to be set around 130% of Iccmax. The OCP delay is recommended around 500µs.

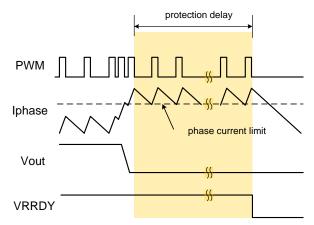

## Phase Current Limit Protection

In addition to the total over-current limit based on the sensed lout, the MP2940A also utilizes a cycle-by-cycle valley point over-current limit method to limit each phase current. If the present phase current is higher than the setting valley point and remains for 80ns, this phase will not turn on, and the next phase will turn on when its own PWM is on, in order to regulate the output voltage at the set point. The phase current limit itself will not trigger latch off, latch off is triggered when the phase current limit is triggered by either the OCP or UVP.

The valley point over-current level can be programmed via the PMBus to limit the per phase current in register OCP DA LIMIT (F6h[15:8]).

Figure 17 shows the process when the output is shorted to ground. During this process, the per phase OCP will limit the phase current immediately and after a certain time the VR will shut down.

#### Figure 17: Phase Current Limit Protection when **Output Dead Short**

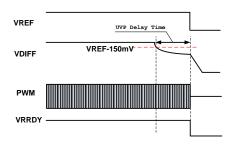

# **Under-Voltage Protection (UVP)**

If the sensed output voltage (VDIFF) is low (below VREF-150mV) for a certain amount of time, the system will trigger UVP and immediately shut down and turn off all phases set by the PWM into tri-state (see Figure 18). Normally, UVP is triggered when OCP is reached. The UVP protection model (Default Latch) can be set through reaister MFR\_UVP\_SET\_MODE (F1h[7:6]). The UVP delay time is set by register

UVP DELAYTIME (F7h[5:0]). Refer to the register list for more details.

Figure 18: Under-Voltage Protection

# VR\_HOT#

The VR HOT# fault is asserted when the sensed external temperature exceeds the temp max threshold. This is used for fault reporting only and it cannot shut down the system. VR HOT# also has a fixed 3°C hysteresis when VR HOT# asserts if the sensed temperature exceeds the temp max. The VR\_HOT# pin will also assert when PSYS exceeds the critical value. VR HOT# is initialized in tri-state when the device powers up.

## Phase Current Balancing/Thermal Balancing

The phase current to the MP2940A is sensed and calculated with the current reference in the slow current PI loop. Each phase's PWM on time is adjusted individually to balance the currents by applying  $\Sigma$ - $\Delta$  modulation and delay line loop technology in the current balance modulation, so the current is balanced and the jitter is greatly reduced.

Each current balance loop can also include the programmable phase current offset to achieve the thermal balance among the phases. The phase that has the worst cooling capability can be set to take less phase current by adding an offset on the CS sample value. This keeps the phase thermals more balanced. Please refer to the register map for the phase current offset configuration.

# **SVID** Interface

To support multiple VR devices used on the same SVID bus, the SVID address can be programmed independently through the register MFR ADDR SVID (E6h[11:0]). The SVID address is a 4 bit code. There are 14 addresses for up to 14 voltage regulator controllers. The final addresses 0Eh and 0Fh are "All Call"

addresses, and all the VR controllers respond to those addresses.

The All Call address will only be used with SetVID or SetPS commands. It cannot be used with GET or SetRegADR and SetRegDAT commands. The VR will NAK those commands with an All Call address. The VR acknowledges an All Call address in the same manner as a single address.

## **Input Power Sense**

The SVID address 0Dh domain is defined to report the system input power. When the voltage of PSYS reaches 0.8V, it means the platform input power has reached Pwr\_in\_Max and the report value for the CPU is FFh in the 1Bh SVID register.

The input power sensing device sends a current signal to the MP2940A, which is proportional to the input power. A resistor from PSYS to GND will convert the current into voltage. A bypass capacitor is required. Figure 19 shows the PSYS connection. The PSYS resistor value is calculated with Equation (9):

$$\mathsf{R}_{\mathsf{PSYS}} = \frac{0.8}{\mathsf{P}_{\mathsf{wr} \ \mathsf{in} \ \mathsf{max}} \times \mathsf{I}_{\mathsf{sys}}} \tag{9}$$

Figure 19: PSYS Connection

Where I<sub>sys</sub> is the current gain of the input power sensor, with the unit of µA/W.

Pwr in Max is the maximum input power, with the unit of W.

The averaging interval of the input power sense is 1ms, and the register update interval is 500 µs.

## **PS4 Enter/Exit Mechanism**

The VR will enter PS4 mode after receiving a SETPS4 command, and VR changes the VID of the VR to 00h and

stops the PWM(s) of the VR immediately. ALERT# remains de-asserted in PS4, the chip turns off PLL and disables as many analog circuits as possible to save power (except the SVID interface).

The SetVID or SetPS0/1/2/3 commands are used to wake the VR from PS4 mode. When VR receives a SetVID or SetPS0/1/2/3 command, it enables the internal PLL and analog circuits. PS4 exit latency is less than 90µs, counted from ACK of the PS4 exit command to where VID is ready to ramp (SETPS) or (SETVID) starts ramping.

#### **STB Function**

STB is used to set MPS Intelli-Phase into standby mode by connecting STB to SYNC of the MPS Intelli-Phase. In PS4 mode, STB will go into tri-state, so Intelli-Phase will enter low power mode to save power. In normal operation mode, STB is logic high. Figure 20 shows the connection between the MP2940A STB pin and the MPS Intelli-Phase SYNC pin.

#### **PVID Function for VccAUX**

The MP2940A supports both a SVID interface, and a PVID interface. Pin 12 (SCLK/VID0) and pin 13 (SDIO/VID1) are multi-function pins and can be configured by the PMBUS register setting. When the MP2940A is configured to support the Intel CPU, pins 12 and 13 are selected as SCLK/SDIO to be the SVID interface. When the MP2940A is configured to support the VccAUX rail, pins 12 and 13 are selected as the PVID VID0 and VID1 input. When the PVID interface is selected, there are a total of 4 VID1/0 combinations to indicate 4 different output voltage levels. VID1/0=00 always means the output is 0V. For the other 3 combinations of VID1/0 (01, 10, 11), there are 3 corresponding PMBUS registers to set the output voltage level. By utilizing the MP2940A programmable function, the MP2940A is capable of supporting any combination of the target voltage level (see Table 8).

In PVID mode, Alert# (pin 14) is high and VRhot# (pin 16) is low.

| VID1/VID0 | Output Voltage                         |

|-----------|----------------------------------------|

| 00        | 0V                                     |

| 01        | Register Programmable<br>Default 1.1V  |

| 10        | Register Programmable<br>Default 1.65V |

| 11        | Register Programmable<br>Default 1.8V  |

# **SVID REGISTERS**

Table 9 shows the data and configuration registers for the SVID protocol.

| Table 9: SVID Data and Configuration Registers |                       |                                        |         |                                                       |  |  |  |  |

|------------------------------------------------|-----------------------|----------------------------------------|---------|-------------------------------------------------------|--|--|--|--|

| Index                                          | Register Name         | Access                                 | Default | Note                                                  |  |  |  |  |

| 00h                                            | Vendor ID             |                                        | 25h     | Programmable through PMBus                            |  |  |  |  |

| 01h                                            | Product ID            |                                        | 0Bh     | Programmable through PMBus                            |  |  |  |  |

| 02h                                            | Product Revision      | Read Only by Master<br>Write by Vendor | 00h     | Programmable through PMBus                            |  |  |  |  |

| 05h                                            | Protocol ID           |                                        | 05h     | Programmable through PMBus                            |  |  |  |  |

| 06h                                            | Capability            |                                        | 81h     | Programmable through PMBus                            |  |  |  |  |

| 10h                                            | Status_1              |                                        | 00h     |                                                       |  |  |  |  |

| 11h                                            | Status_2              |                                        | 00h     |                                                       |  |  |  |  |

| 12h                                            | Temperature zone      |                                        | 00h     | These registers are operation                         |  |  |  |  |

| 15h                                            | Output Current (lout) | Read by Master<br>Write by PWM         | 00h     | condition dependent.<br>The register values vary with |  |  |  |  |

| 17h                                            | VR Temperature        | White by F Will                        | 00h     | operating conditions.                                 |  |  |  |  |

| 1Bh                                            | Input Power           |                                        | 00h     |                                                       |  |  |  |  |

| 1Ch                                            | Status2_last read     |                                        | 00h     |                                                       |  |  |  |  |

| 21h                                            | ICC_MAX               | Read Only                              | 00h     | Programmable through PMBus                            |  |  |  |  |

| 24h                                            | SR-fast               | Configured by the                      | 30mV/us | Programmable through PMBus                            |  |  |  |  |

| 25h                                            | SR-slow               | Platform                               | 15mV/us | Programmable through PMBus                            |  |  |  |  |

| 30h                                            | Vout max              |                                        | FFH     | Can only be programmed by CPU                         |  |  |  |  |

| 31h                                            | VID setting           | Read & Write by<br>Master              | 00H     | Can only be programmed by CPU                         |  |  |  |  |

| 32h                                            | Pwr State             |                                        | 00H     | Can only be programmed by CPU                         |  |  |  |  |

| 34h                                            | Multi VR configure    | Read by Master<br>Write by PWM         | 01H     | Programmable through PMBus                            |  |  |  |  |

| 42h                                            | IVID1-VID             |                                        | 00h     | Programmable through PMBus                            |  |  |  |  |

| 44h                                            | IVID2-VID             |                                        | 00h     | Programmable through PMBus                            |  |  |  |  |

| 46h                                            | IVID3-VID             | Read & Write by                        | 00h     | Programmable through PMBus                            |  |  |  |  |

| 43h                                            | IVID1-I               | Master                                 | 0Fh     |                                                       |  |  |  |  |

| 45h                                            | IVID2-I               |                                        | 0Fh     | CPU may program these registers during system boot.   |  |  |  |  |

| 47h                                            | IVID3-I               |                                        | 05h     |                                                       |  |  |  |  |

# VID RANGE

The MP2940A covers the full IMVP8/IMVP9 VID range. The IMVP8 VID is 0V, 0.25V~1.52V. Between 0.25V~1.52V, the voltage step is 5mV/step. The IMVP9 VID step is 5mV and 10mV; the voltage of the 5mV VID step matches the IMVP8. The 10mV/step of the IMVP9 VID is 0V, 0.2V~2.74V. Between 0.2V~2.74V, the voltage step is 10mV/step. See Table 10 and Table 11.

| VID(HEX) | VOUT(V) | VID(HEX) | VOUT(V) | VID(HEX) | VOUT(V) | VID(HEX) | VOUT(V) |

|----------|---------|----------|---------|----------|---------|----------|---------|

| 00       | 0       | 40       | 0.565   | 80       | 0.885   | C0       | 1.205   |

| 01       | 0.25    | 41       | 0.57    | 81       | 0.89    | C1       | 1.21    |

| 02       | 0.255   | 42       | 0.575   | 82       | 0.895   | C2       | 1.215   |

| 03       | 0.26    | 43       | 0.58    | 83       | 0.9     | C3       | 1.22    |

| 04       | 0.265   | 44       | 0.585   | 84       | 0.905   | C4       | 1.225   |

| 05       | 0.27    | 45       | 0.59    | 85       | 0.91    | C5       | 1.23    |

| 06       | 0.275   | 46       | 0.595   | 86       | 0.915   | C6       | 1.235   |

| 07       | 0.28    | 47       | 0.6     | 87       | 0.92    | C7       | 1.24    |

| 08       | 0.285   | 48       | 0.605   | 88       | 0.925   | C8       | 1.245   |

| 09       | 0.29    | 49       | 0.61    | 89       | 0.93    | C9       | 1.25    |

| 0A       | 0.295   | 4A       | 0.615   | 8A       | 0.935   | CA       | 1.255   |

| 0B       | 0.3     | 4B       | 0.62    | 8B       | 0.94    | СВ       | 1.26    |

| 0C       | 0.305   | 4C       | 0.625   | 8C       | 0.945   | CC       | 1.265   |

| 0D       | 0.31    | 4D       | 0.63    | 8D       | 0.95    | CD       | 1.27    |

| 0E       | 0.315   | 4E       | 0.635   | 8E       | 0.955   | CE       | 1.275   |

| 0F       | 0.32    | 4F       | 0.64    | 8F       | 0.96    | CF       | 1.28    |

| 10       | 0.325   | 50       | 0.645   | 90       | 0.965   | D0       | 1.285   |

| 11       | 0.33    | 51       | 0.65    | 91       | 0.97    | D1       | 1.29    |

| 12       | 0.335   | 52       | 0.655   | 92       | 0.975   | D2       | 1.295   |

| 13       | 0.34    | 53       | 0.66    | 93       | 0.98    | D3       | 1.3     |

| 14       | 0.345   | 54       | 0.665   | 94       | 0.985   | D4       | 1.305   |

| 15       | 0.35    | 55       | 0.67    | 95       | 0.99    | D5       | 1.31    |

| 16       | 0.355   | 56       | 0.675   | 96       | 0.995   | D6       | 1.315   |

| 17       | 0.36    | 57       | 0.68    | 97       | 1       | D7       | 1.32    |

| 18       | 0.365   | 58       | 0.685   | 98       | 1.005   | D8       | 1.325   |

| 19       | 0.37    | 59       | 0.69    | 99       | 1.01    | D9       | 1.33    |

| 1A       | 0.375   | 5A       | 0.695   | 9A       | 1.015   | DA       | 1.335   |

| 1B       | 0.38    | 5B       | 0.7     | 9B       | 1.02    | DB       | 1.34    |

| 1C       | 0.385   | 5C       | 0.705   | 9C       | 1.025   | DC       | 1.345   |

| 1D       | 0.39    | 5D       | 0.71    | 9D       | 1.03    | DD       | 1.35    |

| 1E       | 0.395   | 5E       | 0.715   | 9E       | 1.035   | DE       | 1.355   |

| 1F       | 0.4     | 5F       | 0.72    | 9F       | 1.04    | DF       | 1.36    |

| 20       | 0.405   | 60       | 0.725   | A0       | 1.045   | E0       | 1.365   |

| 21       | 0.41    | 61       | 0.73    | A1       | 1.05    | E1       | 1.37    |

| 22       | 0.415   | 62       | 0.735   | A2       | 1.055   | E2       | 1.375   |

| 23       | 0.42    | 63       | 0.74    | A3       | 1.06    | E3       | 1.38    |

| 24       | 0.425   | 64       | 0.745   | A4       | 1.065   | E4       | 1.385   |

| 25       | 0.43    | 65       | 0.75    | A5       | 1.07    | E5       | 1.39    |

| 26       | 0.435   | 66       | 0.755   | A6       | 1.075   | E6       | 1.395   |

| 27       | 0.44    | 67       | 0.76    | A7       | 1.08    | E7       | 1.4     |

| 28       | 0.445   | 68       | 0.765   | A8       | 1.085   | E8       | 1.405   |

| 29       | 0.45    | 69       | 0.77    | A9       | 1.09    | E9       | 1.41    |

| 2A       | 0.455   | 6A       | 0.775   | AA       | 1.095   | EA       | 1.415   |

| 2B       | 0.46    | 6B       | 0.78    | AB       | 1.1     | EB       | 1.42    |

| 2C       | 0.465   | 6C       | 0.785   | AC       | 1.105   | EC       | 1.425   |

#### Table 10: IMVP8 5mVVID Step VID Table

# **MPS Confidential - For Compulab Use Only**

# MP2940A- SINGLE LOOP DIGITAL MULTI-PHASE VR CONTROLLER

| 2D | 0.47  | 6D | 0.79  | AD | 1.11  | ED | 1.43  |

|----|-------|----|-------|----|-------|----|-------|

| 2E | 0.475 | 6E | 0.795 | AE | 1.115 | EE | 1.435 |

| 2F | 0.48  | 6F | 0.8   | AF | 1.12  | EF | 1.44  |

| 30 | 0.485 | 70 | 0.805 | B0 | 1.125 | F0 | 1.445 |

| 31 | 0.49  | 71 | 0.81  | B1 | 1.13  | F1 | 1.45  |

| 32 | 0.495 | 72 | 0.815 | B2 | 1.135 | F2 | 1.455 |

| 33 | 0.5   | 73 | 0.82  | B3 | 1.14  | F3 | 1.46  |

| 34 | 0.505 | 74 | 0.825 | B4 | 1.145 | F4 | 1.465 |

| 35 | 0.51  | 75 | 0.83  | B5 | 1.15  | F5 | 1.47  |

| 36 | 0.515 | 76 | 0.835 | B6 | 1.155 | F6 | 1.475 |

| 37 | 0.52  | 77 | 0.84  | B7 | 1.16  | F7 | 1.48  |

| 38 | 0.525 | 78 | 0.845 | B8 | 1.165 | F8 | 1.485 |

| 39 | 0.53  | 79 | 0.85  | B9 | 1.17  | F9 | 1.49  |

| 3A | 0.535 | 7A | 0.855 | BA | 1.175 | FA | 1.495 |

| 3B | 0.54  | 7B | 0.86  | BB | 1.18  | FB | 1.5   |

| 3C | 0.545 | 7C | 0.865 | BC | 1.185 | FC | 1.505 |

| 3D | 0.55  | 7D | 0.87  | BD | 1.19  | FD | 1.51  |

| 3E | 0.555 | 7E | 0.875 | BE | 1.195 | FE | 1.515 |

| 3F | 0.56  | 7F | 0.88  | BF | 1.2   | FF | 1.52  |

|                  | Table 11: IMVP9 10mV VID Step VID Table |          |         |          |              |          |         |  |

|------------------|-----------------------------------------|----------|---------|----------|--------------|----------|---------|--|

| VID(HEX)         | VOUT(V)                                 | VID(HEX) | VOUT(V) | VID(HEX) | VOUT(V)      | VID(HEX) | VOUT(V) |  |

| 00               | 0                                       | 40       | 0.83    | 80       | 1.47         | Ċ0       | 2.11    |  |

| 01               | 0.2                                     | 41       | 0.84    | 81       | 1.48         | C1       | 2.12    |  |

| 02               | 0.21                                    | 42       | 0.85    | 82       | 1.49         | C2       | 2.13    |  |

| 03               | 0.22                                    | 43       | 0.86    | 83       | 1.5          | C3       | 2.14    |  |

| 04               | 0.23                                    | 44       | 0.87    | 84       | 1.51         | C4       | 2.15    |  |

| 05               | 0.24                                    | 45       | 0.88    | 85       | 1.52         | C5       | 2.16    |  |

| 06               | 0.25                                    | 46       | 0.89    | 86       | 1.53         | C6       | 2.17    |  |

| 07               | 0.26                                    | 47       | 0.9     | 87       | 1.54         | C7       | 2.18    |  |

| 08               | 0.27                                    | 48       | 0.91    | 88       | 1.55         | C8       | 2.19    |  |

| 09               | 0.28                                    | 49       | 0.92    | 89       | 1.56         | C9       | 2.2     |  |

| 0A               | 0.29                                    | 4A       | 0.93    | 8A       | 1.57         | CA       | 2.21    |  |

| 0B               | 0.3                                     | 4B       | 0.94    | 8B       | 1.58         | CB       | 2.22    |  |

| 0C               | 0.31                                    | 4C       | 0.95    | 8C       | 1.59         | CC       | 2.23    |  |

| 0D               | 0.32                                    | 4D       | 0.96    | 8D       | 1.6          | CD       | 2.24    |  |

| 0E               | 0.33                                    | 4E       | 0.97    | 8E       | 1.61         | CE       | 2.25    |  |

| 0E<br>0F         | 0.34                                    | 4F       | 0.98    | 8F       | 1.62         | CF       | 2.26    |  |