# High Performance, Single-Synchronous Step-Down Controller with Differential Voltage Feedback

#### **FEATURES**

- · Differential Voltage Feedback

- · DC Compensation for Accurate Regulation

- · Wide Input Voltage Range: 3 V to 28 V

- Output Voltage Range: 0.5 V to 2.0 V with Fixed Options of 1.05 V and 1.00 V

- · Wide Output Load Range: 0 A to 20 A+

- Adaptive On-Time Modulation with Selectable Control Architecture and Frequency

- D-CAP™ Mode at 300 kHz/400 kHz for Fast Transient Response

- D-CAP2<sup>™</sup> Mode at 500 kHz/670 kHz for Ceramic Output Capacitor

- 4700 ppm/°C, Low-Side R<sub>DS(on)</sub> Current Sensing

- R<sub>SENSE</sub> Accurate Current Sense Option

- · Internal, 1-ms Voltage Servo Softstart

- Built-In Output Discharge

- Power Good Output

- Integrated Boost Switch

- Built-In OVP/UVP/OCP

- Thermal Shutdown (Non-latched)

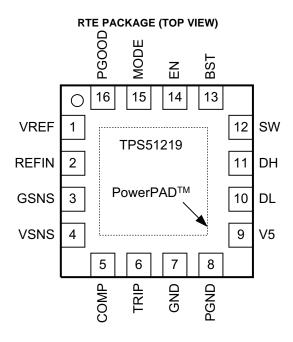

- 3 mm × 3 mm, 16-Pin, QFN (RTE) Package

#### **APPLICATIONS**

- Notebook Computers

- I/O Supplies

## **DESCRIPTION**

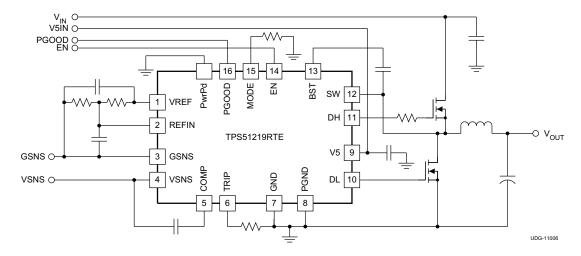

The TPS51219 is a small-sized single buck controller with adaptive on-time control. It provides a choice of control modes (D-CAP™ or D-CAP2™) to meet a wide range of system requirements. It is designed for tight DC regulation requirements such as the VCCIO application for Intel<sup>®</sup> notebooks. The performance and flexibility of the TPS51219 makes it suitable for low output voltage, high current, PC system power rails and similar point-of-load (POL) power supplies. Differential voltage feedback and the voltage compensation function combine to provide high precision power to load devices.

A small package, fixed voltage options and minimal external component count saves cost and space, while a dedicated EN pin and pre-set frequency selections minimize design effort. The skip-mode at light load condition, strong gate drivers, and low-side FET R<sub>DS(on)</sub> current sensing provides high efficiency operation over a broad load range. The external resistor current sense option enables accurate current sensing. The conversion input voltage (the high-side FET drain voltage) ranges from 3 V to 28 V and output voltage ranges from 0.5 V to 2.0 V. The device requires an external 5-V supply.

The TPS51219 is available in a 16-pin, QFN package and is specified for ambient temperature from -40°C to 85°C.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

D-CAP, D-CAP2 are trademarks of Texas Instruments. Intel is a registered trademark of Intel.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE                      | ORDERABLE DEVICE<br>NUMBER | PINS | OUTPUT<br>SUPPLY | MINIMUM<br>QUANTITY |

|----------------|------------------------------|----------------------------|------|------------------|---------------------|

| 40°C to 95°C   | Digatic Oyed Flat Book (OFN) | TPS51219RTER               | 16   | Tape and reel    | 3000                |

| –40°C to 85°C  | Plastic Quad Flat Pack (QFN) | TPS51219RTET               | 16   | Mini-reel        | 250                 |

<sup>(1)</sup> For the most current package and ordering information see the *Package Option Addendum* at the end of this document, or see the TI web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                           |                     | VALUE      | UNIT  |

|---------------------------|---------------------|------------|-------|

|                           |                     | MIN M      | AX    |

|                           | BST                 | -0.3       | 36    |

|                           | BST <sup>(3)</sup>  | -0.3       | 6     |

|                           | SW                  | <b>-</b> 5 | 30    |

| Input voltage range (2)   | EN, MODE, TRIP, V5  | -0.3       | 6.0 V |

|                           | COMP, REFIN, VSNS   | -0.3       | 3.6   |

|                           | GSNS                | -0.35 0.   | 35    |

|                           | PGND                | -0.3       | 0.3   |

|                           | DH                  | -5         | 36    |

|                           | DH <sup>(3)</sup>   | -0.3       | 6     |

| Output voltage range (2)  | DL                  | -0.3       | 6 V   |

|                           | PGOOD               | -0.3       | 6     |

|                           | VREF                | -0.3       | 3.6   |

| Junction temperature rang | e, T <sub>J</sub>   | 1          | 25 °C |

| Storage temperature rang  | e, T <sub>STG</sub> | -55 1      | 50 °C |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted.

<sup>(3)</sup> Voltage values are with respect to the SW terminal.

#### RECOMMENDED OPERATING CONDITIONS

|                           |                                | MIN  | TYP MAX | UNIT  |  |

|---------------------------|--------------------------------|------|---------|-------|--|

| Supply voltage            | V5                             | 4.5  | 5.5     | V     |  |

|                           | BST                            | -0.1 | 33.5    |       |  |

|                           | BST <sup>(1)</sup>             | -0.1 | 5.5     |       |  |

|                           | SW                             | -3   | 28      |       |  |

| Lancet coefficient and an | SW <sup>(2)</sup>              | -4.5 | 28      | .,    |  |

| Input voltage range       | EN, TRIP, MODE                 | -0.1 | 5.5     | V     |  |

|                           | REFIN, VSNS, COMP              | -0.1 | 3.5     |       |  |

|                           | GSNS                           | -0.3 | 0.3     |       |  |

|                           | PGND                           | -0.1 | 0.1     |       |  |

|                           | DH                             | -3   | 33.5    |       |  |

|                           | DH <sup>(1)</sup>              | -0.1 | 5.5     |       |  |

| 0                         | DH <sup>(2)</sup>              | -4.5 | 33.5    | .,    |  |

| Output voltage range      | DL                             | -0.1 | 5.5     | 5.5 V |  |

|                           | PGOOD                          | -0.1 | 5.5     |       |  |

|                           | VREF                           | -0.1 | 3.5     |       |  |

| T <sub>A</sub>            | Operating free-air temperature | -40  | 85      | °C    |  |

- (1) Voltage values are with respect to the SW terminal.

- (2) This voltage should be applied for less than 30% of the repetitive period.

#### THERMAL INFORMATION

|                         |                                                             | TPS51219 |          |

|-------------------------|-------------------------------------------------------------|----------|----------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | RTE      | UNITS    |

|                         |                                                             | 16 PINS  |          |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 48.5     |          |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance (3)               | 49.5     |          |

| $\theta_{JB}$           | Junction-to-board thermal resistance (4)                    | 22.1     | °C // // |

| Ψлт                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.7      | °C/W     |

| ΨЈВ                     | Junction-to-board characterization parameter (6)            | 22.1     |          |

| $\theta_{JCbot}$        | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 7.1      |          |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

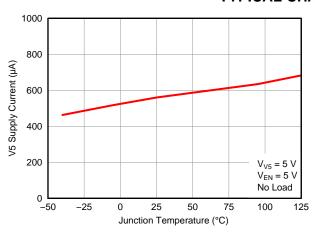

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $V_{V5} = 5 \text{ V}$ ,  $V_{MODE} = 0 \text{ V}$ ,  $V_{EN} = 5 \text{ V}$  (unless otherwise noted)

|                        | PARAMETER                         | TEST CONDITION                                                                    | MIN   | TYP         | MAX  | UNIT  |

|------------------------|-----------------------------------|-----------------------------------------------------------------------------------|-------|-------------|------|-------|

| SUPPLY CUR             | RENT                              |                                                                                   |       |             |      |       |

| I <sub>V5</sub>        | V5 supply current                 | T <sub>A</sub> = 25°C, No load, V <sub>EN</sub> = 5 V                             |       | 560         |      | μA    |

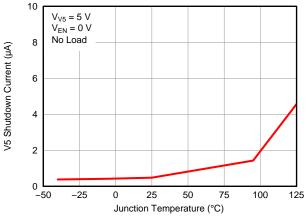

| I <sub>V5SDN</sub>     | V5 shutdown current               | T <sub>A</sub> = 25°C, No load, V <sub>EN</sub> = 0 V                             |       | 0.5         | 2.0  | μA    |

| VREF OUTPU             | т                                 |                                                                                   |       |             |      |       |

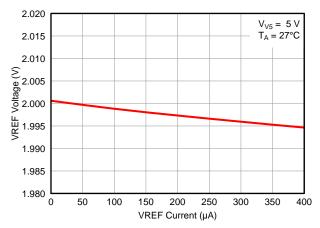

| V <sub>VREF</sub>      | Output voltage                    | I <sub>VREF</sub> = 0 μA wrt GSNS                                                 |       | 2.000       |      | V     |

| V                      | Output valtage telegone           | 0 μA ≤ I <sub>VREF</sub> < 30 μA, T <sub>A</sub> = 0°C to 85°C                    | -0.8% |             | 0.8% |       |

| $V_{VREF(tol)}$        | Output voltage tolerance          | 0 μA ≤ I <sub>VREF</sub> < 300 μA, T <sub>A</sub> = -40°C to 85°C                 | -1.2% |             | 1.2% |       |

| I <sub>VREF(ocl)</sub> | Current limit                     | V <sub>VREF-GSNS</sub> = 1.7 V                                                    | 0.4   | 1.0         |      | mA    |

| OUTPUT VOL             | TAGE                              |                                                                                   |       |             |      |       |

|                        |                                   | V <sub>REFIN</sub> = 0 V                                                          |       | 1.000       |      | V     |

| $V_{VSNS}$             | VSNS sense voltage                | V <sub>REFIN</sub> = 3.3 V                                                        |       | 1.050       |      | V     |

|                        |                                   | 0.5 V ≤ V <sub>REFIN</sub> ≤ 2 V                                                  |       | $V_{REFIN}$ |      | V     |

|                        |                                   | V <sub>REFIN</sub> = 0 V, 0°C ≤ T <sub>A</sub> ≤ 85°C                             | -9    |             | 9    |       |

|                        |                                   | V <sub>REFIN</sub> = 0 V, -40°C ≤ T <sub>A</sub> ≤ 85°C                           | -14   |             | 14   |       |

| V <sub>VSNS(tol)</sub> | VSNS regulation voltage tolerance | V <sub>REFIN</sub> = 3.3 V, 0°C ≤ T <sub>A</sub> ≤ 85°C                           | -9    |             | 9    | mV    |

|                        |                                   | $V_{REFIN} = 3.3 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ | -14   |             | 14   |       |

|                        |                                   | V <sub>REFIN</sub> = 0.5 V and V <sub>REFIN</sub> = 2.0 V                         | -5    |             | 5    |       |

| V <sub>REFIN1</sub>    | REFIN voltage for 1.00-V output   |                                                                                   |       |             | 0.3  | ٧     |

| V <sub>REFIN1P05</sub> | REFIN voltage for 1.05-V output   |                                                                                   | 2.2   |             |      | V     |

| V <sub>OFF_LPCMP</sub> | Loop comparator offset voltage    | V <sub>REFIN</sub> = 1 V, VSNS shorted to COMP                                    | -5    |             | 5    | mV    |

|                        | COMP clamp voltage                | V <sub>REFIN</sub> = 0 V, V <sub>VSNS</sub> = 0.95 V                              |       | 0.885       |      | ٧     |

| V <sub>COMPCLP</sub>   |                                   | V <sub>REFIN</sub> = 0 V, V <sub>VSNS</sub> = 1.05 V                              |       | 1.115       |      | ٧     |

| 9м                     | Error amplifier transconductance  | V <sub>REFIN</sub> = 0 V                                                          |       | 130         |      | μS    |

| I <sub>VSNS</sub>      | VSNS input current                | V <sub>VSNS</sub> = 1.05 V                                                        | -1    |             | 1    | μA    |

| I <sub>REFIN</sub>     | REFIN input current               | V <sub>REFIN</sub> = 0 V                                                          | -1    |             | 1    | μA    |

| I <sub>VSNS(dis)</sub> | VSNS discharge current            | V <sub>EN</sub> = 0 V, V <sub>VSNS</sub> = 0.5 V                                  | 5     | 12          |      | mA    |

| SWITCH MOD             | DE POWER SUPPLY (SMPS) FREQUEN    | ICY                                                                               |       |             |      |       |

|                        |                                   | V <sub>IN</sub> = 12 V, V <sub>VSNS</sub> = 1.8 V, V <sub>MODE</sub> = 2.5 V      |       | 400         |      |       |

|                        | Constability for account          | V <sub>IN</sub> = 12 V, V <sub>VSNS</sub> = 1.8 V, V <sub>MODE</sub> = 1.67 V     |       | 300         |      | 1.11= |

| f <sub>SW</sub>        | Switching frequency               | V <sub>IN</sub> = 12 V, V <sub>VSNS</sub> = 1.8 V, V <sub>MODE</sub> = 0.2 V      |       | 670         |      | kHz   |

|                        |                                   | V <sub>IN</sub> = 12 V, V <sub>VSNS</sub> = 1.8 V, V <sub>MODE</sub> = 0.033 V    |       | 500         |      |       |

| t <sub>ON(min)</sub>   | Minimum on time                   | DH rising to falling <sup>(1)</sup>                                               |       | 60          |      |       |

| t <sub>OFF(min)</sub>  | Minimum off time                  | DH falling to rising                                                              |       | 320         |      | ns    |

| MOSFET DRI             | VERS                              |                                                                                   |       |             |      |       |

| D                      | Dilirosistanos                    | Source, I <sub>DH</sub> = -50 mA                                                  |       | 1.6         | 3.0  |       |

| $R_{DH}$               | DH resistance                     | Sink, I <sub>DH</sub> = 50 mA                                                     |       | 0.6         | 1.5  | ^     |

| D                      | Di registance                     | Source, I <sub>DL</sub> = -50 mA                                                  |       | 0.9         | 2.0  | Ω     |

| $R_{DL}$               | DL resistance                     | Sink, I <sub>DL</sub> = 50 mA                                                     |       | 0.5         | 1.2  |       |

| 4                      | Dood time                         | DH-off to DL-on                                                                   |       | 10          |      |       |

| t <sub>DEAD</sub>      | Dead time                         | DL-off to DH-on                                                                   |       | 20          |      | ns    |

| INTERNAL B             | OOT STRAP SWITCH                  |                                                                                   |       |             |      |       |

| V <sub>FBST</sub>      | Forward voltage                   | V <sub>V5-BST</sub> , T <sub>A</sub> = 25°C, I <sub>F</sub> = 10 mA               |       | 0.1         | 0.2  | V     |

| I <sub>BSTLK</sub>     | BST leakage current               | T <sub>A</sub> = 25°C, V <sub>BST</sub> = 33 V, V <sub>SW</sub> = 28 V            |       | 0.01        | 1.5  | μA    |

<sup>(1)</sup> Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range,  $V_{V5} = 5 \text{ V}$ ,  $V_{MODE} = 0 \text{ V}$ ,  $V_{EN} = 5 \text{ V}$  (unless otherwise noted)

|                         | PARAMETER                                       | TEST CONDITION                                                                | MIN  | TYP  | MAX      | UNIT   |  |

|-------------------------|-------------------------------------------------|-------------------------------------------------------------------------------|------|------|----------|--------|--|

| LOGIC THRE              | ESHOLD                                          |                                                                               |      |      |          |        |  |

| I <sub>MODE</sub>       | MODE source current                             |                                                                               | 15.6 | 16.7 | 17.8     | μΑ     |  |

|                         |                                                 | MODE 0-1                                                                      | 113  | 143  | 173      |        |  |

|                         |                                                 | MODE 1-2                                                                      | 253  | 283  | 313      |        |  |

|                         |                                                 | MODE 2-3                                                                      | 433  | 458  | 483      |        |  |

| $V_{THMODE}$            | MODE threshold voltage                          | MODE 3-4                                                                      | 644  | 667  | 690      | mV     |  |

|                         |                                                 | MODE 4-5                                                                      | 914  | 949  | 984      |        |  |

|                         |                                                 | MODE 5-6                                                                      | 1329 | 1369 | 1409     |        |  |

|                         |                                                 | MODE 6-7                                                                      | 1950 | 2000 | 2050     | 1      |  |

| V <sub>LL</sub>         | EN low-level voltage                            |                                                                               |      |      | 0.5      |        |  |

| V <sub>LH</sub>         | EN high-level voltage                           |                                                                               | 1.8  |      |          | V      |  |

| V <sub>LHYST</sub>      | EN hysteresis voltage                           |                                                                               |      | 0.25 |          | 1      |  |

| I <sub>LLK</sub>        | EN input leakage current                        |                                                                               | -1   | 0    | 1        | μA     |  |

| SOFT STAR               |                                                 |                                                                               |      |      |          |        |  |

| t <sub>SS</sub>         | Soft-start time                                 | Internal soft-start time                                                      |      | 1.1  |          | ms     |  |

|                         | DD COMPARATOR                                   |                                                                               |      |      |          |        |  |

|                         |                                                 | PGOOD in from higher                                                          | 106% | 108% | 110%     |        |  |

|                         | PGOOD threshold                                 | PGOOD in from lower                                                           | 90%  | 92%  | 94%      | 1      |  |

| $V_{THPG}$              |                                                 | PGOOD out to higher                                                           | 114% | 116% | 118%     | 1      |  |

|                         |                                                 | PGOOD out to lower                                                            | 82%  | 84%  | 86%      | 1      |  |

| I <sub>PG</sub>         | PGOOD sink current                              | V <sub>PGOOD</sub> = 0.5 V                                                    | 3    | 6    |          | mA     |  |

| 'PG                     | T CCC S GITH GUITOIN                            | Delay for PGOOD in                                                            | 0.8  | 1.0  | 1.2      | ms     |  |

| t <sub>PGDLY</sub>      | PGOOD delay time                                | Delay for PGOOD out, with 100 mV over drive                                   | 0.0  | 0.25 | 1.2      | μs     |  |

| tocoupos                | PGOOD start-up delay                            | PGOOD comparator wake-up delay                                                |      | 2.5  |          | ms     |  |

| t <sub>PGCMPSS</sub>    | PGOOD leakage current                           | 1 GOOD comparator wake-up delay                                               | -1   | 0    | 1        | μA     |  |

| CURRENT D               |                                                 |                                                                               | -1   | 0    | <u>'</u> | μΛ     |  |

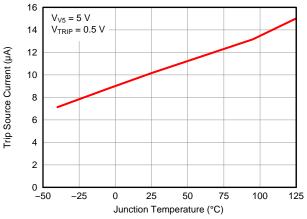

|                         | TRIP source current                             | T <sub>A</sub> = 25°C, V <sub>TRIP</sub> = 0.4 V, R <sub>DS(on)</sub> sensing | 9    | 10   | 11       | μA     |  |

| I <sub>TRIP</sub>       |                                                 | TA = 25 C, VTRIP = 0.4 V, NDS(on) Sensing                                     | 9    |      | - 11     |        |  |

| TC <sub>ITRIP</sub> (2) | TRIP source current temperature coefficient (2) | R <sub>DS(on)</sub> sensing                                                   |      | 4700 |          | ppm/°C |  |

| V <sub>TRIP</sub>       | V <sub>TRIP</sub> voltage range                 | R <sub>DS(on)</sub> sensing                                                   | 0.2  |      | 3        | V      |  |

|                         |                                                 | V <sub>TRIP</sub> = 3.0 V, R <sub>DS(on)</sub> sensing                        | 360  | 375  | 390      |        |  |

| V <sub>OCL</sub>        | Current limit threshold                         | V <sub>TRIP</sub> = 1.6 V, R <sub>DS(on)</sub> sensing                        | 190  | 200  | 210      | mV     |  |

|                         |                                                 | V <sub>TRIP</sub> = 0.2 V, R <sub>DS(on)</sub> sensing                        | 20   | 25   | 30       | -      |  |

|                         |                                                 | V <sub>TRIP</sub> = 3.0 V, R <sub>DS(on)</sub> sensing                        | -390 | -375 | -360     |        |  |

| V <sub>OCLN</sub>       | Negative current limit threshold                | $V_{TRIP} = 1.6 \text{ V}, R_{DS(on)} \text{ sensing}$                        | -212 | -200 | -188     | mV     |  |

|                         | · ·                                             | $V_{TRIP} = 0.2 \text{ V, } R_{DS(on)} \text{ sensing}$                       | -30  | -25  | -20      | 1      |  |

| V <sub>RTRIP</sub>      | Resistor sense trip voltage                     | Resistor sensing                                                              |      | 25   |          | mV     |  |

| V <sub>ZC</sub>         | Zero cross detection offset                     |                                                                               |      | 0    |          | mV     |  |

<sup>(2)</sup> Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range,  $V_{V5} = 5 \text{ V}$ ,  $V_{MODE} = 0 \text{ V}$ ,  $V_{EN} = 5 \text{ V}$  (unless otherwise noted)

|                       | PARAMETER                   | TEST CONDITION                      | MIN  | TYP  | MAX  | UNIT |

|-----------------------|-----------------------------|-------------------------------------|------|------|------|------|

| PROTECTIO             | NS                          |                                     |      |      | •    |      |

| V                     | VE LIVI O threehold voltage | Wake-up                             | 4.2  | 4.4  | 4.5  | .,   |

| V <sub>UVLO</sub>     | V5 UVLO threshold voltage   | Shutdown                            | 3.7  | 3.9  | 4.1  | V    |

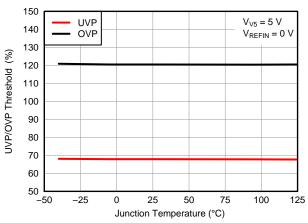

| V <sub>OVP</sub>      | OVP threshold voltage       | OVP detect voltage                  | 118% | 120% | 122% |      |

| t <sub>OVPDLY</sub>   | OVP propagation delay       | With 100 mV over drive              |      | 370  |      | ns   |

| V <sub>UVP</sub>      | UVP threshold voltage       | UVP detect voltage                  | 66%  | 68%  | 70%  |      |

| t <sub>UVPDLY</sub>   | UVP delay                   |                                     |      | 1    |      | ms   |

| t <sub>UVPENDLY</sub> | UVP enable delay            |                                     |      | 1.4  |      | ms   |

| THERMAL S             | HUTDOWN                     |                                     |      |      |      |      |

| _                     | Thermal shutdown threshold  | Shutdown temperature <sup>(3)</sup> |      | 140  |      | °C   |

| I <sub>SDN</sub>      | mermai shuldown threshold   | Hysteresis (3)                      |      | 10   |      | C    |

<sup>(3)</sup> Ensured by design. Not production tested.

## **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| PIN         | ı   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

|-------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

| BST         | 13  | I   | High-side MOSFET gate driver bootstrap voltage input. Connect a capacitor from the BST pin to the SW pin.                                                                                                                                                                                                                                       |

| COMP        | 5   | ı   | Connection for the DC compensation integrator for improved load-line performance. Connect a capacitor from this pin to the VSNS pin (when operating in D-CAP2 mode), or to the positive terminal of the output capacitor (when operating in D-CAP mode). Connect directly to the VSNS pin without capacitor to disable the integrator function. |

| DH          | 11  | 0   | High-side MOSFET gate driver output.                                                                                                                                                                                                                                                                                                            |

| DL          | 10  | 0   | Low-side MOSFET gate driver output.                                                                                                                                                                                                                                                                                                             |

| EN          | 14  | I   | Enable pin. 3.3-V I/O level, 100 ns de-bounce. Short to GND to disable the device.                                                                                                                                                                                                                                                              |

| GND         | 7   | _   | Device analog ground; Connect to a quiet point on the system GND plane                                                                                                                                                                                                                                                                          |

| GSNS        | 3   | ı   | Voltage sense return tied directly to the GND sense point of the load. Short to GND if remote sense is not used.                                                                                                                                                                                                                                |

| MODE        | 15  | ı   | Connect a resistor to GND to configure switching frequency, control mode and current sense scheme. (See Table 2)                                                                                                                                                                                                                                |

| PGND        | 8   | _   | Synchronous low-side MOSFET gate driver return. Also serve as the current sensing input (+). Connect to the GND pin as close as possible to the device.                                                                                                                                                                                         |

| PGOOD       | 16  | 0   | Powergood signal open drain output. PGOOD goes high when the output voltage is within the target range.                                                                                                                                                                                                                                         |

| REFIN       | 2   | I   | Output voltage setting pin. See the VREF and REFIN, Output Voltage section.                                                                                                                                                                                                                                                                     |

| SW          | 12  | I/O | High-side MOSFET gate driver return. R <sub>DS(on)</sub> current sensing input (–) when using R <sub>DS(on)</sub> current sensing.                                                                                                                                                                                                              |

| TRIP        | 6   | ı   | Current sense comparator input (-) for resistor current sensing. Or overcurrent threshold setting pin for $R_{DS(on)}$ current sensing if connected to GND through an OCL setting resistor. For $R_{DS(on)}$ current sensing operation, 10 $\mu$ A at room temperature, $T_C$ =4700ppm/°C, is sourced to set the trip voltage.                  |

| VSNS        | 4   | I   | Voltage sense line tied directly to the load voltage sense point.                                                                                                                                                                                                                                                                               |

| VREF        | 1   | 0   | 2.0-V ±0.8% voltage reference output.                                                                                                                                                                                                                                                                                                           |

| V5          | 9   | 1   | 5V power supply input for internal circuits and MOSFET gate drivers.                                                                                                                                                                                                                                                                            |

| Thermal pad | _   | _   | Thermal pad. Connect directly to system GND plane with multiple vias.                                                                                                                                                                                                                                                                           |

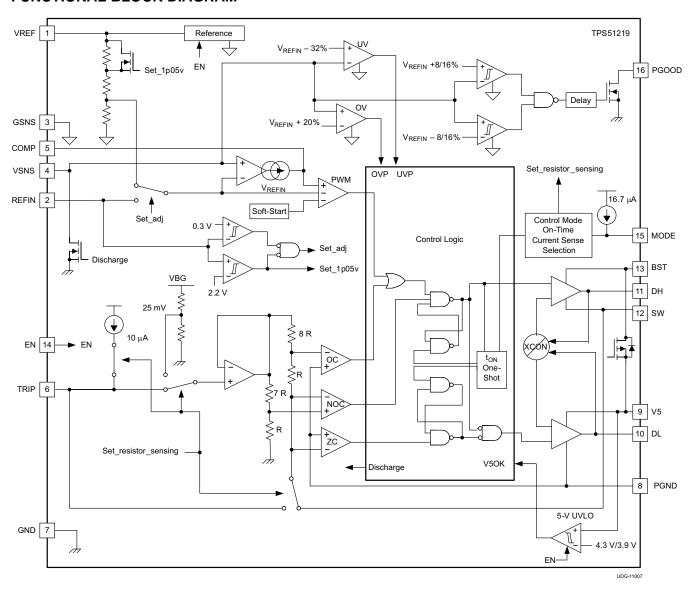

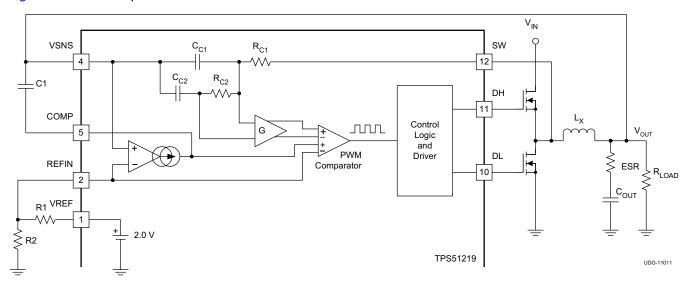

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. V5 Supply Current vs Junction Temperature

Figure 3. Current Sense Current vs Junction Temperature

Figure 5. VREF Load Regulation

Figure 2. V5 Shutdown Current vs Junction Temperature

Figure 4. OVP/UVP Threshold vs Junction Temperature

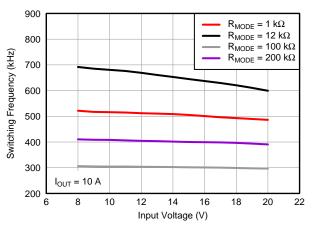

Figure 6. Switching Frequency vs Input Voltage

Figure 11 and Figure 12 refer to the application schematic in Figure 33.

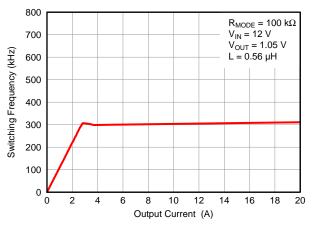

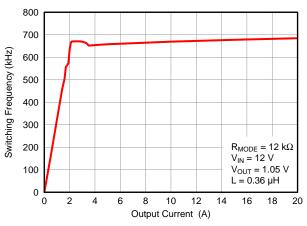

Figure 7. Switching Frequency vs Load Current

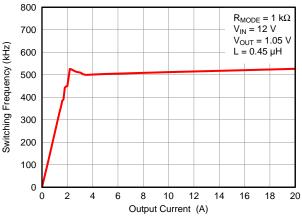

Figure 9. Switching Frequency vs Load Current

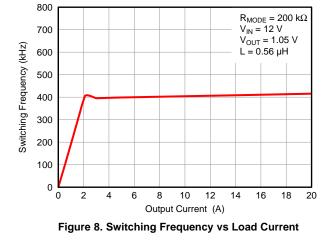

Figure 10. Switching Frequency vs Load Current

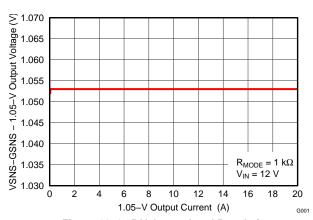

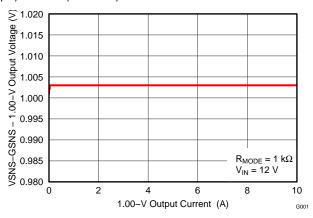

Figure 11. 1.05-V Output Load Regulation

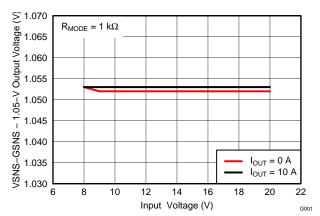

Figure 12. 1.05-V Output Line Regulation

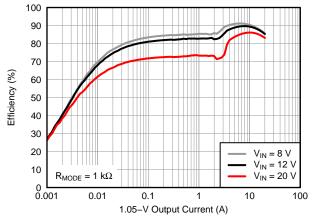

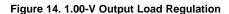

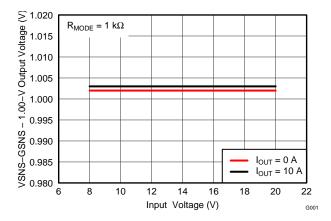

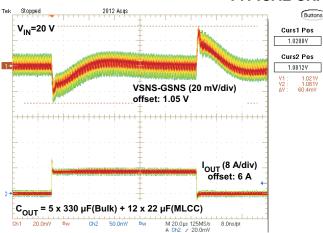

Figure 11, Figure 12, and Figure 13 refer to the application schematic in Figure 33. Figure 14, Figure 15 and Figure 16, refer to the application schematic in Figure 33 except the parameters of L1 (0.56  $\mu$ H), C7 (2 × 330  $\mu$ F) and Q3 (not used).

Figure 13. 1.05-V Output Efficiency

Figure 15. 1.00-V Output Line Regulation

Figure 16. 1.00-V Output Efficiency

Curs1 Pos

975.6mV

Buttons

#### TYPICAL CHARACTERISTICS

V<sub>IN</sub>=20 V

Curs2 Pos

1.032V

V1. 975 βmV

ΔV 55. 4mV

Cout = 2 x 330 μF(Bulk) + 12 x 22 μF(MLCC)

Cot 200mV by Ch2 50.0mV by M 200.μs 125MS/s 8.0ms/st

VSNS-GSNS (20 mV/div)

offset: 1.00 V

Figure 17. 1.05-V Load Transient Response

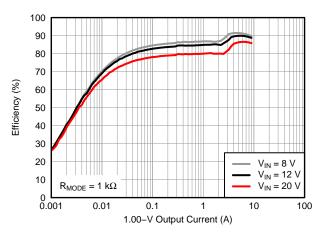

Figure 18. 1.00-V Load Transient Response

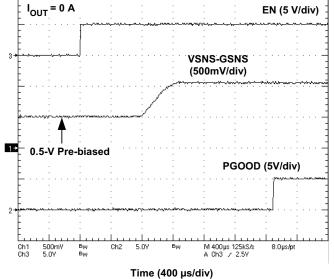

Figure 19. 1.05-V Startup Waveforms

Figure 20. 1.05-V Startup Waveforms (0.5-V Pre-Biased)

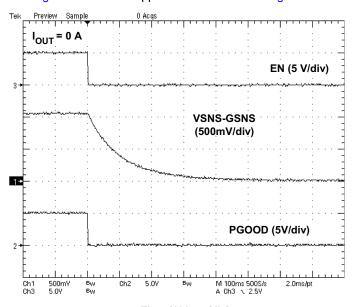

Figure 22 refers to application schematic of Figure 33.

Time (100 ms/div)

Figure 21. 1.05-V Soft-stop Waveforms

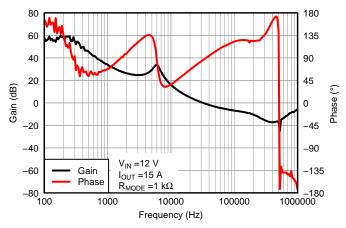

Figure 22. Bode Plot, V<sub>OUT</sub>=1.05 V

#### **APPLICATION INFORMATION**

## **Swtich Mode Power Supply Control**

The TPS51219 is a high performance, single-synchronous step-down controller with differential voltage feedback. The TPS51219 realizes accurate regulation at the specific load point over wide load range with the combination of three functions.

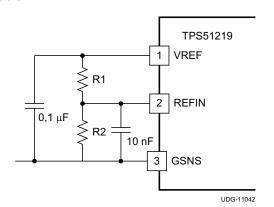

- 2-V Reference with 0.8% Tolerance. Internal voltage divider provides precise reference (See Table 1 in the VREF and REFIN, Output Voltage section). A value of 0.1µF is recommended as the decoupling capacitance between VREF and GSNS pins.

- Integrator. Feedback capacitance connected from the output (COMP pin) to the input (VSNS pin) of the error amplifier comprises integrator, which increases gain at DC to low frequency region and improves load regulation of the output voltage. 10nF is recommended as the capacitance between VSNS and COMP pins.

- **Differential remote sensing**. Differential feedback provides precise output voltage control at the point of load. Connect VSNS and GSNS directly to output voltage sense point and ground return point at the load device, respectively. Short GSNS to GND if remote sense is not used.

The TPS51219 supports two control architectures, D-CAP<sup>TM</sup> mode and D-CAP2<sup>TM</sup> mode. Both control modes do not require complex external compensation networks and are suitable for designs with small external components counts. The D-CAP<sup>TM</sup> mode provides fast transient response with appropriate amount of equivalent series resistance (ESR) on the output capacitors. The D-CAP2<sup>TM</sup> mode is dedicated for a configuration with very low ESR output capacitors such as multi-layer ceramic capacitors (MLCC). For the both modes, an adaptive on-time control scheme is used to achieve pseudo-constant frequency. The TPS51219 adjusts the on-time ( $t_{ON}$ ) to be inversely proportional to the input voltage ( $v_{IN}$ ) and proportional to the SMPS output voltage ( $v_{OUT}$ ). The switching frequency remains nearly constant over the variation of input voltage at the steady-state condition. Control modes and switching frequency are selected by the MODE pin described in Table 2.

## **VREF and REFIN, Output Voltage**

The device provides a 2.0-V,  $\pm 0.8\%$  accurate, voltage reference from VREF. This output has a 300- $\mu$ A current capability to drive the REFIN input voltage through a voltage divider circuit. A capacitor with a value of 0.1- $\mu$ F or larger should be attached close to the VREF terminal.

The SMPS output voltage is defined by REFIN voltage, within the range between 0.5 V and 2.0 V, programmed by the resister-divider connected between VREF and GSNS. (See Figure 23 and External Components Selection section.) A few nano-farads of capacitance from REFIN to GSNS is recommended for stable operation. A voltage divider and a filter capacitor to this pin should be referenced to GSNS. Fixed output voltage can be set as shown in Table 1.

Figure 23. Voltage Reference Connections

**Table 1. Output Voltage Selection**

| REFIN VOLTAGE (V) | OUTPUT VOLTAGE (V) |

|-------------------|--------------------|

| 3.3               | 1.05               |

| GSNS              | 1.00               |

| Resistor Divider  | Adjustable         |

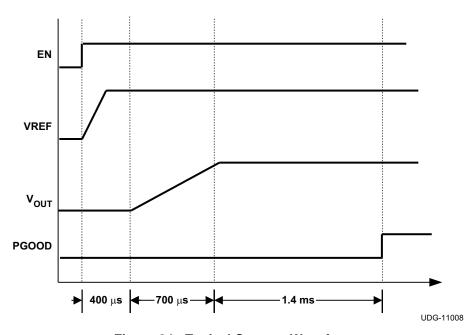

## Soft-Start and Powergood

Provide a voltage supply to VIN and V5 before asserting EN to high. TPS51219 provides integrated soft-start functions to suppress in-rush current at start-up. The soft-start is achieved by controlling internal reference voltage ramping up. Figure 24 shows the start-up waveforms. The switching regulator waits for 400 $\mu$ s after EN assertion. The MODE pin voltage is read in this period. A typical  $V_{OUT}$  ramp up duration is 700  $\mu$ s.

THe TPS51219 has a powergood open-drain output that indicates the  $V_{\text{OUT}}$  voltage is within the target range. The target voltage window and transition delay times of the PGOOD comparator are  $\pm 8\%$  (typ) and 1-ms delay for assertion (low to high), and  $\pm 16\%$  (typ) and 2- $\mu$ s delay for de-assertion (high to low) during running. The PGOOD start-up delay is 2.5 ms after EN is asserted to high. The time constant, which is composed of the REFIN capacitor and a resistor divider, needs to be short enough to reach the target value before PGOOD comparator enabled.

Figure 24. Typical Start-up Waveforms

## **MODE Pin Configuration**

The TPS51219 reads the MODE pin voltage when the EN signal is raised high and stores the status in a register. A 16.7-μA current is sourced from the MODE pin during this time to read the voltage across the resistor connected between the pin and GND. Table 2 shows resistor values, corresponding control mode, switching frequency and current sense operation configurations.

**Table 2. MODE Selection**

| MODE NO. | RESISTANCE BETWEEN MODE AND GND ( $k\Omega$ ) | CONTROL<br>MODE | SWITCHING<br>FREQUENCY (kHz) | CURRENT SENSE OPERATION |

|----------|-----------------------------------------------|-----------------|------------------------------|-------------------------|

| 7        | 200                                           |                 | 400                          | D                       |

| 6        | 100                                           | D-CAP™          | 300                          | R <sub>DS(on)</sub>     |

| 5        | 68                                            | D-CAP ····      | 300                          | Decistor                |

| 4        | 47                                            |                 | 400                          | Resistor                |

| 3        | 33                                            |                 | 500                          | Desistes                |

| 2        | 22                                            | D CADOTM        | 670                          | Resistor                |

| 1        | 12                                            | D-CAP2™         | 670                          | D                       |

| 0        | 1                                             |                 | 500                          | R <sub>DS(on)</sub>     |

#### **D-CAP™ Mode**

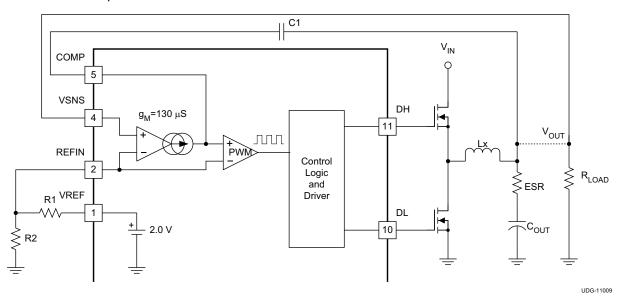

Figure 25 shows a simplified model of D-CAP™ mode architecture in the TPS51219.

Figure 25. Simplified D-CAP™ Model

The transconductance amplifier and the capacitance C1 configure an integrator. The VSNS voltage is compared with REFIN voltage. Ripple voltage generated by ESR of the output capacitance is fed back through the C1 so that C1 should be properly connected to the positive terminal of output capacitor, not at the remote point of load. The PWM comparator creates a set signal to turn on the high-side MOSFET each cycle. The D-CAP™ mode offers flexibility on output inductance and capacitance selections with ease-of-use without complex feedback loop calculation and external components. However, it does require sufficient amount of ESR that represents inductor current information for stable operation and good jitter performance. Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended.

The requirement for loop stability is simple and is described in Equation 1. The 0-dB frequency,  $f_0$ , is recommended to be lower than 1/3 of the switching frequency to secure proper phase margin. The integrator time constant should be long enough compared to  $f_0$ , for example one decade low, as described in Equation 2.

$$f_0 = \frac{1}{2\pi \times \text{ESR} \times C_{OUT}} \leq \frac{f_{SW}}{3}$$

where

- · ESR is the effective series resistance of the output capacitor

- C<sub>OUT</sub> is the capacitance of the output capacitor

$$\frac{9_{\mathsf{M}}}{2\pi \times \mathsf{C1}} \leq \frac{f_0}{10}$$

where

g<sub>M</sub> is transconductance of the error amplifier (typically 130 μS)

(1)

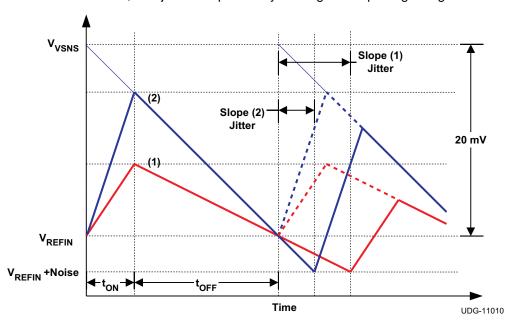

Jitter is another attribute caused by signal-to-noise ratio of the feedback signal. One of the major factors that determine jitter performance in D-CAP™ mode is the down-slope angle of the VSNS ripple voltage. Figure 26 shows, in the same noise condition, that jitter is improved by making the slope angle larger.

Figure 26. Ripple Voltage Slope and Jitter Performance

For a good jitter performance, use the recommended down slope of approximately 20 mV per switching period as shown in Figure 26 and Equation 3.

$$\frac{V_{OUT} \times ESR}{f_{SW} \times L_X} \ge 20 \,\text{mV}$$

where

- V<sub>OUT</sub> is the SMPS output voltage

- L<sub>X</sub> is the inductance (3)

(4)

## **D-CAP2™ Mode Operation**

Figure 27 shows simplified model of D-CAP2™ architecture.

Figure 27. Simplified Modulator Using D-CAP2™ Mode

When the TPS51219 operates in D-CAP2™ mode, connect the COMP and VSNS pins as shown in Figure 27. The transconductance amplifier and the capacitance C1 configures the integrator. The D-CAP2™ mode in the TPS51219 includes an internal feedback network enabling the use of very low ESR output capacitor(s) such as multi-layer ceramic capacitors (MLCC). The role of the internal network is to sense the ripple component of the inductor current information and then combine it with the voltage feedback signal.

Using  $R_{C1}=R_{C2}\equiv R_C$  and  $C_{C1}=C_{C2}\equiv C_C$ , 0-dB frequency of the D-CAP2<sup>TM</sup> mode is given by Equation 4.  $f_0$  is recommended to be lower than 1/3 of the switching frequency to secure proper phase margin. The integrator time constant should be long enough compared to  $f_0$ , for example one decade low, as described in Equation 5.

$$f_0 = \frac{R_C \times C_C}{2\pi \times G \times L_X \times C_{OUT}} \leq \frac{f_{SW}}{3}$$

where

• G is gain of the amplifier which amplifies the ripple current information generated by the compensation circuit

$$\frac{g_{\mathsf{M}}}{2\pi \times \mathsf{C1}} \le \frac{t_0}{10} \tag{5}$$

The typical G value is 0.25, and typical  $R_CC_C$  time constant values for 500 kHz and 670 kHz operation are 32 µs and 23 µs, respectively.

For example, when  $f_{SW}=500$  kHz and  $L_X$ =0.45  $\mu$ H,  $C_{OUT}$  should be larger than 272  $\mu$ F. At the selection of capacitor, pay attention to its characteristics. For MLCC use X5R or better dielectric and take into account derating of the capacitance by both DC bias and AC bias. When derating by DC bias and AC bias are 80% and 50%, respectively, the effective derating is 40% because 0.8 x 0.5 = 0.4. The capacitance of specialty polymer capacitors may change depending on the operating frequency. Consult capacitor manufacturers for specific characteristics.

## **Light-Load Operation**

In auto-skip mode, the TPS51219 SMPS control logic automatically reduces its switching frequency to improve light-load efficiency. To achieve this intelligence, a zero cross detection comparator is used to prevent negative inductor current by turning off the low-side MOSFET. Equation 6 shows the boundary load condition of this skip mode and continuous conduction operation.

$$I_{LOAD(LL)} = \frac{\left(V_{IN} - V_{OUT}\right)}{2 \times L_X} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}}$$

(6)

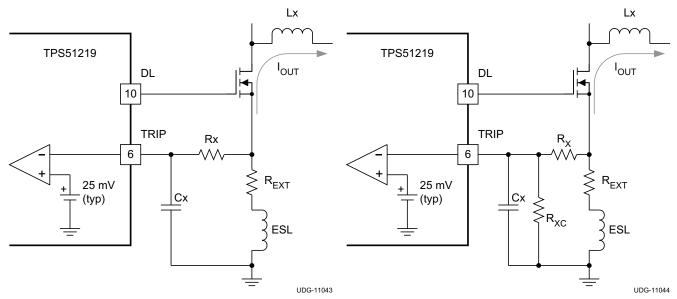

## **Current Sensing**

In order to provide both cost effective solution and good accuracy, TPS51219 supports both of MOSFET  $R_{DS(on)}$  sensing and external resistor sensing. For  $R_{DS(on)}$  sensing scheme, TRIP pin should be connected to GND through the trip voltage setting resistor,  $R_{TRIP}$ . In this scheme, TRIP terminal sources 10µA of  $I_{TRIP}$  current and the trip level is set to 1/8 of the voltage across the  $R_{TRIP}$ . The inductor current is monitored by the voltage between the PGND pin and the SW pin so that the SW pin is connected to the drain terminal of the low-side MOSFET.  $I_{TRIP}$  has a 4700ppm/°C temperature slope to compensate the temperature dependency of the  $R^{DS(on)}$ . For resistor sensing scheme, an appropriate current sensing resistor should be connected between the source terminal of the low-side MOSFET and PGND. The TRIP pin is connected to the MOSFET source terminal node. The inductor current is monitored by the voltage between PGND pin and TRIP pin. In either scheme, PGND is used as the positive current sensing node so that PGND should be connected to the proper current sensing device, i.e. the sense resistor or the source terminal of the low-side MOSFET.

#### **Overcurrent Protection**

TPS51219 has cycle-by-cycle overcurrent limiting protection. The inductor current is monitored during the off-state and the controller maintains the off-state when the inductor current is larger than the overcurrent trip level. The trip level and current sense operation are determined by the MODE pin setting and TRIP pin connection (See Table 2 and Current Sensing section). For  $R_{DS(on)}$  sensing scheme, TRIP terminal sources 10  $\mu$ A and the trip level is set to 1/8 of the voltage across this  $R_{TRIP}$  resistor. The overcurrent trip level,  $V_{OCTRIP}$ , is determined by Equation 7.

$$V_{OCTRIP} = R_{TRIP} \times \left(\frac{I_{TRIP}}{8}\right)$$

(7)

For a resistor sensing scheme, the trip level, V<sub>OCTRIP</sub>, is a fixed value of 25 mV.

Because the comparison is made during the off-state,  $V_{\text{OCTRIP}}$  sets the valley level of the inductor current. The load current OCL level,  $I_{\text{OCL}}$ , can be calculated by considering the inductor ripple current.

Overcurrent limiting using R<sub>DS(on)</sub> sensing is shown in Equation 8.

$$I_{OCL} = \left(\frac{V_{OCTRIP}}{R_{DS(on)}}\right) + \frac{I_{IND(ripple)}}{2} = \left(\frac{V_{OCTRIP}}{R_{DS(on)}}\right) + \frac{1}{2} \times \frac{V_{IN} - V_{OUT}}{L_X} \times \frac{V_{OUT}}{f_{SW} \times V_{IN}}$$

where

I<sub>IND(ripple)</sub> is inductor ripple current

(8)

Overcurrent limiting using resistor sensing is shown in Equation 9.

$$I_{OCL} = \left(\frac{25 \, \text{mV}}{R_{EXT}}\right) + \frac{I_{IND(ripple)}}{2} = \left(\frac{25 \, \text{mV}}{R_{EXT}}\right) + \frac{1}{2} \times \frac{V_{IN} - V_{OUT}}{L_X} \times \frac{V_{OUT}}{f_{SW} \times V_{IN}}$$

where

- I<sub>IND(ripple)</sub> is inductor ripple current

- R<sub>EXT</sub> is the external current sense resistance

(9)

In an overcurrent condition, the current to the load exceeds the current to the output capacitor, thus the output voltage tends to fall down. Eventually, it crosses the undervoltage protection threshold and shuts down.

## Overvoltage and Undervoltage Protection

The TPS51219 sets the overvoltage protection (OVP) when VSNS voltage reaches a level 20% (typ) higher than the REFIN voltage. When an OV event is detected, the controller changes the output target voltage to 0 V. This usually turns off DH and forces DL to be on. When the inductor current begins to flow through the low-side MOSFET and reaches the negative OCL, DL is turned off and DH is turned on, for a minimum on-time.

After the minimum on-time expires, DH is turned off and DL is turned on again. This action minimizes the output node undershoot due to LC resonance. When the VSNS reaches 0 V, the driver output is latched as DH off, DL on.

The undervoltage protection (UVP) latch is set when the VSNS voltage remains lower than 68% (typ) of the REFIN voltage for 1 ms or longer. In this fault condition, the controller latches DH low and DL low and discharges the  $V_{OUT}$ . UVP detection function is enabled after 1.2 ms of SMPS operation to ensure startup.

To release the OVP and UVP latches, toggle EN or adjust the V5 voltage down and up beyond the undervoltage lockout threshold.

## **V5 Undervoltage Lockout Protection**

TPS51219 has a 5-V supply undervoltage lockout protection (UVLO) threshold. When the V5 voltage is lower than UVLO threshold voltage, typically 3.9 V,  $V_{OUT}$  is shut off. This is a non-latch protection.

#### Thermal Shutdown

TPS51219 includes an internal temperature monitor. If the temperature exceeds the threshold value, 140°C (typ),  $V_{OUT}$  is shut off. The state of  $V_{OUT}$  is open at thermal shutdown. This is a non-latch protection and the operation is restarted with soft-start sequence when the device temperature is reduced by 10°C (typ).

## **External Components Selection**

The external components selection is simple in D-CAP™ mode.

#### 1. DETERMINE THE VALUE OF R1 AND R2

The output voltage is determined by the value of the voltage-divider resistor, R1 and R2 as shown in Figure 25. R1 is connected between VREF and REFIN pins, and R2 is connected between the REFIN pin and GSNS. Setting R1 as  $10-k\Omega$  is a good starting point. Determine R2 using Equation 10.

$$R2 = \frac{R1}{\left(\frac{2.0}{V_{OUT} - \left(\frac{I_{IND(ripple)} \times ESR}{2}\right)} - 1\right)}$$

(10)

#### 2. CHOOSE THE INDUCTOR

The inductance value should be determined to yield a ripple current of approximately ¼ to ½ of maximum output current. Larger ripple current increases output ripple voltage and improves the signal-to-noise ratio and helps stable operation.

$$L_{X} = \frac{1}{I_{\text{IND(ripple)}} \times f_{\text{SW}}} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}} = \frac{3}{I_{\text{O(max)}} \times f_{\text{SW}}} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(11)

The inductor needs a low direct current resistance (DCR) to achieve good efficiency, as well as enough room above peak inductor current before saturation. The peak inductor current can be estimated in Equation 12.

$$I_{IND(peak)} = \frac{V_{TRIP}}{8 \times R_{DS(on)}} + \frac{1}{L_X \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}}$$

(12)

#### 3. CHOOSE THE OCL SETTING RESISTANCE

## R<sub>TRIP</sub> for R<sub>DS(on)</sub> Sensing

Combining Equation 7 and Equation 8, R<sub>TRIP</sub> can be obtained using Equation 13.

$$R_{TRIP} = \frac{8 \times \left(I_{OCL} - \left(\frac{\left(V_{IN} - V_{OUT}\right)}{\left(2 \times L_X\right)}\right) \times \frac{V_{OUT}}{\left(f_{SW} \times V_{IN}\right)}\right) \times R_{DS(on)}}{I_{TRIP}}$$

(13)

## R<sub>EXT</sub> for Resistor Setting

Combining Equation 7 and Equation 9, R<sub>EXT</sub> can be obtained using Equation 14.

$$R_{EXT} = \frac{25mV}{I_{OCL} - \left(\frac{V_{IN} - V_{OUT}}{2 \times L_X}\right) \times \frac{V_{OUT}}{f_{SW} \times V_{IN}}}$$

(14)

For more accurate current sensing with an external resistor, the following technique is recommended. Adding an RC filter to cancel the parasitic inductance (ESL) of resistor, this filter value is calculated using Equation 15.

$$C_{X} \times R_{X} = \frac{ESL}{R_{EXT}}$$

(15)

The time-constant of  $C_X$  and  $R_X$  should match the one of ESL and  $R_{EXT}$ . Even when  $C_X$  is not used, an  $R_X$  of 100  $\Omega$  is recommended for noise suppression.

Figure 28. Resistor Sensing with Compensation

Figure 29. Adjustment of Overcurrent Limitation in Resistor Sensing

A voltage divider can be configured to adjust for overcurrent limitation, as described in Figure 29. For  $R_X$ ,  $R_{XC}$  and  $C_X$  can be calculated as shown in Equation 16, and the overcurrent limitation value can be calculated as shown in Equation 17.

$$C_{X} \times \left( R_{X} \| R_{XC} \right) = \frac{ESL}{R_{EXT}}$$

(16)

$$I_{OCL} = \left(\frac{25 \text{mV}}{R_{EXT}}\right) + \frac{R_X + R_{XC}}{R_{XC}} + \left(\frac{V_{IN} - V_{OUT}}{2 \times L_X}\right) \times \frac{V_{OUT}}{f_{SW} \times V_{IN}}$$

(17)

Therefore, R<sub>EXT</sub> can be obtained using Equation 18.

$$R_{EXT} = \frac{25 \text{mV}}{I_{OCL} - \left(\frac{\left(V_{IN} - V_{OUT}\right)}{2 \times L_X}\right) \times \frac{V_{OUT}}{f_{SW} \times V_{IN}}} \times \left(\frac{\left(R_X + R_{XC}\right)}{R_{XC}}\right)$$

(18)

## 4. CHOOSE THE OUTPUT CAPACITORS

#### D-CAP™ Mode

Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended. Determine the ESR value to meet small signal stability and recommended ripple voltage. A quick reference is shown in Equation 19 and Equation 20.

$$f_0 = \frac{1}{2\pi \times \text{ESR} \times C_{\text{OUT}}} \le \frac{f_{\text{SW}}}{3}$$

$$\frac{g_{\text{M}}}{2\pi \times C1} \le \frac{f_0}{10}$$

(19)

where

g<sub>M</sub> is 130 μS (typ)

C1 is the capacitance connected between the VSNS and COMP pins

$$\frac{V_{OUT} \times ESR}{f_{SW} \times Lx} \ge 20 \,\text{mV} \tag{21}$$

(20)

## **D-CAP2™** Mode

Determine output capacitance to meet small signal stability as shown in Equation 22 and Equation 23.

$$\frac{\left(R_{C} \times C_{C}\right)}{2\pi \times G \times L_{X} \times C_{OUT}} \leq \frac{f_{SW}}{3}$$

where

$$G = 0.25$$

$$\frac{g_{\text{M}}}{2\pi \times \text{C1}} \le \frac{f_0}{10}$$

(22)

where

• the

$$R_C \times C_C$$

time constant is 32 µs for operation at 500 kHz. (23 µs for operation at 670 kHz) (23)

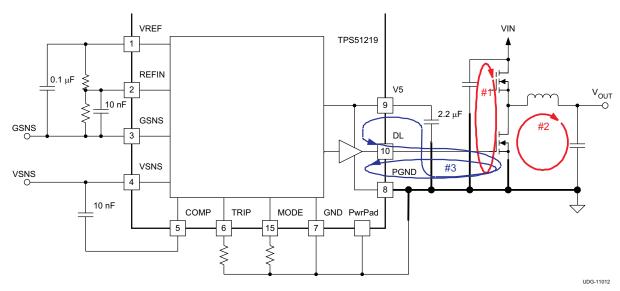

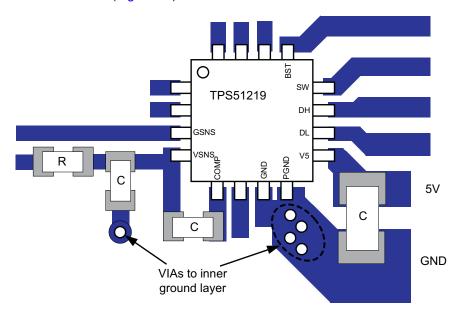

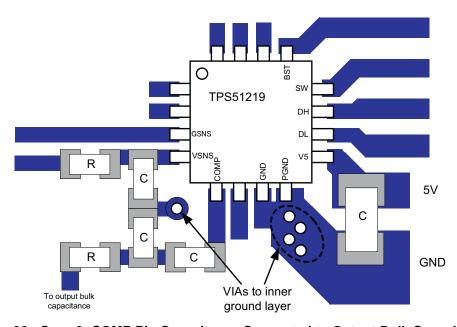

#### **Layout Considerations**

Certain issues must be considered before designing a layout using the TPS51219.

Figure 30. DC/DC Converter Ground System

- V<sub>IN</sub> capacitor(s), V<sub>OUT</sub> capacitor(s) and MOSFETs are the power components and should be placed on one side of the PCB (solder side). Other small signal components should be placed on another side (component side). At least one inner plane should be inserted, connected to ground, in order to shield and isolate the small signal traces from noisy power lines.

- All sensitive analog traces and components such as VSNS, COMP, MODE, REFIN, VREF and TRIP should be placed away from high-voltage switching nodes such as SW, DH, DL or BST to avoid coupling. Use internal layer(s) as ground plane(s) and shield feedback trace from power traces and components.

- The DC/DC converter has several high-current loops. The area of these loops should be minimized in order to suppress generating switching noise.

- Loop #1. The most important loop to minimize the area of is the path from the V<sub>IN</sub> capacitor(s) through the high and low-side MOSFETs, and back to the capacitor(s) through ground. Connect the negative node of the V<sub>IN</sub> capacitor(s) and the source of the low-side MOSFET at ground as close as possible. (Refer to loop #1 of Figure 30)

- Loop #2. The second important loop is the path from the low-side MOSFET through inductor and V<sub>OUT</sub> capacitor(s), and back to source of the low-side MOSFET through ground. Connect source of the low-side MOSFET and negative node of V<sub>OUT</sub> capacitor(s) at ground as close as possible. (Refer to loop #2 of Figure 30)

- Loop #3. The third important loop is of gate driving system for the low-side MOSFET. To turn on the low-side MOSFET, high current flows from V5 capacitor through gate driver and the low-side MOSFET, and back to negative node of the capacitor through ground. To turn off the low-side MOSFET, high current flows from gate of the low-side MOSFET through the gate driver and PGND, and back to source of the low-side MOSFET through ground. Connect negative node of V5 capacitor, source of the low-side MOSFET and PGND at ground as close as possible. (Refer to loop #3 of Figure 30)

- · Connect the PGND and GND pins directly at the device.

Connect VSNS directly to the output voltage sense point at the load device. Connect GSNS to ground return

points at the load device. Insert a 10-Ω, 1-nF, R-C filter between the sense point and the VSNS pin where the

COMP capacitance is connected as shown in Case 1 (Figure 31). When the COMP pin capacitance is

connected to output bulk capacitance, connect the R-C filter in series to both the VSNS pin and the COMP

capacitance as shown in Case 2 (Figure 32).

Figure 31. Case 1: COMP Pin Capacitance Connected to VSNS

Figure 32. Case 2: COMP Pin Capacitance Connected to Output Bulk Capacitance

- Connect the overcurrent setting resistors from TRIP pin to ground and make the connections as close as possible to the device. The trace from TRIP pin to resistor and from resistor to ground should avoid coupling to a high-voltage switching node.

- Connect the frequency and mode setting resistor from MODE pin to ground, and make the connections as

close as possible to the device. The trace from the MODE pin to the resistor and from the resistor to ground

should avoid coupling to a high-voltage switching node.

- Connections from gate drivers to the respective gate of the high-side or the low-side MOSFET should be as short as possible to reduce stray inductance. Use 0.65 mm (25 mils) or wider trace and via(s) of at least 0.5 mm (20 mils) diameter along this trace.

- The PCB trace defined as SW node, which connects to the source of the switching MOSFET, the drain of the rectifying MOSFET and the high-voltage side of the inductor, should be as short and wide as possible.

- In order to effectively remove heat from the package, prepare the thermal land and solder to the package thermal pad. Wide trace of the component-side copper, connected to this thermal land, helps to dissipate heat. Numerous vias with a 0.3-mm diameter connected from the thermal land to the internal/solder-side ground plane(s) should be used to help dissipation.

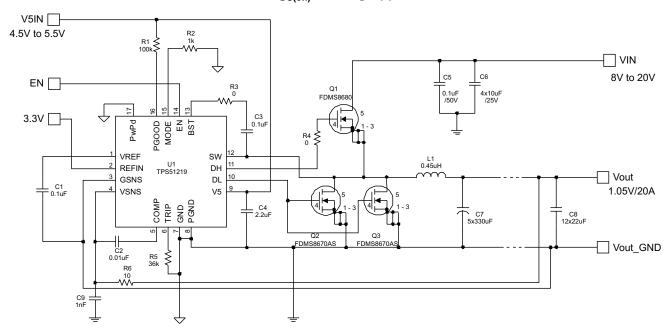

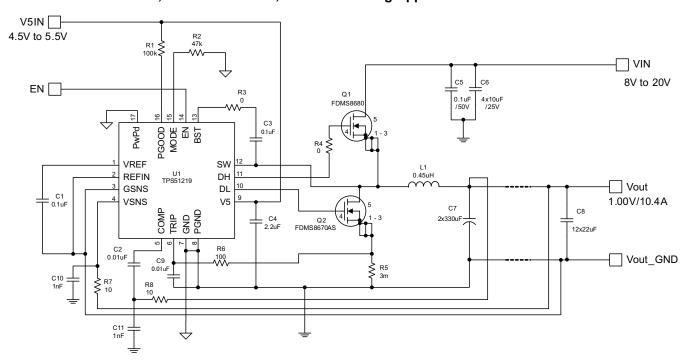

# TPS51219 1.05-V/20-A, D-CAP2™ 500-kHz, R<sub>DS(on)</sub> Sensing Application Circuit

Figure 33. 1.05-V/20-A, D-CAP2<sup>™</sup> 500-kHz, R<sub>DS(on)</sub> Sensing

Table 3. 1.05-V/20-A, D-CAP2<sup>™</sup> 500-kHz, R<sub>DS(on)</sub> Sensing, List of Materials

|                         | - V - / |                       |             |                   |  |

|-------------------------|---------|-----------------------|-------------|-------------------|--|

| REFERENCE<br>DESIGNATOR | QTY     | SPECIFICATION         | MANUFACTURE | PART NUMBER       |  |

| C6                      | 4       | 10 μF, 25 V           | Taiyo Yuden | TMK325BJ106MM     |  |

| C7                      | 5       | 330 μF, 2 V, 6 mΩ     | Panasonic   | EEFSX0D331XE      |  |

| C8                      | 12      | 22 μF, 6.3 V          | Murata      | GRM21BB30J226ME38 |  |

| L1                      | 1       | 0.45 μH, 17 A, 1.1 mΩ | Panasonic   | ETQP4LR45XFC      |  |

| Q1                      | 1       | 30 V, 35 A, 8.5 mΩ    | Fairchild   | FDMS8680          |  |

| Q2, Q3                  | 2       | 30 V, 42 A, 3.5 mΩ    | Fairchild   | FDMS8670AS        |  |

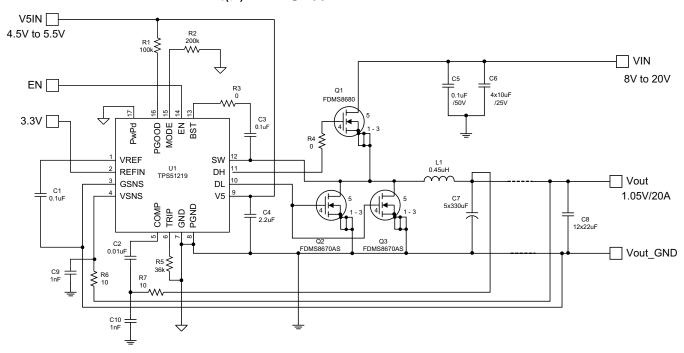

# 1.05-V/20-A, D-CAP<sup>™</sup> 400-kHz, $R_{DS(on)}$ Sensing Application Circuit

Figure 34. 1.05-V/20-A, D-CAP  $^{\text{TM}}$  400-kHz,  $R_{\text{DS(on)}}$  Sensing

Table 4. 1.05-V/20-A, D-CAP  $^{\text{TM}}$  400-kHz,  $R_{DS(on)}$  Sensing, List of Materials

| REFERENCE<br>DESIGNATOR | QTY | SPECIFICATION                     | MANUFACTURE | PART NUMBER       |

|-------------------------|-----|-----------------------------------|-------------|-------------------|

| C6                      | 4   | 10 μF, 25 V                       | Taiyo Yuden | TMK325BJ106MM     |

| C7                      | 5   | 330 $\mu F$ , 2.5 V, 18 $m\Omega$ | Sanyo       | 2R5TPE330MI       |

| C8                      | 12  | 22 μF, 6.3 V                      | Murata      | GRM21BB30J226ME38 |

| L1                      | 1   | 0.45 μH, 17 A, 1.1 mΩ             | Panasonic   | ETQP4LR45XFC      |

| Q1                      | 1   | 30 V, 35 A, 8.5 mΩ                | Fairchild   | FDMS8680          |

| Q2,Q3                   | 2   | 30 V, 42 A, 3.5 mΩ                | Fairchild   | FDMS8670AS        |

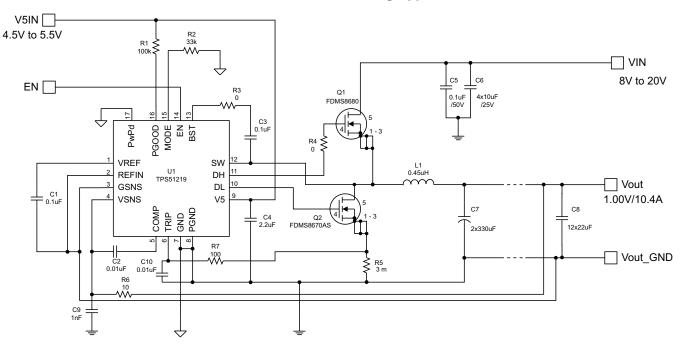

## TPS51219 1.00-V/10.4-A, D-CAP2™ 500-kHz, Resistor Sensing Application Circuit

Figure 35. 1.00-V/10.4-A, D-CAP2™ 500-kHz, Resistor Sensing

Table 5. 1.00-V/10.4-A, D-CAP2™ 500-kHz, Resistor Sensing, List of Materials

|                         |     |                                 | _           |                   |  |  |

|-------------------------|-----|---------------------------------|-------------|-------------------|--|--|

| REFERENCE<br>DESIGNATOR | QTY | SPECIFICATION                   | MANUFACTURE | PART NUMBER       |  |  |

| C6                      | 4   | 10 μF, 25 V                     | Taiyo Yuden | TMK325BJ106MM     |  |  |

| C7                      | 2   | 330 $\mu F$ , 2 V, 6 $m\Omega$  | Panasonic   | EEFSX0D331XE      |  |  |

| C8                      | 12  | 22 μF, 6.3 V                    | Murata      | GRM21BB30J226ME38 |  |  |

| L1                      | 1   | $0.45~\mu H,~17~A,~1.1~m\Omega$ | Panasonic   | ETQP4LR45XFC      |  |  |

| Q1                      | 1   | 30 V, 35 A, 8.5 mΩ              | Fairchild   | FDMS8680          |  |  |

| Q2                      | 1   | 30 V, 42 A, 3.5 mΩ              | Fairchild   | FDMS8670AS        |  |  |

| R5                      | 1   | 3 mΩ, 1 W                       | KOA         | TLR2HDTD3L00F     |  |  |

## TPS51219 1.00-V/10.4-A, D-CAP™ 400-kHz, Resistor Sensing Application Circuit

Figure 36. 1.00-V/10.4-A, D-CAP™ 400-kHz, Resistor Sensing

Table 6. 1.00-V/10.4-A, D-CAP™ 400-kHz, Resistor Sensing, List of Materials

| REFERENCE<br>DESIGNATOR | QTY | SPECIFICATION         | MANUFACTURE | PART NUMBER       |

|-------------------------|-----|-----------------------|-------------|-------------------|

| C6                      | 4   | 10 μF, 25 V           | Taiyo Yuden | TMK325BJ106MM     |

| C7                      | 2   | 330 μF, 2 V, 9 mΩ     | Panasonic   | EEFSX0D331ER      |

| C8                      | 12  | 22 μF, 6.3 V          | Murata      | GRM21BB30J226ME38 |

| L1                      | 1   | 0.45 μH, 17 A, 1.1 mΩ | Panasonic   | ETQP4LR45XFC      |

| Q1                      | 1   | 30 V, 35 A, 8.5 mΩ    | Fairchild   | FDMS8680          |

| Q2                      | 1   | 30 V, 42 A, 3.5 mΩ    | Fairchild   | FDMS8670AS        |

| R5                      | 1   | 3 mΩ, 1 W             | KOA         | TLR2HDTD3L00F     |

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| FX003            | ACTIVE | WQFN         | RTE                | 16   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 51219                | Samples |

| TPS51219RTER     | ACTIVE | WQFN         | RTE                | 16   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 51219                | Samples |

| TPS51219RTET     | ACTIVE | WQFN         | RTE                | 16   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 51219                | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 16-Oct-2020

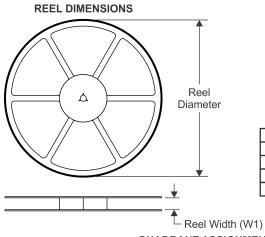

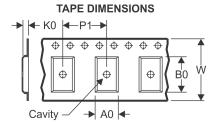

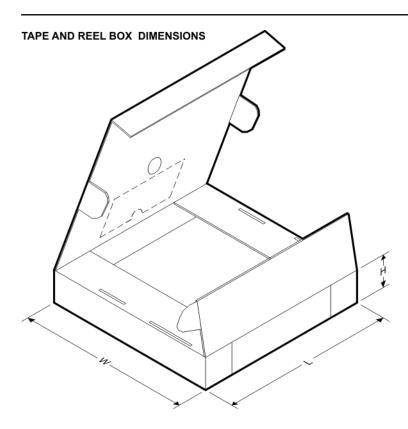

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

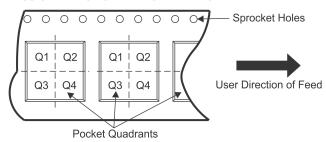

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All differsions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS51219RTER                | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51219RTER                | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51219RTET                | WQFN            | RTE                | 16 | 250  | 180.0                    | 12.5                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 16-Oct-2020

\*All dimensions are nominal

| 7 III GITTIOTOTOTO GITO TIOTITIGI |              |                 |      |      |             |            |             |

|-----------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS51219RTER                      | WQFN         | RTE             | 16   | 3000 | 338.0       | 355.0      | 50.0        |

| TPS51219RTER                      | WQFN         | RTE             | 16   | 3000 | 853.0       | 449.0      | 35.0        |

| TPS51219RTET                      | WQFN         | RTE             | 16   | 250  | 338.0       | 355.0      | 50.0        |

3 x 3, 0.5 mm pitch

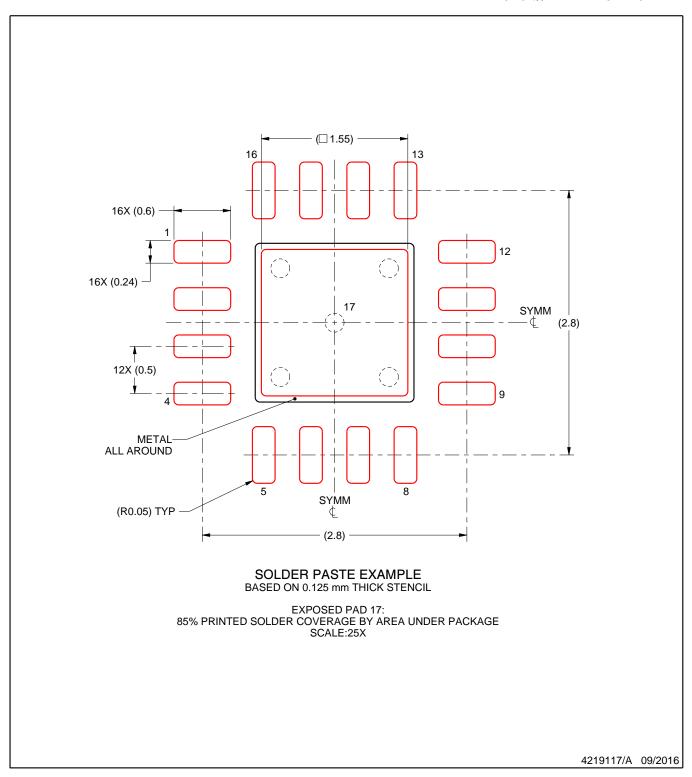

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC QUAD FLATPACK - NO LEAD

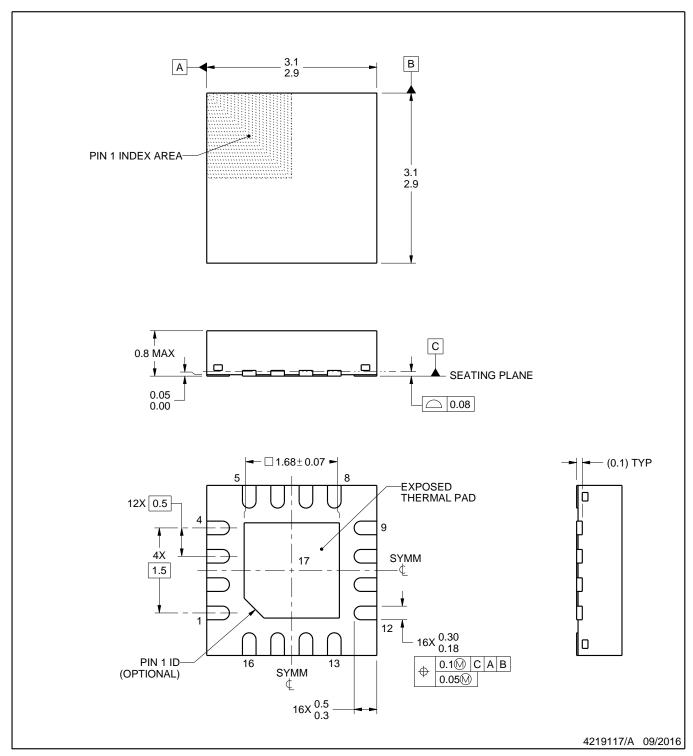

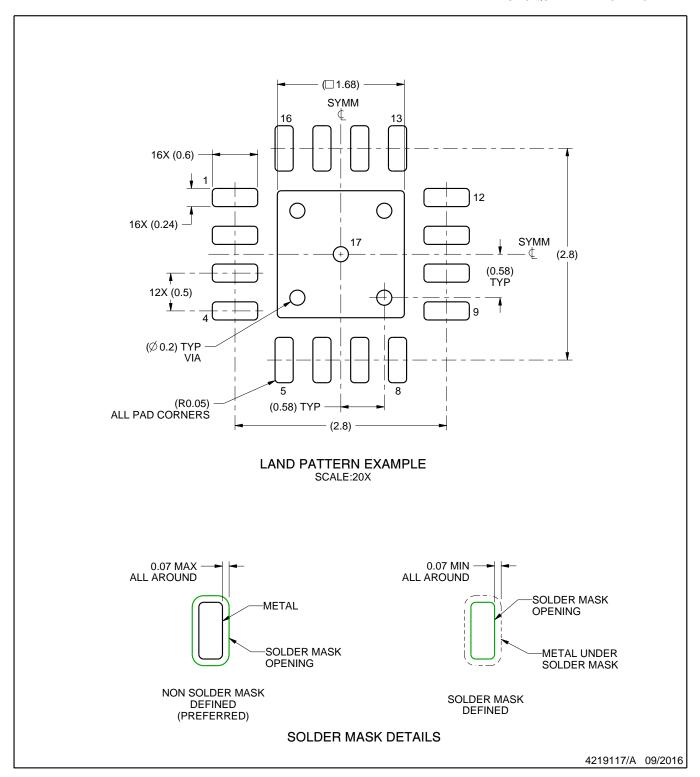

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.