## AR8032 Integrated 10/100 Fast Ethernet Transceiver

## **General Description**

The Atheros AR8032 Fast Ethernet transceiver is a highly integrated physical layer device that transmits and receives high-speed data over standard category 5 (CAT 5) unshielded twisted pair cable.

The AR8032 is compliant with 100 BASE-TX and 10 BASE-T IEEE 802.3 standards. The AR8032 device uses advanced mixed-signal processing technology and integrates functions such as adaptive equalization, and timing recovery to deliver substantial power savings and operation in noisy environments.

The AR8032 device supports the Media Independent Interface (MII) and Reduced Media Independent Interface (RMII) for direct connection to a Fast Ethernet-capable MAC.

The AR8032 supports the Atheros Cable Diagnostic Test (CDT) feature, which uses Time Domain Reflectometry (TDR) technology to quickly and remotely identify potential cable malfunctions without deploying field support personnel or bringing down the network. The AR8032 solution detects and reports issues such as PHY malfunctions, bad/marginal cable or patch cord segments or connectors, thus significantly reducing installation time, cable debug efforts, and overall network support cost. Manufactured in a standard CMOS process, the AR8032 is packaged in a 32-pin QFN, featuring a small body size of 5 x 5mm.

#### Features

- 10/100 BASE-T IEEE 802.3 compliant

- Supports MII/RMII interface

- Low power modes with internal automatic DSP power saving scheme

- Fully integrated digital adaptive equalizers All digital baseline wander correction

- Supports external 25 MHz clock source in MII mode

- Supports external 50 MHz clock source in RMII mode

- Automatic speed downshift mode

- Automatic MDI/MDIX crossover

- Automatic polarity correction

- Loopback modes for diagnostics

- IEEE 802.3u compliant Auto-Negotiation

- Software programmable LED modes

- Cable Diagnostic Test (CDT)

- Requires only one 3.3V power supply

- 32-pin QFN 5mm x 5 mm package

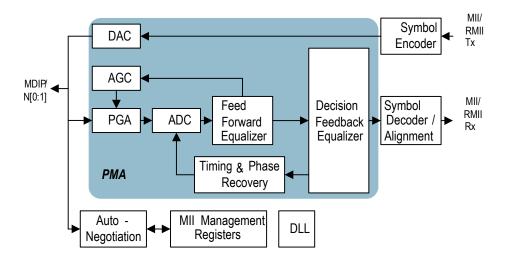

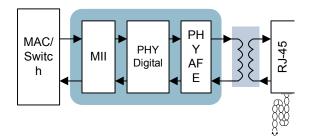

#### AR8032 Functional Block Diagram

<sup>© 2010</sup> by Atheros Communications, Inc. All rights reserved. Atheros<sup>®</sup>, Atheros Driven<sup>®</sup>, Atheros XR<sup>®</sup>, Driving the Wireless Future<sup>®</sup>, ROCm<sup>®</sup>, Super A/G<sup>®</sup>, Super A<sup>®</sup>, Super N<sup>®</sup>, Total 802.11<sup>®</sup>, XSPAN<sup>®</sup>, Wireless Future. Unleashed Now<sup>®</sup>, and Wake on Wireless<sup>®</sup> are registered by Atheros Communications, Inc. Atheros SST<sup>™</sup>, Signal-Sustain Technology<sup>™</sup>, the Air is Cleaner at 5-GHz<sup>™</sup>, and 5-UP<sup>™</sup> are trademarks of Atheros Communications, Inc. The Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders. Subject to change without notice.

# 2 • AR8032 Integrated 10/100 Mbps Ethernet Transceiver July 2010

## **Table of Contents**

| Ge | General Description1 |                                        |  |  |  |

|----|----------------------|----------------------------------------|--|--|--|

| Fe | Features1            |                                        |  |  |  |

| Aŀ | R803                 | 2 Functional Block Diagram1            |  |  |  |

| 1  | Pin                  | Descriptions5                          |  |  |  |

| 2  | Fur                  | nctional Description9                  |  |  |  |

|    | 2.1                  | Transmit Functions9                    |  |  |  |

|    | 2.2                  | Receive Functions9                     |  |  |  |

|    |                      | 2.2.1 Decoder Modes                    |  |  |  |

|    |                      | 2.2.2 Analog to Digital Converter . 10 |  |  |  |

|    |                      | 2.2.3 Baseline Wander Canceller 10     |  |  |  |

|    |                      | 2.2.4 Digital Adaptive Equalizer 10    |  |  |  |

|    |                      | 2.2.5 Auto-Negotiation10               |  |  |  |

|    |                      | 2.2.6 Smartspeed Function10            |  |  |  |

|    |                      | 2.2.7 Polarity Correction              |  |  |  |

|    | 2.3                  | Loopback Modes 11                      |  |  |  |

|    |                      | 2.3.1 Digital Loopback11               |  |  |  |

|    |                      | 2.3.2 External Cable Loopback 11       |  |  |  |

|    |                      | 2.3.3 Cable Diagnostic Test11          |  |  |  |

|    |                      | 2.3.4 LED Interface11                  |  |  |  |

|    |                      | 2.3.5 Power Supplies11                 |  |  |  |

|    |                      | 2.3.6 Low Power Modes11                |  |  |  |

| _  |                      | 2.3.7 Hibernation Mode 11              |  |  |  |

| 3  |                      | ctrical Characteristics                |  |  |  |

|    |                      | Absolute Maximum Ratings13             |  |  |  |

|    | 3.2                  | Recommended Operating Conditions 13    |  |  |  |

|    | 3.3                  | XTAL/OSC Timing14                      |  |  |  |

|    | 3.4                  | MII DC Characteristics15               |  |  |  |

|    | 3.5                  | MDIO Characteristics16                 |  |  |  |

|    |                      | 3.5.8 MDIO Timing16                    |  |  |  |

|    | 3.6                  | Power-On Strapping18                   |  |  |  |

|    | 3.7                  | Typical Power Consumption Parame-      |  |  |  |

|    |                      | ters                                   |  |  |  |

|    | 3.8                  | Power-on Sequence, Reset and Clock 20  |  |  |  |

|    |                      | 3.8.1 Power-on Sequence                |  |  |  |

|    |                      | 3.8.2 Reset and Clock Timing20         |  |  |  |

| 4  | Reg                  | gister Descriptions21                  |  |  |  |

|    | 4.1                  | PHY Register Summary21                 |  |  |  |

|    |                      | 4.1.1 Control Register                 |  |  |  |

|    |                      | 4.1.2 Status Register24                |  |  |  |

|    |                      | 4.1.3 PHY Identifier                   |  |  |  |

|    |                      | 4.1.4 PHY Identifier 226               |  |  |  |

|   | 4.1.5     | Auto-Negotiation Advertise-        |

|---|-----------|------------------------------------|

|   |           | ment Register 27                   |

|   | 4.1.6     | Auto-Negotiation Expansion         |

|   |           | Register 29                        |

|   | 4.1.7     | Link partner ability register(base |

|   |           | page)                              |

|   | 4.1.8     | Function Control Register 31       |

|   | 4.1.9     | PHY Specific Status Register 33    |

|   | 4.1.10    | Interrupt Enable Register 34       |

|   | 4.1.11    | Interrupt Status Register 36       |

|   | 4.1.12    | Smart Speed Register               |

|   |           | Receive Error Count Register 40    |

|   |           | Virtual Cable Tester Control       |

|   |           | Register 40                        |

|   | 4.1.15    | LED Control Register               |

|   | 4.1.16    | Virtual Cable Tester Status Reg-   |

|   |           | ister                              |

|   | 4.1.17    | Debug Port (Address Offset Set)    |

|   |           | Register 43                        |

|   | 4.1.18    | Debug Port 2 (R/W Port) Regis-     |

|   |           | ter                                |

|   | 4.2 Powe  | r Saving and Debug Register        |

|   |           | nary                               |

|   | 4.2.19    | 10Base-T Test Configuration        |

|   |           | Register                           |

|   | 4.2.20    | 100Base-TX Test Configuration      |

|   |           | Register 45                        |

|   |           | Hibernate Control Register 47      |

|   |           | Power Saving Control               |

| 5 | Package I | Dimensions                         |

| 6 | Ordering  | Information51                      |

# 4 • AR8032 Integrated 10/100 Mbps Ethernet Transceiver July 2010

## 1. Pin Descriptions

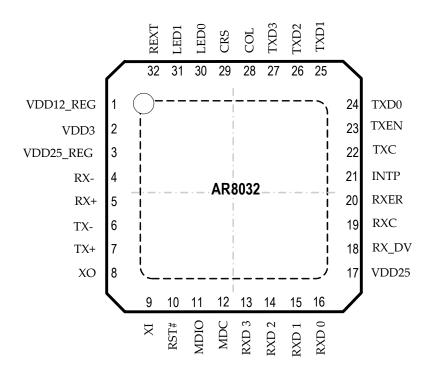

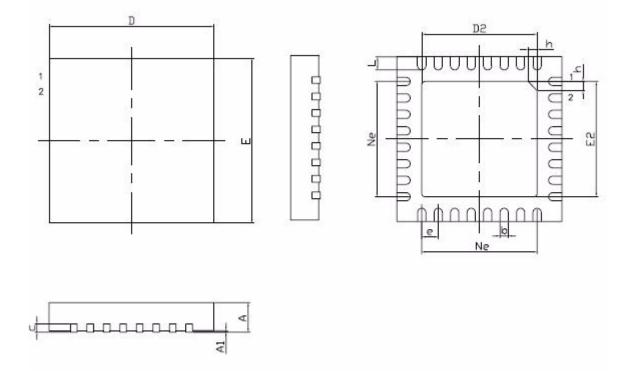

This section contains a package pinout for the AR8032 QFN 32pin and a listing of the signal descriptions (see Figure 1-1).

The following nomenclature is used for signal names:

| NC | No connection to the internal die is made from this pin     |

|----|-------------------------------------------------------------|

| _# | At the end of the signal name, indicates active low signals |

| Р  | Power                                                       |

The following nomenclature is used for signal types described in Table 1-1:

- D Open drain

- IA Analog input

- I Digital input

- IH Digital input with histeresis

- I/O Digital input/output

- OA Analog output

- O Digital output

- PD Internal pull-down for digital input

- PU Internal pull-up for digital input

Figure 1-1 shows the pinout diagram for the AR8032.

Figure 1-1. Pinout Diagram

NOTE: There is an exposed ground pad on the back side of the package.

| Symbol    | Pin | Туре            | Description                                                                                                                                                                                                                                                          |  |  |

|-----------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDD12_REG | 1   | AO              | 1.2V regulator output. A 1 uF plus a 0.1 uF cap needed to stabilize the output                                                                                                                                                                                       |  |  |

| VDD3      | 2   | Р               | 3.3V power supply.                                                                                                                                                                                                                                                   |  |  |

| VDD25_REG | 3   | AO              | 2.5V regulator output. A 1 uF ceramic cap needed to stabalize the output. It is for analog, digital I/O and the transformer center taps.                                                                                                                             |  |  |

| RX-       | 4   | AI, AO          | Media Dependent Interface 0, terminate with a 49.9 $\Omega$ resister and onnect to XFMR                                                                                                                                                                              |  |  |

| RX+       | 5   | AI, AO          | Media Dependent Interface 0, terminate with a $49.9\Omega$ resister and connect to XFMR                                                                                                                                                                              |  |  |

| TX-       | 6   | AI, AO          | Media Dependent Interface 1, terminate with a $49.9\Omega$ resister and connect to XFMR                                                                                                                                                                              |  |  |

| TX+       | 7   | AI, AO          | Media Dependent Interface 1, terminate with a $49.9\Omega$ resister and connect to XFMR                                                                                                                                                                              |  |  |

| ХО        | 8   | AO              | Crystal oscillator output. 27 pF to GND.                                                                                                                                                                                                                             |  |  |

| XI        | 9   | AI              | Crystal oscillator input. 27 pF to GND. An external 25/50 MHx clock source with 1.2V swing can inject from this pin when a crystal is not used and the two 27pF caps removed. The 25 Mhz clock input is for MII mode, while the 50 Mhz clock input is for RMII mode. |  |  |

| RST#      | 10  | IH, PU          | System reset input.                                                                                                                                                                                                                                                  |  |  |

| MDIO      | 11  | I/O, D, PU      | Management data.                                                                                                                                                                                                                                                     |  |  |

| MDC       | 12  | I, PU           | /anagement clock reference.                                                                                                                                                                                                                                          |  |  |

| RXD3      | 13  | I/O, PU,<br>POS | MII Receive data output [3].                                                                                                                                                                                                                                         |  |  |

| RXD2      | 14  | I/O, PD,<br>POS | MII Receive data output [2].                                                                                                                                                                                                                                         |  |  |

| RXD1      | 15  | I/O, PD,<br>POS | MII/RMII Receive data output [1].                                                                                                                                                                                                                                    |  |  |

| RXD0      | 16  | I/O, PU,<br>POS | MII/RMII Receive data output [0].                                                                                                                                                                                                                                    |  |  |

| VDD25     | 17  | Р               | 2.5V I/O power, connect with pin 3, 0.1uF to GND.                                                                                                                                                                                                                    |  |  |

| RX_DV     | 18  | I/O, PD,<br>POS | Receive data valid output                                                                                                                                                                                                                                            |  |  |

| RXC       | 19  | I/O, PD,<br>POS | Receive clock output                                                                                                                                                                                                                                                 |  |  |

| RXER      | 20  | I/O, PD,<br>POS | Receive error output                                                                                                                                                                                                                                                 |  |  |

| INTP      | 21  | I/O, PU,<br>POS | Interrupt Output                                                                                                                                                                                                                                                     |  |  |

| TXC       | 22  | I/O, PU,<br>POS | Transmit clock output                                                                                                                                                                                                                                                |  |  |

| TXEN      | 23  | I, PU           | Transmit data enable                                                                                                                                                                                                                                                 |  |  |

Table 1-1. Signal to Pin Relationships and Descriptions

| Symbol | Pin | Туре            | Description                                               |

|--------|-----|-----------------|-----------------------------------------------------------|

| TXD0   | 24  | I, PD           | MII/RMII Transmit data input [0]                          |

| TXD1   | 25  | I, PD           | MII/RMII Transmit data input [1]                          |

| TXD2   | 26  | I, PD           | MII Transmit data input [2]                               |

| TXD3   | 27  | I, PD           | MII Transmit data input [3]                               |

| COL    | 28  | I/O, PD,<br>POS | Collision Detect output                                   |

| CRS    | 29  | I/O, PD<br>POS  | Carrier Sense output                                      |

| LED0   | 30  | I/O, PU<br>POS  | Programable LED0, the default indicates Link and Activity |

| LED1   | 31  | I/O, PU<br>POS  | Programmable LED1, The default indicates Speed            |

| REXT   | 32  | AO              | Connect 2.37 K to GND                                     |

| PADDLE | GND | Gnd             | Ground                                                    |

Table 1-1. Signal to Pin Relationships and Descriptions (continued)

**NOTE:** All of the digital input only pads are 3.3V input tolerant. The 0 and I/0 pads are powered with 2.5V power. The input level of any I/0 pads (except open-drain type) is limited to 3 V.

## 2. Functional Description

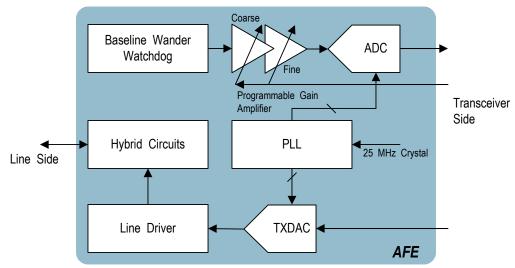

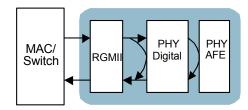

The Atheros AR8032 is a highly integrated analog front end (AFE) and digital signal transceiver (see Figure 2-1), providing high performance with substantial cost reduction. AFE consists of automatic gain control (AGC), ADC, DAC, drivers, and clock generation. The AR8032 provides physical layer functions to transmit and receive high-speed data over standard category 5 (CAT5) unshielded twisted pair cable.

See also the "AR8032 Functional Block Diagram" on page 1.

Figure 2-1. Analog Front End

The AR8032 10/100 PHY is fully 802.3, 802.3u compliant, and supports the mediaindependent interface (MII) and Reduced Media Independent Interface (RMII) to connect to a Fast Ethernet-capable MAC.

The AR8032 transceiver combines feedforward equalizer, feedback equalizer, and timing recovery, to enhance signal performance in noisy environments.

#### 2.1 Transmit Functions

The AR8032 transmit channel includes 4B/5B mapper and scrambler. Table 2-1 describes the transmit function encoder modes.

| Table 2-1. Transmit Function Encoder Modes | Table 2-1. | Transmit | Function | Encoder | Modes |

|--------------------------------------------|------------|----------|----------|---------|-------|

|--------------------------------------------|------------|----------|----------|---------|-------|

| Encoder Mode | Description                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100BASE-TX   | In 100BASE-TX mode, 4-bit data<br>from the MII is 4B/5B serialized,<br>scrambled, and encoded to a<br>three-level MLT3 sequence<br>transmitted by the PMA. |

| 10BASE-T     | In 10BASE-T mode, the AR8032<br>transmits and receives<br>Manchester-encoded data.                                                                         |

#### 2.2 Receive Functions

The AR8032 receive channel includes digital gain control, feed forward adaptive equalizer, decision feedback equalizer, slicer, 5B/4B demapper and de-scrambler, PCS receive functional block, and timing recovery logic.

#### 2.2.1 Decoder Modes

Table 2-2 describes the receive function decoder modes.

#### Table 2-2. Receive Function Decoder Modes

| Decoder Mode | Description                                                                                                                                                                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100BASE-TX   | In 100BASE-TX mode, the receive<br>data stream is recovered and<br>descrambled to align to the<br>symbol boundaries. The aligned<br>data is then parallelized and 5B/<br>4B decoded to 4-bit data. This<br>output runs to the MII/RMII<br>receive data pins after data stream<br>delimiters have been translated. |

| 10BASE-T     | In 10BASE-T mode, the recovered<br>10BASE-T signal is decoded from<br>Manchester then aligned.                                                                                                                                                                                                                    |

#### 2.2.2 Analog to Digital Converter

The AR8032 device employs an advanced high speed ADC on each receive channel with high resolution, which results in better SNR and lower error rates.

#### 2.2.3 Baseline Wander Canceller

Baseline wander results from Ethernet links that AC-couple to the transceivers and from AC coupling that cannot maintain voltage levels for longer than a short time. As a result, transmitted pulses are distorted, resulting in erroneous sampled values for affected pulses. The AR8032 device uses an advanced baseline wander cancellation circuit that continuously monitors and compensates for this effect, minimizing the impact of DC baseline shift on the overall error rate.

#### 2.2.4 Digital Adaptive Equalizer

The digital adaptive equalizer removes intersymbol interference at the receiver. The digital adaptive equalizer takes unequalized signals from ADC output and uses a combination of feedforward equalizer (FFE) and decision feedback equalizer (DFE) for the bestoptimized signal-to-noise (SNR) ratio.

#### 2.2.5 Auto-Negotiation

The AR8032 device supports 10/100 BASE-T Copper auto-negotiation in accordance with IEEE 802.3 clauses 28 and 40. Auto-negotiation provides a mechanism for transferring information between a pair of link partners to choose the best possible mode of operation in terms of speed, duplex modes, and master/ slave preference. Auto-negotiation is initiated upon any of the following scenarios:

- Power-up reset

- Hardware reset

- Software reset

- Auto-negotiation restart

- Transition from power-down to power-up

- The link goes down

If auto-negotiation is disabled, a 10BASE-T or 100BASE-TX can be manually selected using the IEEE MII registers.

#### 2.2.6 Smartspeed Function

The Atheros Smartspeed function is an enhanced feature of auto-negotiation that allows the AR8032 device to fall back in speed based on cabling conditions as well as operate over CAT3 cabling (in 10BASE-T mode) or twopair CAT5 cabling (in 100BASE-TX mode).

By default, the Smartspeed feature is enabled. Refer to the register "Smart Speed Register" on page 38, which describes how to set the parameters. Set these register bits to control the Smartspeed feature:

- Bit [5]: 1 = Enables Smartspeed (default)

- Bits [4:2]: Sets the number of link attempts before adjusting

- Bit [1]: Timer to determine the stable link condition

#### 2.2.7 Polarity Correction

If cabling has been incorrectly wired, the AR8032 automatically corrects polarity errors on the receive pairs.

#### 2.3 Loopback Modes

#### 2.3.1 Digital Loopback

Digital loopback provides the ability to loop transmitted data back to the receiver using digital circuitry in the AR8032 device.

Figure 2-2 shows a block diagram of digital loopback.

Figure 2-2. Digital Loopback

#### 2.3.2 External Cable Loopback

External cable loopback loops MII Tx to MII Rx through a complete digital and analog path and an external cable, thus testing all the digital data paths and all the analog circuits. Figure 2-3 shows a block diagram of external cable loopback.

Figure 2-3. External Cable Loopback

#### 2.3.3 Cable Diagnostic Test

The Cable Diagnostic Test (CDT) feature in the AR8032 device uses Time Domain Reflectometry (TDR) to identify remote and local PHY malfunctions, bad/marginal cable or patch cord segments, or connectors. Some of the possible problems that can be diagnosed include opens, shorts, cable impedance mismatch, bad connectors, termination mismatch, and bad magnetics. The CDT can be performed when there is no link partner or when the link partner is auto-negotiating.

#### 2.3.4 LED Interface

The LED interface can either be controlled by the PHY or controlled manually, independent of the state of the PHY. Two status LEDs are available. These can be used to indicate operation speed, and link status. The LEDs can be programmed to different status functions from their default value. They can also be controlled directly from the MII register interface.

#### 2.3.5 Power Supplies

The AR8032 device requires only one power supply: 3.3V.

#### 2.3.6 Low Power Modes

The AR8032 device supports the software power-down low power mode. The standard IEEE power-down mode is entered by setting the POWER\_DOWN bit (bit [11]) of the register "Control Register" on page 22 equal to one.

In this mode, the AR8032 device ignores all MAC interface signals except the MDC/MDIO. It does not respond to any activity on the CAT 5 cable. The device cannot wake up on its own. It can only wake up by setting the POWER\_DOWN bit (bit [11]) of the register "Control Register" on page 22" to 0.

#### 2.3.7 Hibernation Mode

The AR8032 device supports hibernation mode. When the cable is unplugged, the AR8032 will enter hibernation mode after about 10 seconds. The power consumption in this mode is very low compared to the normal mode of operation. When the cable is reconnected, the AR8032 wakes up and normal functioning is restored.

## 3. Electrical Characteristics

#### 3.1 Absolute Maximum Ratings

Table 3-1 summarizes the absolute maximum ratings and Table 3-2 lists the recommended operating conditions for the AR8032. Absolute maximum ratings are those values beyond which damage to the device can occur. Functional operation under these conditions, or at any other condition beyond those indicated in the operational sections of this document, is not recommended.

| Symbol             | Symbol Parameter     |            | Unit |

|--------------------|----------------------|------------|------|

| VDD33              | 3.3V supply voltage  | 3.8        | V    |

| T <sub>store</sub> | Storage temperature  | -65 to 150 | °C   |

| HBM                | Human Body Model     | ±4500      | V    |

| CDM                | Charged-Device Model | ±1000      | V    |

| MM                 | Machine Model        | ±200       | V    |

#### Table 3-1. Absolute Maximum Ratings

#### 3.2 Recommended Operating Conditions

Table 3-2. Recommended Operating Conditions

| Symbol         | Parameter                                                                                                                    | Min | Тур | Max | Unit |

|----------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VDD33          | 3.3V supply voltage                                                                                                          | 3.0 | 3.3 | 3.6 | V    |

| T <sub>A</sub> | Ambient Temperature for normal operation —<br>Commercial chip version, AR8032-BL1A (see<br>"Ordering Information — page 53") | 0   | _   | 70  | °C   |

|                | Ambient Temperature for normal operation —<br>Industrial chip version, AR8032-BL1B (see<br>"Ordering Information — page 53") | -40 | _   | 85  | °C   |

| T <sub>J</sub> | Junction Temperature                                                                                                         | -40 | —   | 125 | °C   |

| $\Psi_{JT}$    | Thermal Dissipation Coefficient                                                                                              |     | 4   | —   | °C/W |

**NOTE:** The following condition must be satisfied:

$T_{Jmax} > T_{Cmax} + \Psi_{JT} \times P_{Typical}$

Where:

$T_{Jmax}$  = Maximum allowable temperature of the Junction

T<sub>Cmax</sub> = Maximum allowable Case temperature

$\Psi_{\text{IT}}$  = Thermal Dissipation Coefficient

P<sub>Typical</sub> = Typical power dissipation

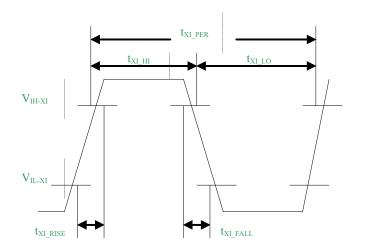

#### 3.3 XTAL/OSC Timing

Figure 3-1 shows the XTAL timing diagram.

Figure 3-1. XTAL/OSC Timing Diagram

| Symbol    | Parameter                                                                  | Min             | Тур  | Max             | Unit |

|-----------|----------------------------------------------------------------------------|-----------------|------|-----------------|------|

| T_XI_PER  | XI/OSCI Clock Period                                                       | 40.0 -<br>50ppm | 40.0 | 40.0 +<br>50ppm | ns   |

| T_XI_HI   | XI/OSCI Clock High                                                         | 14              | 20.0 |                 | ns   |

| T_XI_LO   | XI/OSCI Clock Low                                                          | 14              | 20.0 |                 | ns   |

| T_XI_RISE | XI/OSCI Clock Rise Time, V <sub>IL</sub> (max)<br>to V <sub>IH</sub> (min) |                 |      | 4               | ns   |

| T_XI_FALL | XI/OSCI Clock Fall time, V <sub>IL</sub> (max)<br>to V <sub>IH</sub> (min) |                 |      | 4               | ns   |

| V_IH_XI   | The XTLI input high level                                                  | 0.8             | 1.2  | 1.5             | V    |

| V_IL_XI   | The xtli input low lever voltage                                           | -0.3            | 0    | 0.15            | V    |

#### Table 3-4. XTAL/OSC Timing — RMII mode

| Symbol   | Parameter            | Min             | Тур  | Max             | Unit |

|----------|----------------------|-----------------|------|-----------------|------|

| T_XI_PER | XI/OSCI Clock Period | 20.0 -<br>50ppm | 20.0 | 20.0 +<br>50ppm | ns   |

| T_XI_HI  | XI/OSCI Clock High   | 8               | 10.0 |                 | ns   |

| T_XI_LO  | XI/OSCI Clock Low    |                 | 10.0 |                 | ns   |

| T_XI_RISE | XI/OSCI Clock Rise Time, V <sub>IL</sub> (max)<br>to V <sub>IH</sub> (min) |      |     | 2    | ns |

|-----------|----------------------------------------------------------------------------|------|-----|------|----|

| T_XI_FALL | XI/OSCI Clock Fall time, V <sub>IL</sub> (max)<br>to V <sub>IH</sub> (min) |      |     | 2    | ns |

| V_IH_XI   | The XTLI input high level                                                  | 0.8  | 1.2 | 1.5  | V  |

| V_IL_XI   | The xtli input low level voltage                                           | -0.3 | 0   | 0.15 | V  |

## 3.4 MII DC Characteristics

Table 3-5 shows the MII DC characteristics.

#### Table 3-5. MII DC Characteristics

| Symbol          | Parameter           | Min | Max | Unit |

|-----------------|---------------------|-----|-----|------|

| V <sub>OH</sub> | Output high voltage | 2.4 | 3.0 | V    |

| V <sub>OL</sub> | Output low voltage  | GND | 0.4 | V    |

| V <sub>IH</sub> | Input high voltage  | 1.7 |     | V    |

| V <sub>IL</sub> | Input low voltage   | _   | 0.7 | V    |

| $I_{IH}$        | Input high current  | _   | 15  | μΑ   |

| $I_{IL}$        | Input low current   | -15 | —   | μΑ   |

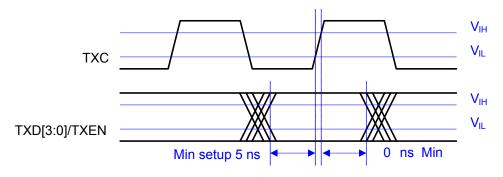

Figure 3-2 shows the MII input AC timing diagram.

Figure 3-2. MII Input AC Timing Diagram

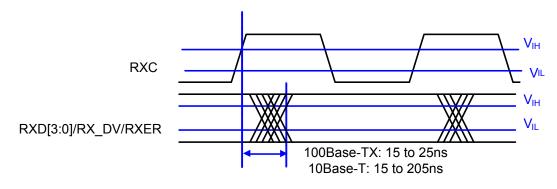

Figure 3-3 shows the MII output AC timing diagram.

Figure 3-3. MII Output AC Timing Diagram

#### 3.5 MDIO Characteristics

Table 3-6 shows the MDIO DC characteristics.RMII TimingTable 3-6.MDIO DC Characteristics

| Symbol          | Parameter                           | Min  | Max | Unit |

|-----------------|-------------------------------------|------|-----|------|

| V <sub>OH</sub> | V <sub>OH</sub> Output high voltage |      |     | V    |

| V <sub>OL</sub> | Output low voltage                  | _    | 0.4 | V    |

| V <sub>IH</sub> | Input high voltage                  | 2    |     | V    |

| V <sub>IL</sub> | Input low voltage                   |      | 0.8 | V    |

| I <sub>IH</sub> | Input high current                  | _    | 0.4 | mA   |

| I <sub>IL</sub> | Input low current                   | -0.4 |     | mA   |

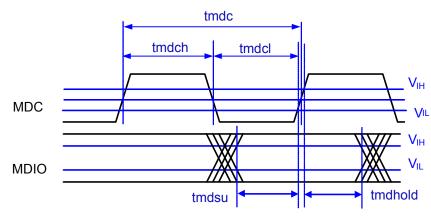

#### 3.5.8 MDIO Timing

Figure 3-4 shows the MDIO timing diagram.

Figure 3-4. MDIO Timing Diagram

Table 3-7 shows the RMII AC timing characteristics.

| Symbol  | Parameter                     | Min | Тур | Max | Unit |

|---------|-------------------------------|-----|-----|-----|------|

| tmdc    | MDC Period                    | 100 |     |     | nS   |

| tmdcl   | MDC Low Period                | 40  |     |     | nS   |

| tmdch   | MDC High Period               | 40  |     |     | nS   |

| tmdsu   | MDIO to MDC rising setup time | 10  |     |     | nS   |

| tmdhold | MDIO to MDC rising hold time  | 10  |     |     | nS   |

#### Table 3-7. MDIO Timing

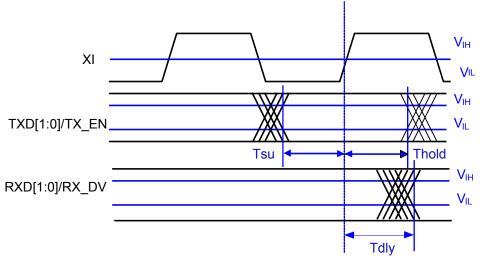

Table 3-8 shows the RMII AC timingcharacteristics.

#### Table 3-8. RMII AC Timing

| Symbol | Parameter                         | Min       | Max       | Unit |

|--------|-----------------------------------|-----------|-----------|------|

| Tck    | XI Period                         | 20 -50ppm | 20 +50ppm | nS   |

|        |                                   |           |           |      |

| Tsu    | TXEN, TXD to XI rising setup time | 4         | —         | nS   |

| Thold  | TXEN, TXD to XI rising hold time  | 2         | —         | nS   |

| Tdly   | XI to RX_DV, RXD output delay     | 3         | 14        | nS   |

Figure 3-5 shows the AC RMII timing diagram.

Figure 3-5. RMII AC Timing Diagram

#### 3.6 Power-On Strapping

Table 3-9 shows the pin-to-PHY core configuration signal power-on strapping.

| PHY Pin Name | Pin | PHY Core<br>Configuration Signal | Description                                                        | Default |

|--------------|-----|----------------------------------|--------------------------------------------------------------------|---------|

| RXD3         | 13  | PHYADDRESS[0]                    | RXD[1:3] set the lower three bits of the physical                  |         |

| RXD2         | 14  | PHYADDRESS[1]                    | address. The upper two bits of the physical addr<br>default to 001 | ess 0   |

| RXD1         | 15  | PHYADDRESS[2]                    |                                                                    | 0       |

| RXD0         | 16  | DUPLEX                           | 0 Half Duplex                                                      | 1       |

|              |     |                                  | 1 Full Duplex                                                      |         |

| RXDV         | 18  | CONFIG2                          | CONFIG[2:0]                                                        | 000     |

| CRS          | 29  | CONFIG1                          | 000 = MII                                                          |         |

| COL          | 28  | CONFIG0                          | 001 = RMII<br>All other binary combinations are Reserved.          |         |

| RXER         | 20  | ISOLATE                          | 0 Disable                                                          | 0       |

|              |     |                                  | 1 Enable                                                           |         |

| INTP         | 21  | TEST MODE                        | 0 Test Mode                                                        | 1       |

|              |     |                                  | 1 Normal Operation                                                 |         |

| LED0         | 30  | AUTO-                            | 0 Disable                                                          | 1       |

|              |     | NEGOTIATION                      | 1 Enable                                                           |         |

| LED1         | 31  | SPEED                            | 0 10Base-T                                                         | 1       |

|              |     |                                  | 1 100Base-Tx                                                       |         |

| RXC          | 19  | POWER DOWN                       | 0 Disable                                                          | 0       |

|              |     | MODE                             | 1 Enable                                                           |         |

| TXC          | 22  | Reserved                         |                                                                    | 1       |

Table 3-9. Power-On Strapping<sup>[1]</sup>

[1]Default values: 0 = Pull-down, 1 = Pull-up with 10 K resistor.

#### 3.7 Typical Power Consumption Parameters

The following conditions apply to the typical characteristics unless otherwise specified:

$V_{DD33}$  = 3.3V,  $T_{amb}$  = 25 °C

Table 3-10 shows the typical power drain as a function of the AR8032's operating mode.

| Table 3-10. Total System Powe |

|-------------------------------|

|-------------------------------|

| Symbol            | AR8032 Power<br>Consumption (mW) | Total System (includes<br>XFMR and LEDO Power<br>Consumption (mW) | Description                  |

|-------------------|----------------------------------|-------------------------------------------------------------------|------------------------------|

| P <sub>LDPS</sub> | 10.9                             | 10.9                                                              | Link down, power-saving mode |

| P <sub>PWD</sub>  | 6.6                              | 6.6                                                               | Power Down Mode              |

Table 3-10. Total System Power

| Symbol               | AR8032 Power<br>Consumption (mW) | Total System (includes<br>XFMR and LEDO Power<br>Consumption (mW) | Description           |

|----------------------|----------------------------------|-------------------------------------------------------------------|-----------------------|

| P <sub>Isolate</sub> | 39.6                             | 52.8                                                              | Isolate mode          |

| P <sub>100F</sub>    | 123                              | 280                                                               | 100Base-T Full Duplex |

| P <sub>10F</sub>     | 52.5                             | 272                                                               | 10Base-T Full Duplex  |

| P <sub>10TX</sub>    | 49.5                             | 257.4                                                             | 10Base-T Transmit     |

| P <sub>10RX</sub>    | 49.5                             | 59.4                                                              | 10Base-T Receive      |

| P <sub>10IDLE</sub>  | 47.8                             | 69.3                                                              | 10Base-T Idle         |

**NOTE:** Total power includes power consumed by the center-tap of the transformer and the LEDs

Table 3-11 shows the Power Output Parameters of the AR8032's operating mode.

| Table 3-11. | Power | Output | Parameters |

|-------------|-------|--------|------------|

| 10010 0 11. |       | Juspas |            |

| Symbol    | Voltage Range | Total Consumption |

|-----------|---------------|-------------------|

| VDD12_REG | 1.2V ±5%      | 34 mA             |

| VDD25_REG | 2.5V +10%/-5% | 70 mA             |

**NOTE:** The 1.2V only has one regulator outpur pin, so the 1.2V current does not appear on the board. The VDD25\_REG total comsumption includes center tap power consumption.

#### 3.8 Power-on Sequence, Reset and Clock

#### 3.8.1 Power-on Sequence

The AR8032 only needs a single 3.3V power supply input. The 1.2V core and 2.5V I/O voltages are generated by AR8032's internal LDOs. So the AR8032's power-on sequence to establish the power rails stability is met internally.

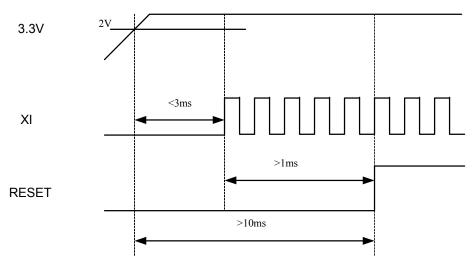

#### 3.8.2 Reset and Clock Timing

Figure 3-6 shows the Power-on Timing diagram.

Figure 3-6. Power-on Timing Diagram

AR8032 provides a hardware RESET pin, which must be asserted during power on and kept low for at least 10 ms after 3.3V rail reaches 2V.

AR8032 clock input XI must be supplied within 3ms after 3.3V rail reaching 2V and must be kept stable for at least 1ms before RESET is brought to high.

If designs with an external 25MHz clock (for MII mode) or 50MHz (for RMII mode) can not

meet the 3.3v to XI within the 3ms requirement, the PHY registers need be initialized (different from default value) immediately, as in the following — write debug register 0x12[3]=1'b0 then write debug register 0x29[2:0]=3'b100.

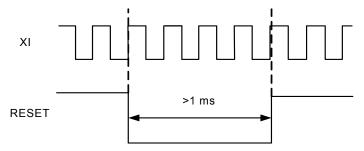

Once the power 3.3V rail is stable and clock XI is present then subsequent hardware reset signal must be a minimum of 1ms in duration.

Figure 3-7 shows the Warm Hardware Reset Diagram.

Figure 3-7. Warm Hardware Reset Diagram

## 4. Register Descriptions

Table 4-1 shows the reset types used in this document.

#### Table 4-1. Reset Types

| Туре   | Description                                                                                                                                                                                                                 |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LH     | Register field with latching high function.<br>If status is high, then the register is set to<br>one and remains set until a read operation<br>is performed through the management<br>interface or a reset occurs.          |

| LL     | Register field with latching low function.<br>If status is low, then the register is cleared<br>to a zero and remains cleared until a read<br>operation is performed through the<br>management interface or a reset occurs. |

| Retain | Value written to a register field takes effect without a software reset.                                                                                                                                                    |

| SC     | Self-Clear. Writing a one to this register<br>causes the desired function to execute<br>immediately, and the register field clears<br>to zero when the function is complete.                                                |

| Update | The value written to the register field does<br>not take effect until a software reset is<br>executed. The value can still be read after<br>it is written.                                                                  |

| RES    | Reserved for future use. All reserved bits are read as a zero unless otherworse noted.                                                                                                                                      |

| RO     | Read Only                                                                                                                                                                                                                   |

| ROC    | Read Only Clear. After read, register field is cleard to zero.                                                                                                                                                              |

| Table 4-1. | Reset Types | (continued) |

|------------|-------------|-------------|

|------------|-------------|-------------|

| Туре | Description                                                                                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W  | Read/Write                                                                                                                                                                               |

| RWC  | Read/Write Clear. After read, register field is cleared to zero.                                                                                                                         |

| RWR  | Read/Write Reset. All bits are readable<br>and writable. After reset or read, the<br>register field is cleard to zero.                                                                   |

| RWS  | Read/Write Set. All bits are readable and<br>writable. After reset or read, the register<br>field is set to a non-zero value specified in<br>the text.                                   |

| SC   | Self-Clear. Writing a one to this register<br>causes the desired function to be<br>immediately executed, then the register<br>field is cleared to zero when the function<br>is complete. |

| WO   | Write Only. Reads to this type of register return undefined data.                                                                                                                        |

#### 4.1 PHY Register Summary

Table 4-2 summarizes the registers for theAR8032.

| Table 4-2. | Register | Summary |

|------------|----------|---------|

|------------|----------|---------|

| Offset | Register                        | Page    |  |  |  |  |  |

|--------|---------------------------------|---------|--|--|--|--|--|

| 0x00   | Control Register                | page 22 |  |  |  |  |  |

| 0x01   | Status                          | page 24 |  |  |  |  |  |

| 0x02   | PHY Identifier                  | page 26 |  |  |  |  |  |

| 0x03   | PHY Identifier 2                | page 26 |  |  |  |  |  |

| 0x04   | Auto-Negotiation Advertisement  | page 29 |  |  |  |  |  |

| 0x05   | Link Partner Ability            | page 30 |  |  |  |  |  |

| 0x06   | Auto-Negotiation Expansion page |         |  |  |  |  |  |

| 0x07   | Reserved                        |         |  |  |  |  |  |

| 0x08   | Reserved                        |         |  |  |  |  |  |

| 0x09   | Reserved                        |         |  |  |  |  |  |

| 0x0A   | Reserved                        |         |  |  |  |  |  |

| 0x0B   | Reserved                        |         |  |  |  |  |  |

| Offset | Register                                | Page    |  |  |  |  |  |

|--------|-----------------------------------------|---------|--|--|--|--|--|

| 0x0C   | Reserved                                |         |  |  |  |  |  |

| 0x0D   | Reserved                                |         |  |  |  |  |  |

| 0x0E   | Reserved                                |         |  |  |  |  |  |

| 0x0F   | Reserved                                |         |  |  |  |  |  |

| 0x10   | Function Control Register               | page 22 |  |  |  |  |  |

| 0x11   | PHY Specific Status Register            | page 33 |  |  |  |  |  |

| 0x12   | Interrupt Enable Register               | page 34 |  |  |  |  |  |

| 0x13   | Interrupt Status Register               | page 36 |  |  |  |  |  |

| 0x14   | Smart Speed Register                    | page 38 |  |  |  |  |  |

| 0x15   | Recieve Error Counter Register          | page 40 |  |  |  |  |  |

| 0x16   | Virtual Cable Tester Control Register   | page 40 |  |  |  |  |  |

| 0x18   | LED Control Register                    | page 41 |  |  |  |  |  |

| 0x19   | Reserved                                |         |  |  |  |  |  |

| 0x1A   | Reserved                                |         |  |  |  |  |  |

| 0x1B   | Reserved                                |         |  |  |  |  |  |

| 0x1C   | Virtual Cable Tester Status Register    | page 40 |  |  |  |  |  |

| 0x1D   | Debug Port (Address Offset Set)         | page 43 |  |  |  |  |  |

| 0x1E   | Debug Port 2 (R/W Port) Register        | page 43 |  |  |  |  |  |

| 0x1F   | Reserved                                |         |  |  |  |  |  |

|        | Debug Register                          | 1       |  |  |  |  |  |

| 0x12   | 10 Base-T Test Configuration Register   | page 44 |  |  |  |  |  |

| 0x10   | 100 Base-TX Test Configuration Register | page 45 |  |  |  |  |  |

| 0x0B   | Hibernate Control Register              | page 47 |  |  |  |  |  |

| 0x29   | Power Saving Control                    | page 48 |  |  |  |  |  |

Table 4-2. Register Summary (continued)

## 4.1.1 Control Register

| Bit | Name     | Name Type         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                               |

|-----|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Reset    | Mode<br>HW<br>Rst | R/W<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PHY Software Reset. Writing a "1" to this bit causes the PHY the reset operation is done , this bit is cleared to "0" automatically. The reset occurs immediately.        |

|     |          | SW<br>Rst         | SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1= PHY reset<br>0 =Normal operation                                                                                                                                       |

| 14  | Loopback | Mode<br>HW<br>Rst | $ \begin{array}{c c} R/W \\ \hline \\ 0 \\ \hline \\ 0 \\ \hline \\ 0 \\ \hline 0 \\ 0 \\$ | When loopback is activated, the transmitter data presented on<br>TXD is looped back to RXD internally. Link is broken when<br>loopback is enabled.<br>1 = Enable Loopback |

|     |          | SW<br>Rst         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 = Disable Loopback                                                                                                                                                      |

| Bit | Name                         | Ту                             | ре                            | Description                                                                                                                                                                                                                                                |

|-----|------------------------------|--------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | Speed Selection<br>(LSB)     | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W<br>See<br>Desc.<br>Retain | Upon hardware reset , this bit and 0.6 bit depend upon<br>anen(bit0.12) and SPEED:<br>anen {0.6 , 0.13}<br>0 {0, SPEED}<br>1 2'b01<br>(00:10Mbps, 01:100Mbps, 10:Reserved, 11:Reserved)                                                                    |

| 12  | Auto-negotiation             | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W<br>See<br>Desc.<br>Retain | Upon hardware reset, this bit depends on ANEN_PAD.<br>1 = Enable Auto-Negotiation Process<br>0 = Disable Auto-Negotiation Process                                                                                                                          |

| 11  | Power Down                   | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W<br>0<br>0                 | When the port is switched from power down to normal operation, software reset and restart Auto-Negotiation are performed even when bits Reset (0.15) and Restart Auto-Negotiation (0.9) are not set by the user.<br>1 = Power down<br>0 = Normal operation |

| 10  | Isolate                      | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W<br>0<br>0                 | The MII output pins are tristated when this bit is set to 1.<br>The MII inputs are ignored.<br>1 = Isolate<br>0 = Normal operation                                                                                                                         |

| 9   | Restart Auto-<br>negotiation | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W,<br>SC<br>0<br>SC         | Auto-Negotiation automatically restarts after hardware or<br>software reset regardless of whether or not the restart bit (0.9) is<br>set.<br>1 = Restart Auto-Negotiation Process<br>0 = Normal operation                                                  |

| 8   | Duplex mode                  | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W,<br>SC<br>See<br>Desc.    | Upon hardware reset, this bit bit depends on<br>DUPLEX_MODE_PAD and anen bit(0.12):<br>0.12 0.8<br>0 0<br>1 DUPLEX_MODE_PAD<br>1:Full Duplex<br>0:Half Duplex                                                                                              |

| 7   | Collision Test               | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W<br>0<br>0                 | Setting this bit to 1 will cause the COL pin to assert whenever the TX_EN pin is asserted.<br>1 = Enable COL signal test<br>0 = Disable COL signal test                                                                                                    |

| 6   | Speed Selection<br>(MSB)     | Mode<br>HW<br>Rst<br>SW<br>Rst | R/W<br>See<br>Desc.           | See bit 0.13.                                                                                                                                                                                                                                              |

| Bit | Name | Туре      |       |                          | Description |

|-----|------|-----------|-------|--------------------------|-------------|

| 5:0 | RES  | Mode      | RO    | Reserved for future use. |             |

|     |      | HW<br>Rst | 00000 |                          |             |

|     |      | SW<br>Rst | 00000 |                          |             |

## 4.1.2 Status Register

| Bit | Name             | Ту        | ре  | Description                                                               |

|-----|------------------|-----------|-----|---------------------------------------------------------------------------|

| 15  | 15 100Base-T4    |           | RO  | 100BASE-T4.                                                               |

|     |                  | HW<br>Rst | 0   | This protocol is not available.<br>0 = PHY not able to perform 100BASE-T4 |

|     |                  | SW<br>Rst | 0   |                                                                           |

| 14  | 100Base-Tx Full- | Mode      | RO  | Capable of 100Base-Tx Full-Duplex operation                               |

|     | Duplex           | HW<br>Rst | 1   |                                                                           |

|     |                  | SW<br>Rst | 1   |                                                                           |

| 13  | 100Base-Tx Half- | Mode      | RO  | Capable of 100Base-Tx Half-Duplex operation                               |

|     | Duplex           | HW<br>Rst | 1   |                                                                           |

|     |                  | SW<br>Rst | 1   |                                                                           |

| 12  | 10 Mbps Full-    | Mode      | RO  | Capable of 10Base-T Full-Duplex operation                                 |

|     | Duplex           | HW<br>Rst | 1   |                                                                           |

|     |                  | SW<br>Rst | 1   |                                                                           |

| 11  | 10 Mbps Half-    | Mode      | R/W | Capable of 10 Mbps Half-Duplex operation                                  |

|     | Duplex           | HW<br>Rst | 1   |                                                                           |

|     |                  | SW<br>Rst | 1   |                                                                           |

| 10  | 100Base-T2 Full- | Mode      | RO  | Not able to perform 100Base-T2 Full-Duplex operation                      |

|     | Duplex           | HW<br>Rst | 0   |                                                                           |

|     |                  | SW<br>Rst | 0   |                                                                           |

| Bit | Name                       | Ту        | ре        | Description                                                                                                     |

|-----|----------------------------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------|

| 9   | 100Base-T2 Half-           | Mode      | R/W       | Not able to perform 100Base-T2 Half-Duplex operation                                                            |

|     | Duplex                     | HW<br>Rst | 0         |                                                                                                                 |

|     |                            | SW<br>Rst | 0         |                                                                                                                 |

| 8   | Extended Status            | Mode      | RO        | Extended status information in register 15                                                                      |

|     |                            | HW<br>Rst | 1         |                                                                                                                 |

|     |                            | SW<br>Rst | 1         |                                                                                                                 |

| 7   | RES                        | Mode      | RO        | Reserved                                                                                                        |

|     |                            | HW<br>Rst | 0         |                                                                                                                 |

|     |                            | SW<br>Rst | 0         |                                                                                                                 |

| 6   | MF Preamble<br>Suppression | Mode      | RO        | PHY accepts management frames with preamble suppressed                                                          |

|     | Suppression                | HW<br>Rst | 1         |                                                                                                                 |

|     |                            | SW<br>Rst | 1         |                                                                                                                 |

| 5   | Auto-negotiation           | Mode      | RO        | 1: Auto negotiation process complete                                                                            |

|     | Complete                   | HW<br>Rst | 0         | 0:Auto negotiation process not complete                                                                         |

|     |                            | SW<br>Rst | 0         |                                                                                                                 |

| 4   | Remote Fault               | Mode      | RO,<br>LH | 1: Remote fault condition detected<br>0:Remote fault condition not detected                                     |

|     |                            | HW<br>Rst | 0         |                                                                                                                 |

|     |                            | SW<br>Rst | 0         |                                                                                                                 |

| 3   | Auto-Negotiation           | Mode      | R/W       | 1: PHY able to perform auto-negotiation                                                                         |

|     | Ability                    | HW<br>Rst | 1         |                                                                                                                 |

|     |                            | SW<br>Rst | 1         |                                                                                                                 |

| 2   | Link Status                | Mode      | RO,<br>LL | This register bit indicates whether the link was lost since the last<br>read. For the current link status, read |

|     |                            | HW<br>Rst | 0         | register bit 17.10 Link Real Time.<br>1 = Link is up                                                            |

|     |                            | SW<br>Rst | 0         | 0 = Link is down                                                                                                |

| Bit | Name                     | Ту        | pe        | Description                                                      |

|-----|--------------------------|-----------|-----------|------------------------------------------------------------------|

| 1   | Jabber Detect            | Mode      | RO,<br>LH | 1: Jabber condition detected<br>0: Jabber condition not detected |

|     |                          | HW<br>Rst | 0         |                                                                  |

|     |                          | SW<br>Rst | 0         |                                                                  |