ASSP for Power Supply Applications (Secondary battery)

# DC/DC Converter IC of Synchronous Rectification for charging Li-ion battery

# MB39A119

#### **■ DESCRIPTION**

The MB39A119 is the N-ch MOS drive of the synchronous rectification type DC/DC converter IC using pulse-width modulation (PWM) type that can charge Li-ion battery from 1 cell to 4 cells and suitable for down-conversion.

This IC integrates built-in comparator for the voltage detection of the AC adapter and switches the power supply to the AC adapter or battery automatically, enabling supply it to system. In addition, the constant voltage control state detection function is built in, which prevents mis-detecting the full charge. The MB39A119 provides a wide range of power supply voltage and low standby current, high efficiency, making it ideal for use as a built-in charge device in products such as notebook PC.

#### **■ FEATURES**

- High efficiency: 97 % (Max)

- High-frequency operation: 1 MHz (Max)

- · Built-in off time control function

- Built-in voltage detection function of AC adapter (ACOK, XACOK terminal)

- Preventing mis-detection for the full charge by the constant voltage control state detection function (CVM terminal)

(Continued)

#### ■ PACKAGE

- Built-in two constant current control circuits

- Analog control of constant current value is possible ( + INE1, + INE2 terminal)

- Built-in output stage for N-ch MOS FET synchronous rectification

- Built-in charge stop function at low input voltage

- Output voltage setting accuracy : 4.2 V  $\pm$  0.74 % (Ta= 10 °C to + 85 °C)

- Built-in high accuracy charge current detection amplifier: ± 4 % (At input voltage difference 100 mV with Voltage gain 24.5 (V/V)

- Built-in high accuracy input current detection amplifier :  $\pm$  3 % (At input voltage difference 100 mV with Voltage gain 25 (V/V)

- Arbitrary output voltage can be set by external resistor

- In IC standby mode, output voltage setting resistor is made to be open to prevent inefficient current loss

- Quiescent current : 1.9 mA (Typ)

Standby current : 0 μA (Typ)

- Package : QFN28

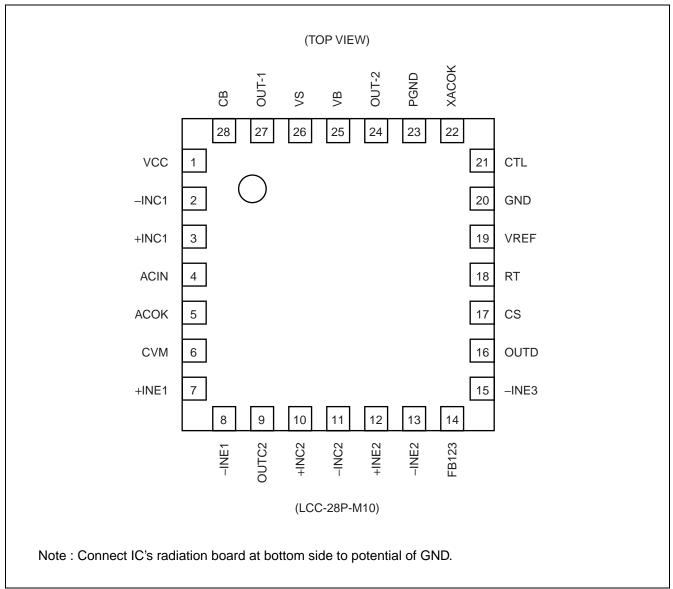

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                   |

|---------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCC      |     | Power supply terminal for reference voltage and control circuit.                                                                                                              |

| 2       | -INC1    | I   | Input current detection amplifier (Current Amp1) input terminal.                                                                                                              |

| 3       | + INC1   | I   | Input current detection amplifier (Current Amp1) input terminal.                                                                                                              |

| 4       | ACIN     | I   | AC adapter voltage detection block (AC Comp.) input terminal.                                                                                                                 |

| 5       | ACOK     | 0   | AC adapter voltage detection block (AC Comp.) output terminal.  ACOK = L when ACIN = H, ACOK = Hi-Z when ACIN = L,  ACOK = Hi-Z when CTL = L                                  |

| 6       | CVM      | 0   | Constant voltage control state detection block (CV Comp.) output terminal.                                                                                                    |

| 7       | + INE1   | I   | Error amplifier (Error Amp1) non-inverted input terminal.                                                                                                                     |

| 8       | -INE1    | I   | Error amplifier (Error Amp1) inverted input terminal.                                                                                                                         |

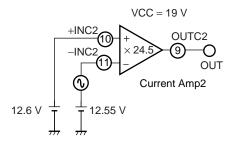

| 9       | OUTC2    | 0   | Charge current detection amplifier (Current Amp2) output terminal.                                                                                                            |

| 10      | + INC2   | I   | Charge current detection amplifier (Current Amp2) input terminal.                                                                                                             |

| 11      | -INC2    | I   | Charge current detection amplifier (Current Amp2) and low input voltage detection comparator (UV Comp.) input terminal.                                                       |

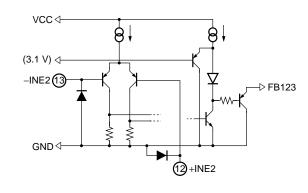

| 12      | + INE2   | Į   | Error amplifier (Error Amp2) non-inverted input terminal.                                                                                                                     |

| 13      | - INE2   | I   | Error amplifier (Error Amp2) inverted input terminal.                                                                                                                         |

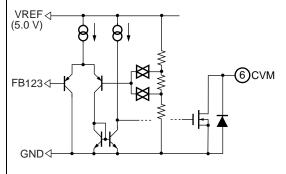

| 14      | FB123    | 0   | Error amplifier (Error Amp1, 2, 3) output terminal.                                                                                                                           |

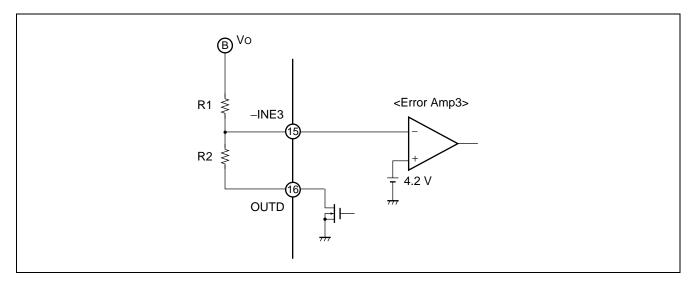

| 15      | -INE3    | I   | Error amplifier (Error Amp3) inverted input terminal.                                                                                                                         |

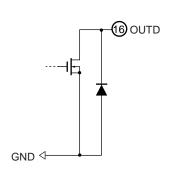

| 16      | OUTD     | 0   | This terminal is set to Hi-Z to prevent loss of current through the output voltage setting resistor when IC is standby mode.  OUTD = Hi-Z when CTL = L  OUTD = L when CTL = H |

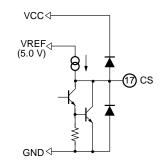

| 17      | CS       |     | Soft-start capacitor connection terminal.                                                                                                                                     |

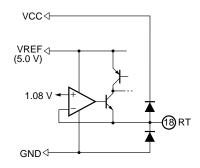

| 18      | RT       |     | Triangular wave oscillation frequency setting resistor connection terminal.                                                                                                   |

| 19      | VREF     | 0   | Reference voltage output terminal.                                                                                                                                            |

| 20      | GND      |     | Ground terminal.                                                                                                                                                              |

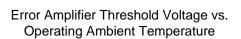

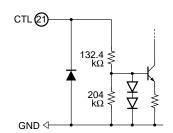

| 21      | CTL      | I   | Power supply control terminal for DC/DC converter block.                                                                                                                      |

| 22      | XACOK    | 0   | AC adapter voltage detection block (AC Comp.) output terminal.  XACOK = Hi-Z when ACIN = H, XACOK = L when ACIN = L,  XACOK = Hi-Z when CTL = L                               |

| 23      | PGND     |     | Ground terminal.                                                                                                                                                              |

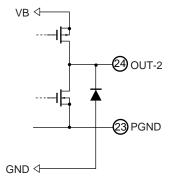

| 24      | OUT-2    | 0   | External synchronous rectification side FET gate drive output terminal.                                                                                                       |

| 25      | VB       | 0   | Bias output terminal for output circuit.                                                                                                                                      |

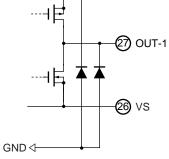

| 26      | VS       | _   | External main side FET source conneciton terminal.                                                                                                                            |

| 27      | OUT-1    | 0   | External main side FET gate drive output terminal.                                                                                                                            |

| 28      | СВ       | _   | Boot strap capacitor connection terminal.  The capacitor is connected between the CB terminal and the VS terminal.                                                            |

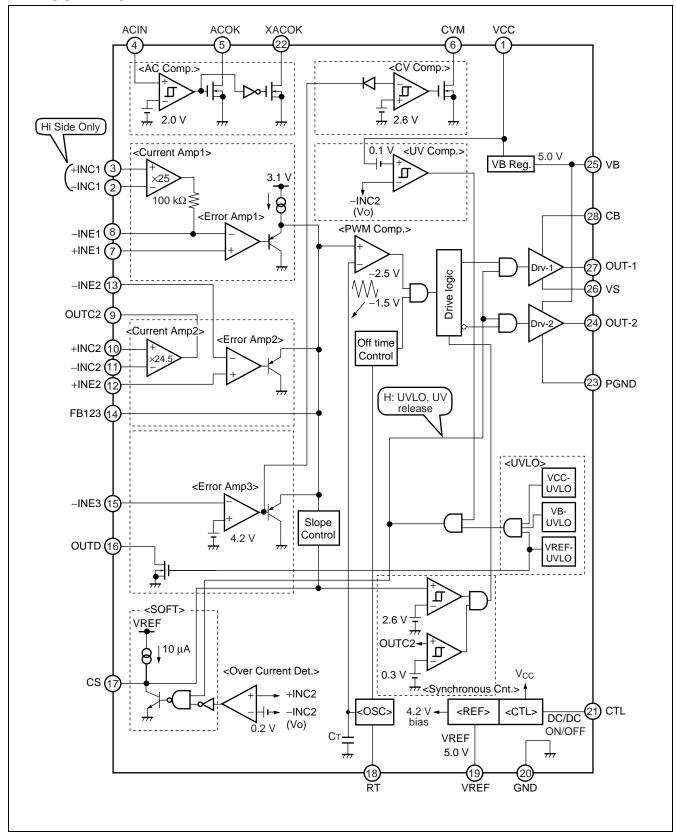

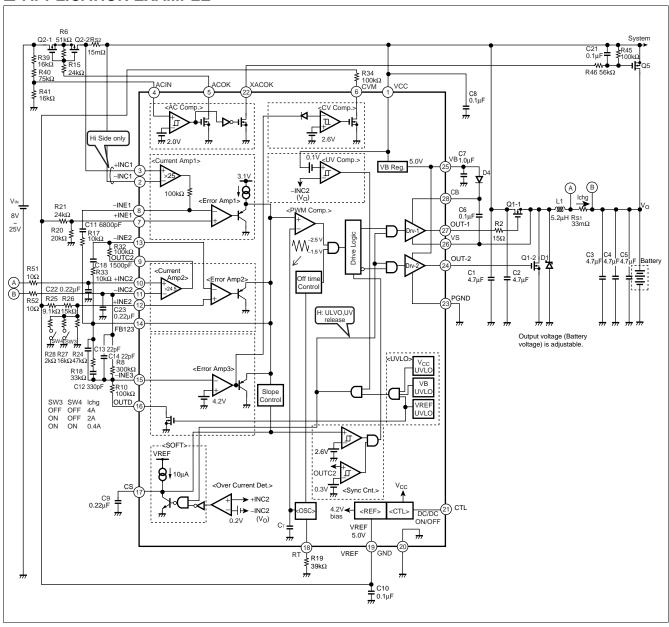

#### **■ BLOCK DIAGRAM**

#### ■ ABSOLUTE MAXIMUM RATINGS

| Doromotor                     | Symbol Condition  |                                                    | Ra         | Rating    |      |  |

|-------------------------------|-------------------|----------------------------------------------------|------------|-----------|------|--|

| Parameter                     | Symbol            | Condition                                          | Min        | Max       | Unit |  |

| Power supply voltage          | Vcc               | VCC terminal                                       | _          | 27        | V    |  |

| CB terminal input voltage     | Vсв               | CB terminal                                        | _          | 32        | V    |  |

| Control input voltage         | Vctl              | CTL terminal                                       |            | 27        | V    |  |

|                               | VINE              | + INE1, + INE2, - INE1, - INE2,<br>- INE3 terminal | _          | Vcc + 0.3 | V    |  |

| Input voltage                 | V <sub>INC1</sub> | + INC1, - INC1 terminal                            | _          | Vcc + 0.3 | V    |  |

|                               | V <sub>INC2</sub> | + INC2, - INC2 terminal                            | _          | 20        | V    |  |

| OUTD terminal output voltage  | Voutd             | OUTD terminal                                      | _          | 20        | V    |  |

| ACIN input voltage            | Vacin             | ACIN terminal                                      | _          | Vcc       | V    |  |

| ACOK terminal output voltage  | Vacok             | ACOK terminal                                      | _          | 27        | V    |  |

| XACOK terminal output voltage | Vxacok            | XACOK terminal                                     | _          | 27        | V    |  |

| CVM terminal output voltage   | Vcvm              | CVM terminal                                       | _          | 27        | V    |  |

| Output current                | lоит              | _                                                  | _          | 60        | mA   |  |

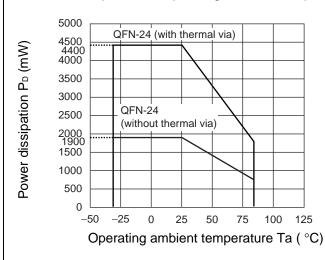

| Dower dissination             | Pp                | Ta ≤ +25 °C                                        | _          | 4400*1,*2 |      |  |

| Power dissipation             | <b>Γ</b> υ        | I a > +20 U                                        | _          | 1900*1,*3 | mW   |  |

| Storage temperature           | Тѕтс              | _                                                  | <b>-55</b> | + 125     | °C   |  |

<sup>\*1 :</sup> The packages are mounted on the dual-sided epoxy board (10 cm  $\times$  10cm) .

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

<sup>\*2:</sup> With connection of exposed pad and with thermal via.

<sup>\*3:</sup> With connection of exposed pad and without thermal via.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Davamatar                          | Cumbal            | Condition                                          |       | Value |       | Unit |

|------------------------------------|-------------------|----------------------------------------------------|-------|-------|-------|------|

| Parameter                          | Symbol            | Condition                                          | Min   | Тур   | Max   | Unit |

| Power supply voltage               | Vcc               | VCC terminal                                       | 8     | _     | 25    | V    |

| CB terminal input voltage          | Vсв               | CB terminal                                        |       |       | 30    | V    |

| Reference voltage output current   | IREF              | VREF terminal                                      | -1    |       | 0     | mA   |

| Bias output current                | Ivв               | VB terminal                                        | -1    |       | 0     | mA   |

|                                    | VINE              | + INE1, + INE2, - INE1,<br>- INE2, - INE3 terminal | 0     | _     | 5     | V    |

| Input voltage                      | VINC1             | + INC1, -INC1 terminal                             | 7     | _     | Vcc   | V    |

|                                    | V <sub>INC2</sub> | + INC2, -INC2 terminal                             | 0     |       | 19    | V    |

| Input voltage difference           | Dvinc             | Current detection voltage range                    | 0     | _     | 140   | mV   |

| OUTD terminal output voltage       | Voutd             | OUTD terminal                                      | 0     | _     | 19    | V    |

| OUTD terminal output current       | loutd             | OUTD terminal                                      | 0     | _     | 2     | mA   |

| CTL terminal input voltage         | Vctl              | CTL terminal                                       | 0     |       | 25    | V    |

| ACIN input voltage                 | Vacin             | ACIN terminal                                      | 0     |       | Vcc   | V    |

| ACOK terminal output voltage       | Vacok             | ACOK terminal                                      | 0     | _     | 25    | V    |

| XACOK terminal output voltage      | Vxacok            | XACOK terminal                                     | 0     | _     | 25    | V    |

| CVM terminal output voltage        | Vс∨м              | CVM terminal                                       | 0     |       | 25    | V    |

| Peak output current                | Іоит              | Duty ≤ 5 % (t=1/fosc × Duty)                       | -1200 | _     | +1200 | mA   |

| Oscillation frequency              | fosc              | _                                                  | 200   | 500   | 1000  | kHz  |

| Timing resistor                    | R⊤                | RT terminal                                        |       | 39    |       | kΩ   |

| Soft-start capacitor               | Cs                | CS terminal                                        | _     | 0.22  | _     | μF   |

| CB terminal capacitor              | Св                | CB terminal                                        | _     | 0.1   | _     | μF   |

| Bias output capacitor              | Сув               | VB terminal                                        | _     | 1.0   | _     | μF   |

| Reference voltage output capacitor | Cref              | VREF terminal                                      | _     | 0.1   | 1.0   | μF   |

| Operating ambient temperature      | Та                | _                                                  | -30   | +25   | +85   | °C   |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

### **■ ELECTRICAL CHARACTERISTICS**

(VCC = 19 V, VB = 0 mA, VREF = 0 mA, Ta = +25 °C)

| _                             | ,                                     |                   | D: N     | (                                                             | <u> </u> | Value |       | 11:4 |

|-------------------------------|---------------------------------------|-------------------|----------|---------------------------------------------------------------|----------|-------|-------|------|

| Pa                            | arameter                              | Symbol            | Pin No.  | Conditions                                                    | Min      | Тур   | Max   | Unit |

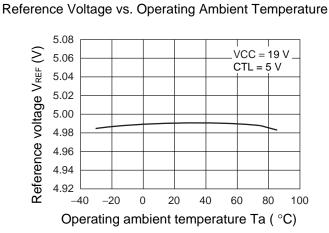

|                               | Output valtage                        | V <sub>REF1</sub> | 19       | Ta = +25 °C                                                   | 4.963    | 5.000 | 5.037 | V    |

| Reference                     | Output voltage                        | V <sub>REF2</sub> | 19       | $Ta = -10 ^{\circ}\text{C} \text{ to } + 85 ^{\circ}\text{C}$ | 4.95     | 5.00  | 5.05  | V    |

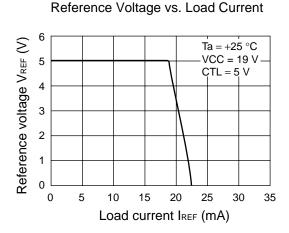

| voltage                       | Input stability                       | Line              | 19       | VCC = 8 V to 25 V                                             | _        | 1     | 10    | mV   |

| block                         | Load stability                        | Load              | 19       | VREF = 0  mA to  -1  mA                                       | _        | 1     | 10    | mV   |

| [REF]                         | Short-circuit output current          | los               | 19       | VREF = 1 V                                                    | -60      | -30   | -15   | mA   |

|                               | Throshold voltage                     | VTLH              | 1        | VCC                                                           | _        | 7.5   | 7.9   | V    |

|                               | Threshold voltage                     | VTHL              | 1        | VCC                                                           | 7.0      | 7.4   |       | V    |

| Under                         | Hysteresis width                      | Vн                | 1        | VCC                                                           | _        | 0.1   |       | V    |

| voltage                       | There also led violate are            | VTLH              | 25       | VB                                                            | 3.8      | 4.0   | 4.2   | V    |

| lockout<br>protection         | Threshold voltage                     | VTHL              | 25       | VB                                                            | 3.1      | 3.3   | 3.5   | V    |

| circuit block                 | Hysteresis width                      | Vн                | 25       | VB                                                            | _        | 0.7   |       | V    |

| [UVLO]                        | There also led violate are            | VTLH              | 19       | VREF                                                          | 2.5      | 2.7   | 2.9   | V    |

|                               | Threshold voltage                     | V <sub>THL</sub>  | 19       | VREF                                                          | 2.3      | 2.5   | 2.7   | V    |

|                               | Hysteresis width                      | Vн                | 19       | VREF                                                          | _        | 0.2   |       | V    |

| Soft-start<br>block<br>[SOFT] | Charge current                        | Ics               | 17       | _                                                             | -14      | -10   | -6    | μΑ   |

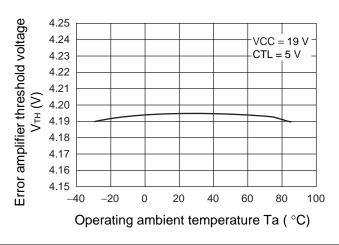

| Triangular<br>wave            | Oscillation frequency                 | fosc              | 27       | RT = 39 kΩ                                                    | 450      | 500   | 550   | kHz  |

| oscillator<br>block<br>[OSC]  | Frequency<br>temperature<br>stability | Δf/fdt            | 27       | Ta = -30 °C to +85 °C                                         | _        | 1*    | _     | %    |

|                               | Input offset voltage                  | Vıo               | 7, 8     | _                                                             | _        | 1     | 5     | mV   |

|                               | Input bias current                    | lв                | 7, 8     | _                                                             | -50      | -15   |       | nA   |

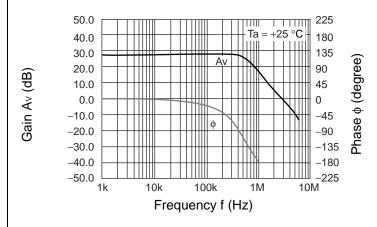

|                               | Voltage gain                          | A۷                | 7, 8, 14 | DC                                                            | _        | 100*  | _     | dB   |

| Error<br>amplifier            | Frequency bandwidth                   | BW                | 7, 8, 14 | Av = 0 dB                                                     | _        | 1.2*  | _     | MHz  |

| block<br>[Error               | Outrast valtage                       | V <sub>FBH</sub>  | 14       | _                                                             | 2.9      | 3.1   |       | V    |

| Amp1]                         | Output voltage                        | V <sub>FBL</sub>  | 14       | _                                                             | _        | 0.8   | 0.9   | V    |

|                               | Output source current                 | ISOURCE           | 14       | FB123 = 2 V                                                   | _        | -60   | -30   | μΑ   |

|                               | Output sink current                   | İsink             | 14       | FB123 = 2 V                                                   | 2.0      | 4.0   |       | mA   |

<sup>\*:</sup> Standard design value

(VCC = 19 V, VB = 0 mA, VREF = 0 mA, Ta = +25  $^{\circ}$ C)

|                            |                                    |                    |               |                                                                                    |       | Value |       |      |

|----------------------------|------------------------------------|--------------------|---------------|------------------------------------------------------------------------------------|-------|-------|-------|------|

|                            | Parameter                          | Symbol             | Pin No.       | Conditions                                                                         | Min   | Тур   | Max   | Unit |

|                            | Input offset voltage               | Vio                | 12, 13        | _                                                                                  | _     | 1     | 5     | mV   |

|                            | Input bias current                 | Ів                 | 12, 13        | _                                                                                  | -50   | -15   |       | nA   |

| Error                      | Voltage gain                       | Av                 | 12, 13,<br>14 | DC                                                                                 |       | 100*  | _     | dB   |

| amplifier<br>block         | Frequency bandwidth                | BW                 | 12, 13,<br>14 | Av = 0dB                                                                           | _     | 1.2*  | _     | MHz  |

| [Error<br>Amp2]            | Output voltage                     | V <sub>FBH</sub>   | 14            | _                                                                                  | 2.9   | 3.1   |       | V    |

|                            | Output voltage                     | V <sub>FBL</sub>   | 14            | _                                                                                  |       | 0.8   | 0.9   | V    |

|                            | Output source current              | ISOURCE            | 14            | FB123 = 2 V                                                                        | _     | -60   | -30   | μΑ   |

|                            | Output sink current                | Isink              | 14            | FB123 = 2 V                                                                        | 2.0   | 4.0   |       | mΑ   |

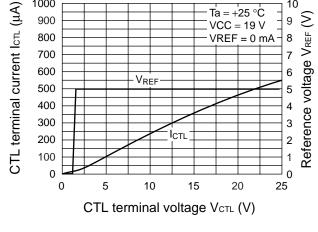

|                            |                                    | V <sub>TH1</sub>   | 14, 15        | FB123 = 2 V                                                                        | 4.179 | 4.200 | 4.221 | V    |

|                            | Threshold voltage                  | V <sub>TH2</sub>   | 14, 15        | FB123 = 2 V,<br>Ta = -10 °C to +85 °C                                              | 4.169 | 4.200 | 4.231 | ٧    |

|                            | Voltage gain                       | Av                 | 14, 15        | DC                                                                                 | _     | 100*  |       | dB   |

| Error                      | Frequency bandwidth                | BW                 | 14, 15        | Av = 0 dB                                                                          | _     | 1.2*  |       | MHz  |

| amplifier                  | Output valtage                     | V <sub>FBH</sub>   | 14            | _                                                                                  | 2.9   | 3.1   |       | V    |

| block                      | Output voltage                     | V <sub>FBL</sub>   | 14            | _                                                                                  | _     | 0.8   | 0.9   | V    |

| [Error<br>Amp3]            | Output source current              | Isource            | 14            | FB123 = 2 V                                                                        | _     | -60   | -30   | μА   |

| Ampoj                      | Output sink current                | Isink              | 14            | FB123 = 2 V                                                                        | 2.0   | 4.0   |       | mΑ   |

|                            | OUTD terminal leak current         | ILEAK              | 16            | OUTD = 19 V                                                                        | _     | 0     | 1     | μА   |

|                            | OUTD terminal output ON resistance | Ron                | 16            | OUTD = 1 mA                                                                        |       | 35    | 50    | Ω    |

|                            | Current detection                  | Voutc <sub>1</sub> | 8             | $+ INC1 = - INC1 = 7 \text{ V to } 19 \text{ V},$ $\Delta V_{IN} = 100 \text{ mV}$ | 2.425 | 2.5   | 2.575 | ٧    |

|                            | voltage                            | Voutc2             | 8             | + INC1 = - INC1 = 7 V to 19 V,<br>$\Delta V_{IN} = 20 \text{ mV}$                  | 0.425 | 0.5   | 0.575 | V    |

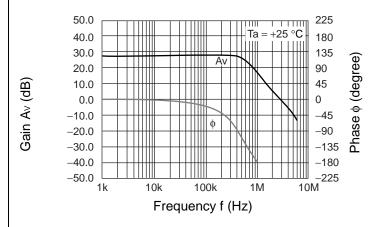

| Current                    | Voltage gain                       | Av                 | 2, 3, 8       | + INC1 = - INC1 = 7 V to 19 V,<br>$\Delta V_{IN} = 100 \text{ mV}$                 | 24.25 | 25    | 25.75 | V/V  |

| detection                  | Input offset voltage               | Vio                | 2, 3, 8       | + INC1 = - INC1 = 7 V to 19 V                                                      | -3    | _     | +3    | mV   |

| amplifier                  |                                    | INC1               | 2, 3          | + INC1 = - INC1 = 7 V to 19 V                                                      | _     | 20    | 30    | μΑ   |

| block<br>[Current<br>Amp1] | Input current                      | I <sub>INC2</sub>  | 2, 3          | + INC1 = - INC1 = 7 V to 19 V,<br>CTL = 0 V                                        |       | 0     | 1     | μА   |

|                            | Frequency bandwidth                | BW                 | 2, 3, 8       | Av = 0 dB                                                                          | —     | 3.0*  |       | MHz  |

|                            | Output voltage                     | Vоитсн             | 8             | _                                                                                  | 3.7   | 4.0   |       | V    |

|                            | Output voltage                     | Voutcl             | 8             | _                                                                                  | _     | 0.04  | 0.2   | V    |

|                            | Output source current              | ISOURCE            | 8             | -INE1 = 2 V                                                                        | _     | -1.2  | -0.6  | mA   |

|                            | Output sink current                | Isink              | 8             | -INE1 = 2 V                                                                        | 100   | 200   |       | μΑ   |

<sup>\*:</sup> Standard design value

(VCC = 19 V, VB = 0 mA, VREF = 0 mA, Ta = +25  $^{\circ}$ C)

| Paramete:                                           |                       | Symbol  | Pin No.   | 0 1111                                                                       |       | Value |       | Unit |

|-----------------------------------------------------|-----------------------|---------|-----------|------------------------------------------------------------------------------|-------|-------|-------|------|

| '                                                   | Parameter             |         |           | Conditions                                                                   | Min   | Тур   | Max   | Unit |

|                                                     |                       | Voutc1  | 9         | + INC2 = - INC2 = 3 V to 19 V,<br>$\Delta V_{IN} = 100 \text{ mV}$           | 2.38  | 2.48  | 2.58  | V    |

|                                                     | Current detection     | Voutc2  | 9         | + INC2 = - INC2 = 3 V  to  19 V,<br>$\Delta V_{IN} = 20 \text{ mV}$          | 0.44  | 0.52  | 0.60  | V    |

|                                                     | voltage               | Vоитсз  | 9         | + INC2 = - INC2 = 0 V to 3 V,<br>$\Delta V_{IN} = 100 \text{ mV}$            | 2.24  | 2.45  | 2.66  | V    |

|                                                     |                       | Voutc4  | 9         | + INC2 = $-$ INC2 = 0 V to 3 V,<br>$\Delta$ V <sub>IN</sub> = 20 mV          | 0.30  | 0.5   | 0.70  | V    |

| Current                                             | Voltage gain          | Av      | 9, 10, 11 | + INC2 = - INC2 = 3 V  to  19 V,<br>$\Delta V_{IN} = 100 \text{ mV}$         | 23.76 | 24.5  | 25.24 | V/V  |

| detection                                           | Input offset voltage  | Vio     | 9, 10, 11 | + INC2 = - INC2 = 3 V to 19 V                                                | -1.5  | +1.5  | +4.5  | mV   |

| amplifier<br>block<br>[Current                      |                       | I+inch  | 10        | $ + INC2 = -INC2 = 3 V \text{ to } 19 V, $ $\Delta V_{IN} = 100 \text{ mV} $ |       | 30    | 45    | μΑ   |

| Amp2]                                               | Input current         | І-інсн  | 11        | + INC2 = - INC2 = 3 V  to  19 V,<br>$\Delta V_{IN} = 100 \text{ mV}$         |       | 0.1*  | _     | μΑ   |

|                                                     |                       | Incl    | 10, 11    | + INC2 = - INC2 = 0 V                                                        | -300  | -200  |       | μΑ   |

|                                                     | Frequency bandwidth   | BW      | 9, 10, 11 | Av = 0 dB                                                                    | _     | 3.0*  | _     | MHz  |

|                                                     | Output voltage        | Vоитсн  | 9         | _                                                                            | 3.9   | 4.2   | _     | V    |

|                                                     | Odiput voltage        | Voutcl  | 9         | _                                                                            | _     | 0.04  | 0.2   | V    |

|                                                     | Output source current | Isource | 9         | OUTC2 = 2 V                                                                  |       | -1.2  | -0.6  | mA   |

|                                                     | Output sink current   | Isink   | 9         | OUTC2 = 2 V                                                                  | 100   | 200   |       | μΑ   |

| PWM                                                 |                       | VTL     | 14        | Duty cycle = 0%                                                              | _     | 1.5   |       | V    |

| compara-<br>tor block<br>[PWM<br>Comp.]             | Threshold voltage     | Vтн     | 14        | Duty cycle = 100%                                                            | _     | 2.5   | _     | V    |

| Output                                              | Output ON             | Rон     | 24, 27    | OUT-1, OUT-2 = -100 mA                                                       | —     | 4     | 7     | Ω    |

| block<br>[Drv-1, 2]                                 | resistance            | RoL     | 24, 27    | OUT-1, OUT-2 = 100 mA                                                        | _     | 1     | 3.5   | Ω    |

| Under                                               | Threshold voltage     | VTLH    | 11        | -INC2 = 12.6 V                                                               | 12.6  | 12.8  | 13.0  | V    |

| input<br>voltage                                    | Threshold voltage     | VTHL    | 11        | -INC2 = 12.6 V                                                               | 12.5  | 12.7  | 12.9  | V    |

| detection<br>compara-<br>tor block<br>[UV<br>Comp.] | Hysteresis width      | Vн      | 11        | _                                                                            | _     | 0.1   | _     | V    |

<sup>\*:</sup> Standard design value

### (Continued)

(VCC = 19 V, VB = 0 mA, VREF = 0 mA, Ta = +25  $^{\circ}$ C)

|                                                             |                                     | Comple ed        | Din Na  | O a maliti a ma        |       | Value |       | Unit |

|-------------------------------------------------------------|-------------------------------------|------------------|---------|------------------------|-------|-------|-------|------|

| Parameter                                                   |                                     | Symbol           | Pin No. | Conditions             | Min   | Тур   | Max   | Unit |

| Overcurrent<br>detection<br>block<br>[Over<br>Current Det.] | Threshold voltage                   | V <sub>TLH</sub> | 11      | -INC2 = 12.6 V         | 12.75 | 12.8  | 12.85 | ٧    |

|                                                             | Threshold voltage                   | VTLH             | 4       |                        | 2.056 | 2.12  | 2.184 | V    |

|                                                             | Threshold voltage                   | VTHL             | 4       | _                      | 1.959 | 2.02  | 2.081 | V    |

|                                                             | Hysteresis width                    | Vн               | 4       | _                      | _     | 0.1   |       | V    |

| AC adapter voltage                                          | ACOK terminal output leak current   | ILEAK            | 5       | ACOK = 25 V            |       | 0     | 1     | μΑ   |

| detection<br>block<br>[AC Comp.]                            | ACOK terminal output ON resistance  | Ron              | 5       | ACOK = 1 mA            |       | 200   | 400   | Ω    |

| [//C Comp.]                                                 | XACOK terminal output leak current  | ILEAK            | 22      | XACOK = 25 V           |       | 0     | 1     | μΑ   |

|                                                             | XACOK terminal output ON resistance | Ron              | 22      | XACOK = 1 mA           |       | 200   | 400   | Ω    |

|                                                             | Threshold voltage                   | V <sub>TLH</sub> | 14      | _                      |       | 2.7*  |       | V    |

| Constant                                                    |                                     | VTHL             | 14      | _                      | _     | 2.6*  | _     | V    |

| voltage<br>control state                                    | Hysteresis width                    | Vн               | 14      | _                      | _     | 0.1*  |       | V    |

| detection<br>block                                          | CVM terminal output leak current    | ILEAK            | 6       | CVM = 25 V             |       | 0     | 1     | μА   |

| [CV Comp.]                                                  | CVM terminal output ON resistance   | Ron              | 6       | CVM = 1 mA             |       | 200   | 400   | Ω    |

|                                                             | CS threshold                        | V <sub>TLH</sub> | 17      | _                      | 2.55  | 2.6   | 2.65  | V    |

| Synchronous                                                 | voltage                             | V <sub>THL</sub> | 17      | _                      | 2.50  | 2.55  | 2.60  | V    |

| rectification control block                                 | Hysteresis width                    | Vн               | 17      | _                      | _     | 0.05  |       | V    |

| [Synchronous                                                | Light load detection                | VTLH             | 9       | _                      | 0.35  | 0.4   | 0.45  | V    |

| Cnt.]                                                       | threshold voltage                   | V <sub>THL</sub> | 9       | _                      | 0.25  | 0.3   | 0.35  | V    |

|                                                             | Hysteresis width                    | Vн               | 9       | _                      |       | 0.1   |       | V    |

| Bias voltage                                                | Output voltage                      | Vв               | 25      | _                      | 4.9   | 5.0   | 5.1   | V    |

| block<br>[VB]                                               | Load stability                      | Load             | 25      | VB = 0  mA to  -10  mA | _     | 10    | 50    | mV   |

| Control block                                               | CTL                                 | Von              | 21      | IC operating state     | 2     | _     | 25    | V    |

|                                                             | input voltage                       | Voff             | 21      | IC standby state       | 0     | _     | 0.8   | V    |

| [CTL]                                                       | Input current                       | Істьн            | 21      | CTL = 5 V              | —     | 25    | 40    | μΑ   |

|                                                             | pat odiront                         | ICTLL            | 21      | CTL = 0 V              | _     | 0     | 1     | μΑ   |

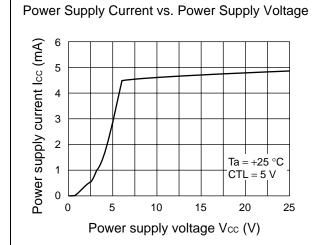

| General                                                     | Standby current                     | Iccs             | 1       | CTL = 0 V              | _     | 0     | 10    | μΑ   |

| 20110101                                                    | Power supply current                | Icc              | 1       | CTL = 5 V              | _     | 1.9   | 2.9   | mA   |

<sup>\*:</sup> Standard design value

#### **■ TYPICAL CHARACTERISTICS**

Triangular Wave Oscillation Frequency vs.

Operating Ambient Temperature

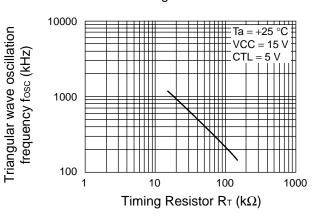

Triangular Wave Oscillation Frequency vs.

Timing Resistor

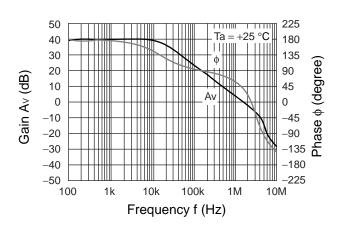

Error Amplifier Gain, Phase vs. Frequency (ERR1, 2)

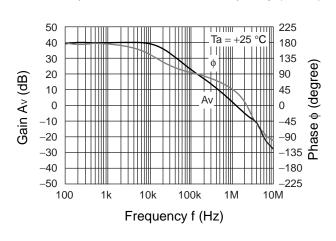

Error Amplifier Gain, Phase vs. Frequency (ERR3)

#### (Continued)

#### Current Detection Amplifier Gain, Phase vs. Frequency

#### Current Detection Amplifier Gain, Phase vs. Frequency

#### Power Dissipation vs. Operating Ambient Temperature

#### **■ FUNCTION DESCRIPTION**

#### 1. DC/DC Converter Block

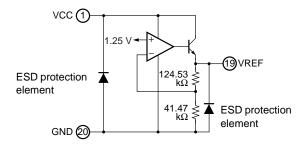

#### (1) Reference voltage block (REF)

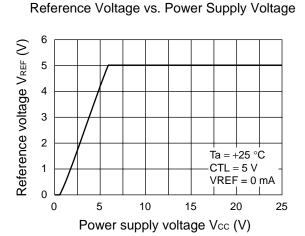

The reference voltage circuit uses the voltage supplied from the VCC terminal (pin 1) to generate a temperature compensated, stable voltage (5.0 V Typ) used as the reference power supply voltage for the IC's internal circuitry. This block can also be used to obtain a load current to a maximum of 1 mA from the reference voltage VREF terminal (pin 19).

#### (2) Triangular wave oscillator block (OSC)

The triangular wave oscillator block has built-in capacitor for frequency setting and generates the triangular wave oscillation waveform by connecting the triangular wave oscillation frequency setting resistor with the RT terminal (pin 17).

The triangular wave is input to the PWM comparator circuits on the IC.

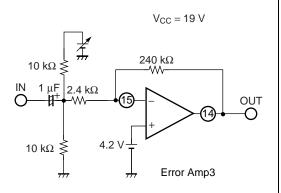

#### (3) Error amplifier block (Error Amp1)

This amplifier detects the output signal from the current detection amplifier (Current Amp1), compares this to the +INE1 terminal (pin 7), and outputs a PWM control signal to be used in controlling the charge current.

In addition, an arbitrary loop gain can be set up by connecting a feedback resistor and capacitor between the FB123 terminal (pin 14) and -INE1 terminal (pin 8), providing stable phase compensation to the system.

#### (4) Error amplifier block (Error Amp2)

This amplifier detects the output signal from the current detection amplifier (Current Amp2), compares this to the +INE2 terminal (pin 12), and outputs a PWM control signal to be used in controlling the charge current.

In addition, an arbitrary loop gain can be set up by connecting a feedback resistor and capacitor between the FB123 terminal (pin 14) and -INE2 terminal (pin 13), providing stable phase compensation to the system.

#### (5) Error amplifier block (Error Amp3)

This error amplifier (Error Amp3) detects the output voltage from the DC/DC converter and outputs the PWM control signal. External output voltage setting resistors can be connected to the error amplifier inverted input terminal to set the desired level of output voltage from 1 cell to 4 cells.

In addition, an arbitrary loop gain can be set by connecting a feedback resistor and capacitor from the FB123 terminal (pin 14) to the -INE3 terminal (pin 15) of the error amplifier, enabling stable phase compensation to the system.

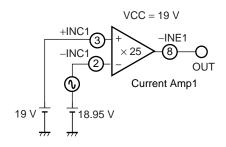

#### (6) Current detection amplifier block (Current Amp1)

The current detection amplifier (Current Amp1) detects a voltage drop which occurs between both ends of the output sense resistor (Rs2) due to the flow of the AC adapter current, using the +INC1 terminal (pin 3) and -INC1 terminal (pin 2) . The AC adapter current control signal is amplified to 25 times and output to the inverse input terminal of Error Amp1 through the internal 100 k $\Omega$ .

This amplifier cannot use for detecting the charge current.

#### (7) Current detection amplifier block (Current Amp2)

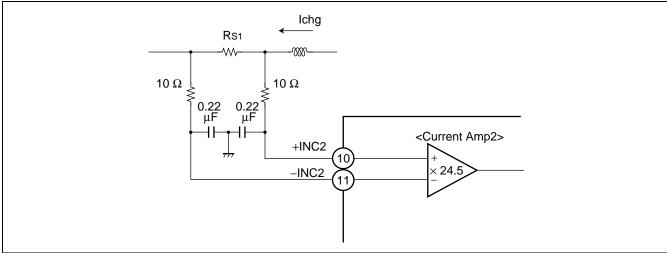

The current detection amplifier (Current Amp2) detects a voltage drop which occurs between both ends of the output sense resistor (Rs1) due to the flow of the charge current, using the +INC2 terminal (pin 10) and -INC2 terminal (pin 11). The signal amplified to 24.5 times is output to the OUTC2 terminal (pin 9).

#### (8) PWM comparator block (PWM Comp.)

The PWM comparator circuit is a voltage-pulse width converter for controlling the output duty of the error amplifiers (Error Amp1 to Error Amp3) depending on their output voltage.

The PWM comparator circuit compares with either of low voltages between the triangular wave voltage generated by the triangular wave oscillator and the error amplifier output voltage, turns on the main side output transistor

and turns off on the synchronous rectification side output transistor, during the interval in which the triangular wave voltage is lower than the error amplifier output voltage.

#### (9) Output block (Drv-1, 2)

The output circuit uses a CMOS configuration capable of driving an external N-ch MOS FET both main side and synchronous rectification side.

#### (10) Control block (CTL)

Setting the CTL terminal (pin 21) "L" level places in the standby mode.

#### CTL function table

| CTL | Power         | OUTD |

|-----|---------------|------|

| L   | OFF (Standby) | Hi-Z |

| Н   | ON (Active)   | L    |

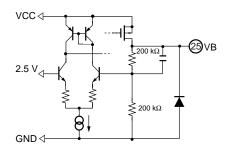

#### (11) Bias voltage block (VB)

Bias voltage block outputs 5 V (Typ) for the power supply of the output circuit and for setting the bootstrap voltage.

#### (12) Off time control block (Off time Control)

When MB39A119 operates by high on-duty, voltage difference of both ends of boot strap capacitor  $C_B$  is decreasing gradually. In such the case, off time control block charges with  $C_B$  by compulsorily generating off time (0.3  $\mu$ s Typ).

#### (13) Overcurrent detection block (Over Current Det.)

Overcurrent detection block detects the 0.2 V (Typ) or more potential difference between +INC2 terminal (pin 10) and -INC2 terminal (pin 11). When excessive current flows to the charge direction due to load-sudden change, it determines the overcurrent, makes CS terminal (pin 17) "L" level, and makes the on duty 0 %. After finishing the overcurrent, MB39A119 restarts with the soft-start operation.

#### (14) Synchronous rectification control block (Synchronous Cnt.)

CS terminal (pin 17) and 2.6 V (Typ) are compared. Output OUT-2 terminal (pin 24) for synchronous rectification side FET drive in the soft-start is fixed at "L" level.

Output OUTC2 terminal of current detection amplifier block (Current Amp2) (pin 9) and 0.3 V (Typ) are compared, and output OUT-2 terminal (pin 24) for synchronous rectification side FET drive is fixed at "L" level at light-load.

#### 2. Protection Function

#### (1) Under voltage lockout protection circuit block (VREF-UVLO)

A momentary decrease in internal reference voltage (VREF) may cause malfunctions in the control IC, resulting in breakdown or degradation of the system.

To prevent such malfunction, the under voltage lockout protection circuit detects internal reference voltage drop and fixes the OUT-1 terminal (pin 27) and the OUT-2 terminal (pin 24) to the "L" level. The system restores voltage supply when the internal reference voltage reaches the threshold voltage of the under voltage lockout protection circuit.

#### Protection circuit (VREF-UVLO) operation function table

When UVLO is operating (VREF voltage is lower than UVLO threshold voltage), the logic of the following terminal is fixed.

| OUTD | OUT-1 | OUT-2 | CS | VB |

|------|-------|-------|----|----|

| Hi-Z | L     | L     | L  | L  |

#### (2) Under voltage lockout protection circuit block (VCC-UVLO, VB-UVLO)

The transient state or a momentary decrease in power supply voltage, which occurs when the bias voltage (VB) for output circuit is turned on, may cause malfunctions in the control IC, resulting in breakdown or degradation of the system.

To prevent such malfunction, the under voltage lockout protection circuit detects a bias voltage drop and fixes the OUT-1 terminal (pin 27) and the OUT-2 terminal (pin 24) to the "L" level. The system restores voltage supply when the power supply voltage or internal reference voltage reaches the threshold voltage of the under voltage lockout protection circuit.

#### Protection circuit (VCC-UVLO, VB-UVLO) operation function table

When UVLO is operating (VCC voltage or VB voltage is lower than UVLO threshold voltage), the logic of the following terminal is fixed.

| OUT-1 | OUT-2 | CS |

|-------|-------|----|

| L     | L     | L  |

#### (3) Under input voltage detection comparator block (UV Comp.)

VCC terminal (pin 1) voltage and -INC2 terminal (pin 11) voltage are compared, and VCC voltage is lower than the battery voltage +0.1 V (Typ) and fixes the OUT-1 terminal (pin 27) and OUT-2 terminal (pin 24) to the "L" level.

The system restores voltage supply when the input voltage reaches the threshold voltage of the under input voltage detection comparator.

#### Protection circuit (UV Comp.) operation function table

When under input voltage is detected (Input voltage is lower than UV Comp. threshold voltage), the logic of the following terminal is fixed.

| OUT-1 | OUT-2 | CS |  |

|-------|-------|----|--|

| L     | L     | L  |  |

#### 3. Detection Functions

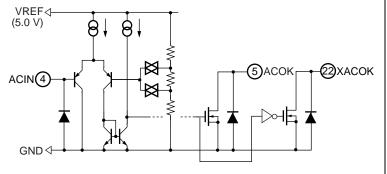

#### (1) AC adapter voltage detection block (AC Comp.)

When ACIN terminal (pin 4) voltage is lower than 2.0 V (Typ), AC adapter voltage detection block (AC Comp.) outputs "Hi-Z" level to the ACOK terminal (pin 5) and outputs "L" level to the XACOK terminal (pin 22). When CTL terminal (pin 21) is set to "L" level, ACOK terminal (pin 5) and XACOK terminal (pin 22) are fixed to "Hi-Z" level.

#### AC adapter detection function table

The logic of the following terminal is fixed according to the connection state of the AC adapter.

| ACIN | ACOK | XACOK |

|------|------|-------|

| Н    | L    | Hi-Z  |

| L    | Hi-Z | L     |

#### (2) Constant voltage control state detection block (CV Comp.)

When CV Comp. detects that the FB123 terminal (pin 14) voltage of the error amplifier (Error Amp3) output terminal becomes 2.6 V (Typ) or less, "L" level is output to constant voltage control state detection block output terminal CVM terminal (pin 6).

#### Charge control state function table

| Error Amp3 output (FB123) | CVM  | Status                   |

|---------------------------|------|--------------------------|

| > 2.6 V                   | Hi-Z | Constant current control |

| ≤ 2.6 V                   | L    | Constant voltage control |

#### ■ CONSTANT CHARGING VOLTAGE AND CURRENT OPERATION

The MB39A119 is DC/DC converter IC with the pulse width modulation method (PWM method) .

In the output voltage control loop, the output voltage of the DC/DC converter is detected, and the Error Amp3 compares internal reference voltage 4.2 V and DC/DC converter output to output the PWM controlled signal.

In the charging current control loop, the voltage drop generated at both ends of charging current sense resistor (Rs<sub>1</sub>) is sensed by +INC2 terminal (pin 10) , -INC2 terminal (pin 11) of Current Amp2, and the signal is output to OUTC2 terminal (pin 9) , which is amplified by 24.5 times. Error Amp2 compares the OUTC2 terminal (pin 9) voltage, which is the output of Current Amp2, and +INE2 terminal (pin 12) to output the PWM control signal, and it regulates the charging current.

In AC adapter current control loop, the voltage drop generated at both ends of AC adapter current sense resistor (Rs2) is sensed by +INC1 terminal (pin 3), -INC1 terminal (pin 2) of Current Amp1, and the signal is output to -INE1 terminal (pin 8), which is amplified by 25 times. Error Amp1 compares -INE1 terminal (pin 8) voltage, which is output of Current Amp1, and +INE1 terminal (pin 7) to output PWM controlled signal, and it limits the charging current due to the AC adapter current not to exceed the setting value.

The PWM comparator compares the triangular wave to the smallest terminal voltage among the Error Amplifier output voltage (Error Amp1 to Error Amp3). And the triangular wave voltage generated by the triangular wave oscillator. When the triangular wave voltage is smaller than the error amplifier output voltage, the main side output transistor is turned on and the synchronous rectification side output transistor is turned off.

#### **■ SETTING THE CHARGE VOLTAGE**

The charge voltage (DC/DC output voltage) can be set by connecting external output voltage setting resistors (R1 and R2) to the -INE3 terminal (pin 15) . Be sure to select a resistor value that allows you to ignore the onresistance (35  $\Omega$  at 1 mA) of internal FET connected to the OUTD terminal (pin 16).

Battery charge voltage: Vo

$$V_0 (V) = \frac{R1 + R2}{R2} \times -INE3 (V)$$

#### **■ SETTING THE CHARGE CURRENT**

The charge current value can be set at the analog voltage value of the +INE2 terminal (pin 12).

Charge current formula : Ichg (A) =

$$\frac{+ INE2 (V)}{24.5 \times R_{S1} (\Omega)}$$

Battery charge current setting voltage: + INE2

+ INE2 (V) =

$$24.5 \times Ichg (A) \times Rs1 (\Omega)$$

It is recommended that the filter should be connected to an input terminal of Current Amp2 as shown below in order to reduce the switching noise and increase the charge current accuracy.

#### **■ SETTING THE INPUT CURRENT**

The input limit current value can be set at the analog voltage value of the +INE1 terminal (pin 7).

Input current formula :

$$I_{IN}(A) = \frac{+ INE1(V)}{25 \times R_{S2}(\Omega)}$$

Input current setting voltage : + INE1 + INE1 (V) =

$$25 \times I_{IN}$$

(A)  $\times R_{S2}$  ( $\Omega$ )

#### ■ SETTING THE OVERCURRENT DETECTION VALUE

The overcurrent is detected when the voltage difference is more than 0.2 V (Typ) between +INE2 terminal (pin 10) voltage and -INE2 terminal (pin 11) voltage.

Charge overcurrent detection value : locdet (A) =

$$\frac{0.2 \text{ (V)}}{\text{Rs}_1 (\Omega)}$$

Charge current and overcurrent detection value by Rs1 value (example)

| Rs <sub>1</sub>     | +INE2          | lchg           | OCDet |

|---------------------|----------------|----------------|-------|

| $33~\text{m}\Omega$ | 0.5 V to 3.5 V | 0.6 A to 4.2 A | 6 A   |

| 15 m $\Omega$       | 0.5 V to 3.5 V | 1.3 A to 9.3 A | 13 A  |

#### ■ SETTING THE TRIANGULAR WAVE OSCILLATION FREQUENCY

The triangular wave oscillation frequency can be set by the timing resistor ( $R_T$ ) connected to the RT terminal (pin 18) .

Triangular wave oscillation frequency: fosc

fosc (kHz)

$$\Rightarrow$$

19500

$R_T (k\Omega)$

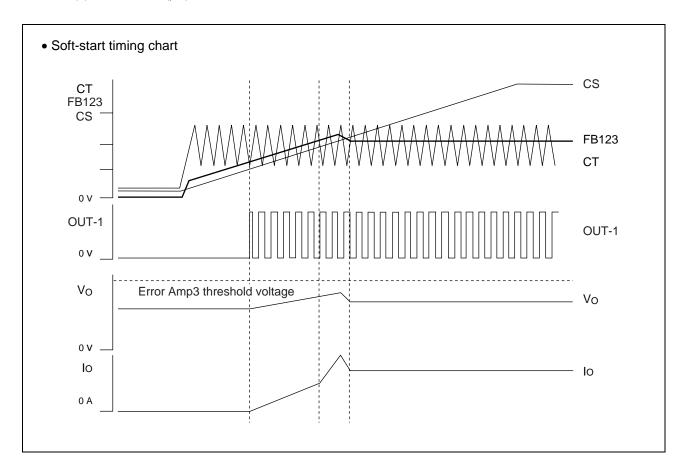

#### ■ SETTING THE SOFT-START TIME

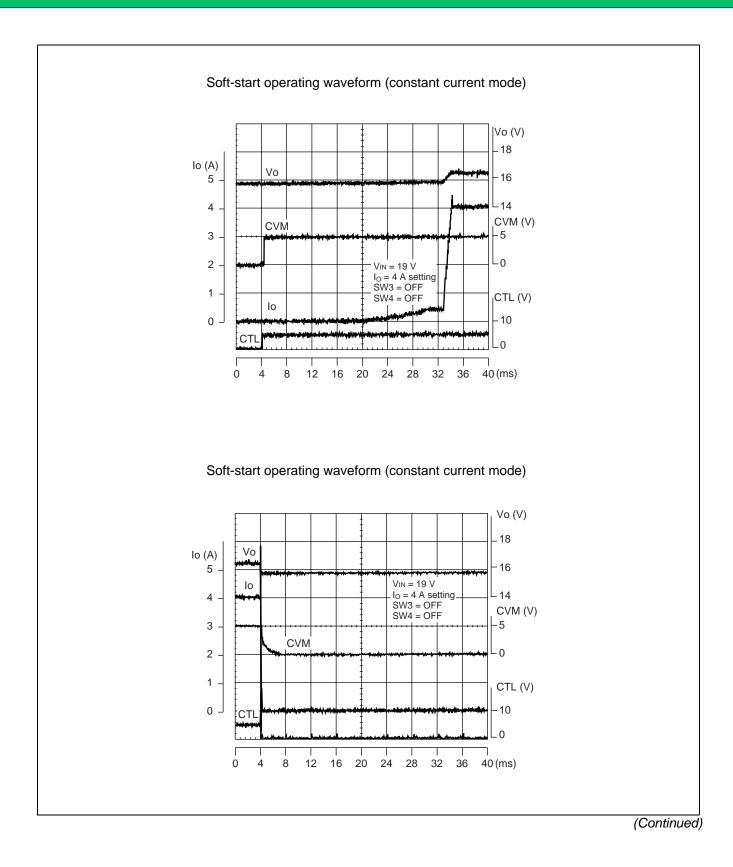

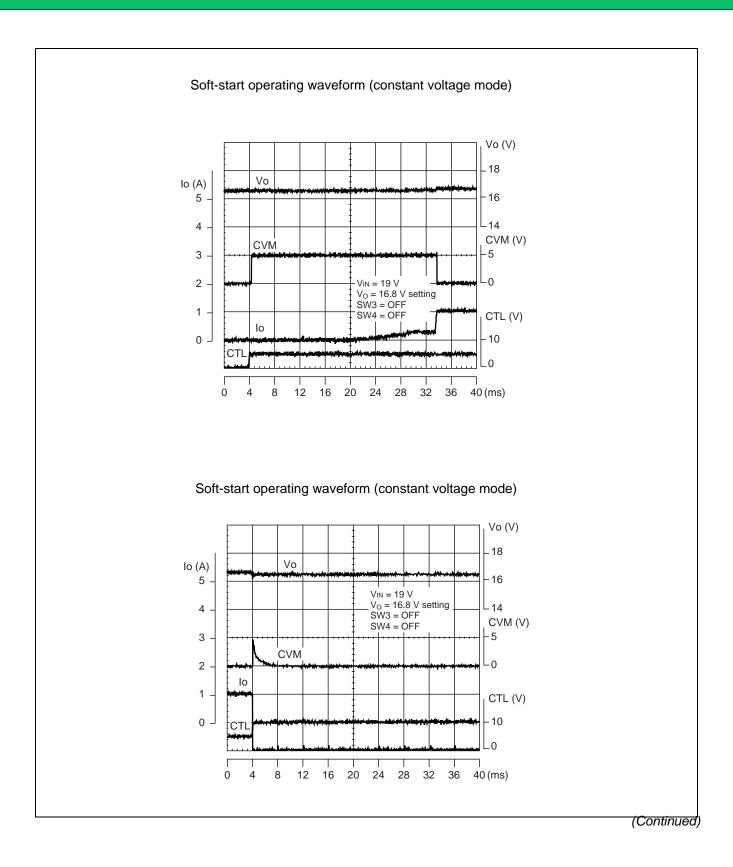

To prevent rush current at start-up of IC, the soft-start time can be set by connecting soft-start capacitor (Cs) to the CS terminal (pin 17).

When the CTL terminal (pin 21) is set to "H" level and IC is started ( $Vcc \ge UVLO$  threshold voltage), external soft-start capacitor (Cs) connected to the CS terminal (pin 17) is charged at 10  $\mu$ A.

ON duty depends PWN comparator output, which compares the FB123 terminal (pin 14) voltage and the triangular wave oscillator output voltage.

During soft-start, FB123 terminal (pin14) voltage increases with sum voltage of CS terminal (pin 17) and diode voltage. Therefore, the output voltage of the DC/DC converter and current increase can be set by output ON duty in proportion to rise of the CS terminal (pin 17) voltage. The ON duty is affected by the ramp voltage of FB123 terminal (pin 14) until an output voltage of one Error Amp reaches the DC/DC converter loop controlled voltage.

Soft-start time is obtained from the following formula. :

Soft-start time: ts (time to output on duty 80 %)

ts (s)

$$\neq$$

0.13  $\times$  Cs ( $\mu$ F)

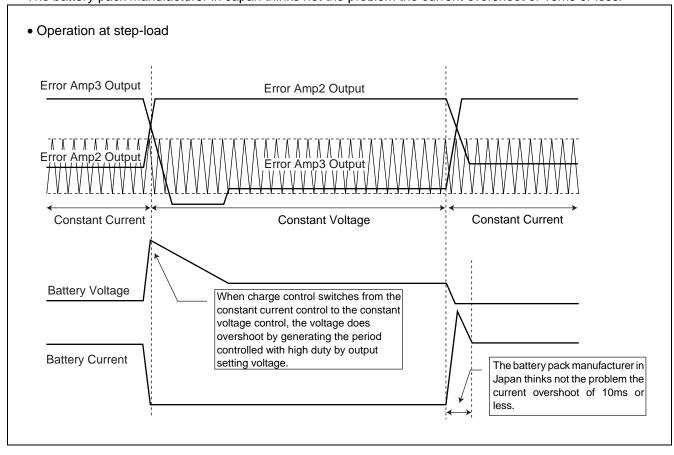

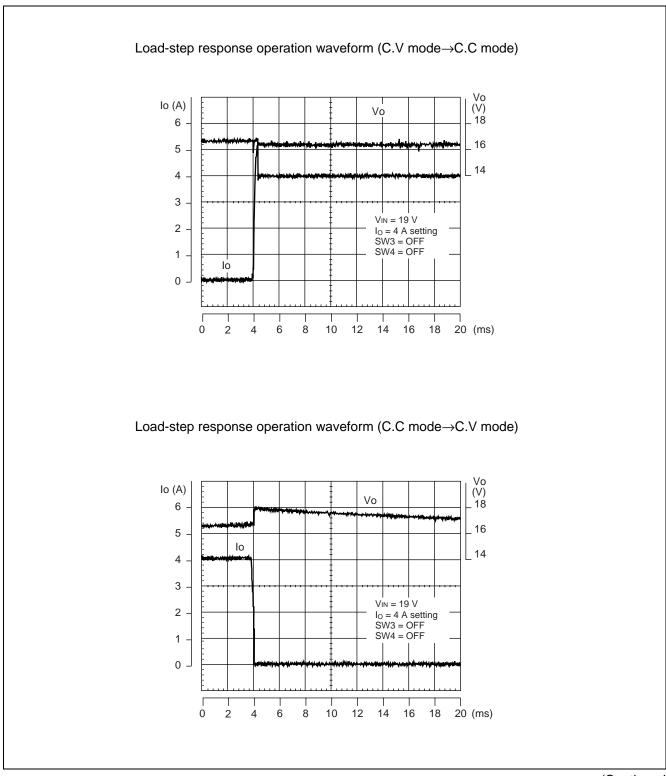

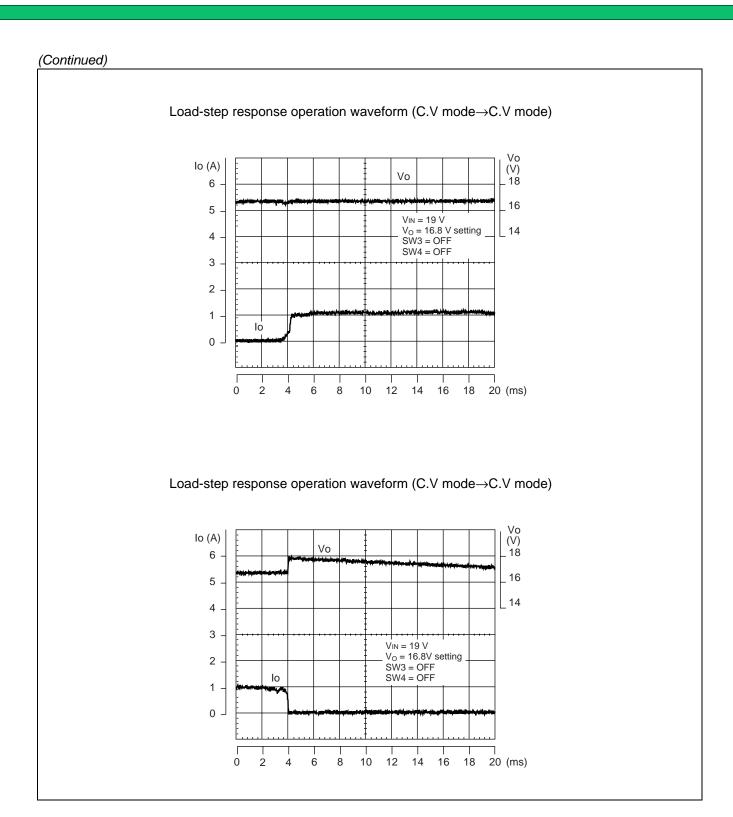

#### **■ TRANSIENT RESPONSE AT LOAD-STEP**

The constant voltage control loop and the constant current control loop are independent. With the load-step, these two control loops change.

The battery voltage and current overshoot are generated by the delay time of the control loop when the mode changes. The delay time is determined by phase compensation constant. When the battery is removed if the charge control is switched from the constant current control to the constant voltage control, and the charging voltage does overshoot by generating the period controlled with high duty by output setting voltage. The excessive voltage is not applied to the battery because the battery is not connected.

When the battery is connected if the charge control is switched from the constant voltage control to the constant current control, and the charging current does overshoot by generating the period controlled with high duty by output setting voltage.

The battery pack manufacturer in Japan thinks not the problem the current overshoot of 10ms or less.

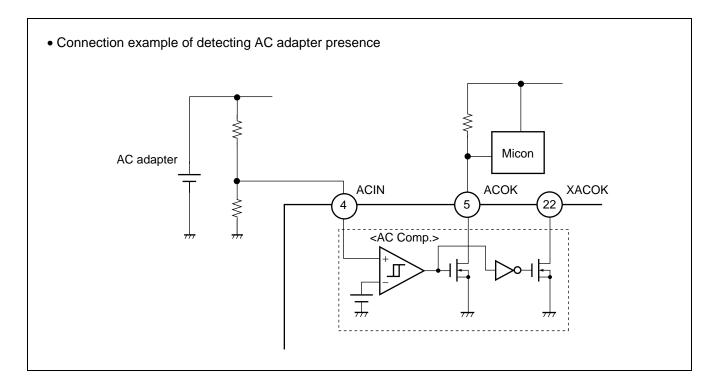

#### ■ AC ADAPTER DETECTION FUNCTION

When ACIN terminal (pin 4) voltage is lower than 2.0 V (Typ), AC adapter voltage detection block (AC Comp.) outputs "Hi-Z" level to the ACOK terminal (pin 5) and outputs "L" level to the XACOK terminal (pin 22). When CTL terminal (pin 21) is set to "L" level, ACOK terminal (pin 5) and XACOK terminal (pin 22) are fixed to "Hi-Z" level.

#### (1) AC adapter presence

The presence of AC adapter can be easily detected because the signal is output from the ACOK terminal (pin 5) to microcomputer etc.

In this case, if CTL terminal (pin 21) is set in "L" level, IC become the standby state ( $Icc = 0 \mu A Typ$ ).

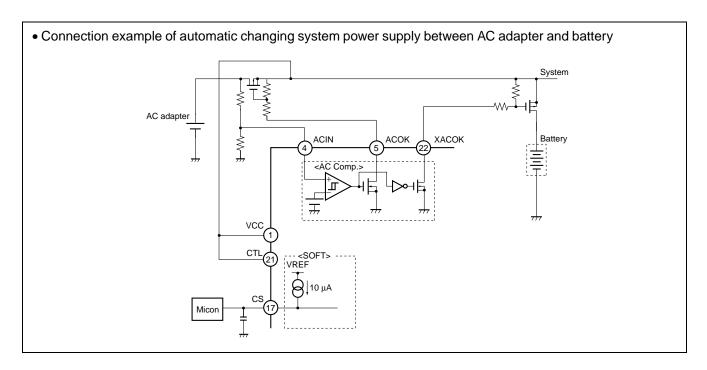

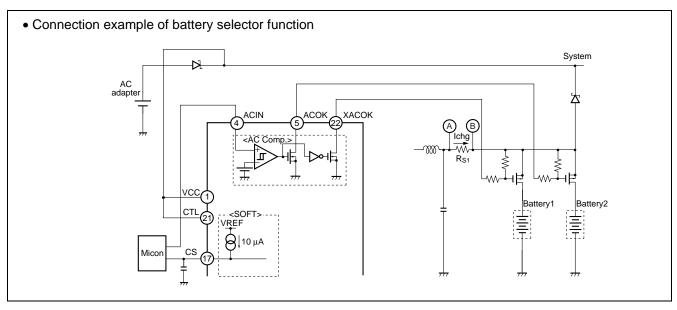

#### (2) Automatic changing system power supply between AC adapter and battery

The AC adapter voltage is detected, and the external switch at input side and battery side is changed automatically with the connection as follows. Connect CTL terminal (pin 21) to VCC terminal (pin 1) for this function. OFF duty cycle becomes 100 % when CS terminal (pin 17) voltage is made to be 0 V, if it is needed after full charge.

#### (3) Battery selector function

When control signal from microcomputer etc. is input to ACIN terminal (pin 4) below, ACOK terminal (pin 5) output voltage and XACOK terminal (pin 22) output voltage are controlled to select one of the two batteries for charge. Connect CTL terminal (pin 21) to VCC terminal (pin 1) for this function. OFF duty cycle becomes 100 % when CS terminal (pin 17) voltage is made to be 0 V, if it is needed after full charge.

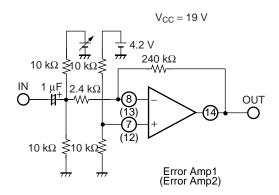

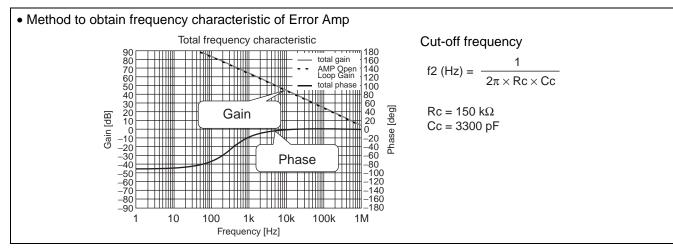

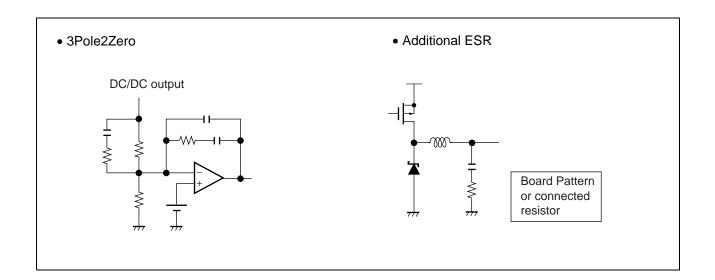

#### **■ PHASE COMPENSATION**

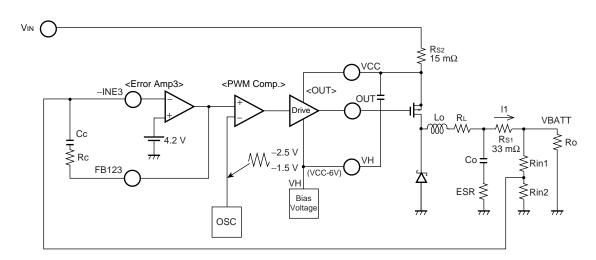

Circuit example of phase compensation is shown below.

• Circuit example of phase compensation

Lo: Inductance

R<sub>L</sub>: Equivalent series resistance of inductance

Co: Capacity of condenser

ESR: Equivalent series resistance of condenser

Ro: Load resistance

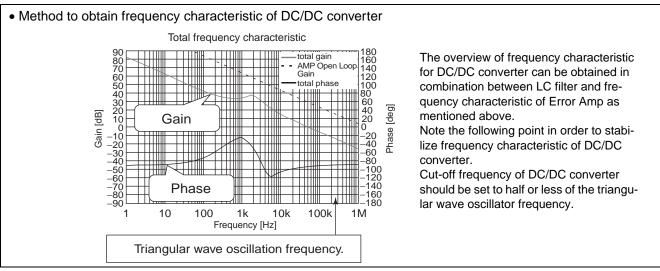

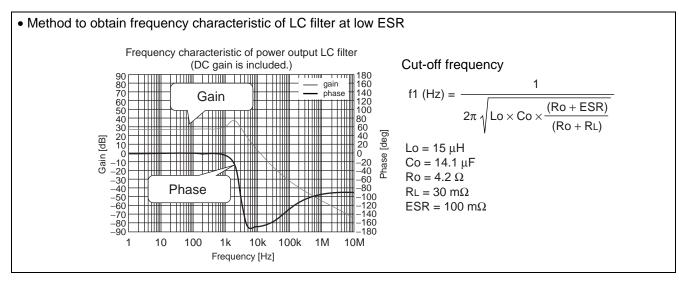

Method to obtain frequency characteristic of LC filter

Cut-off frequency

f1 (Hz) =

$$\frac{1}{2\pi \sqrt{\text{Lo} \times \text{Co} \times \frac{(\text{Ro} + \text{ESR})}{(\text{Ro} + \text{RL})}}}$$

$$Lo = 15 \mu H$$

$$Co = 14.1 \mu F$$

$$Ro = 4.2 \Omega$$

$$RL = 30 m\Omega$$

$$ESR = 100 m\Omega$$

- Note1) Review frequency characteristic of Error Amp when LC filter constant is changed.

- Note2) When the ceramic capacitor is used as smoothing capacitor Co, phase margin is reduced because ESR of the ceramic capacitor is extremely small as frequency characteristic of LC filter at low ESR.

Therefore, change phase compensation of Error Amp or create resistance equivalent to ESR using pattern.

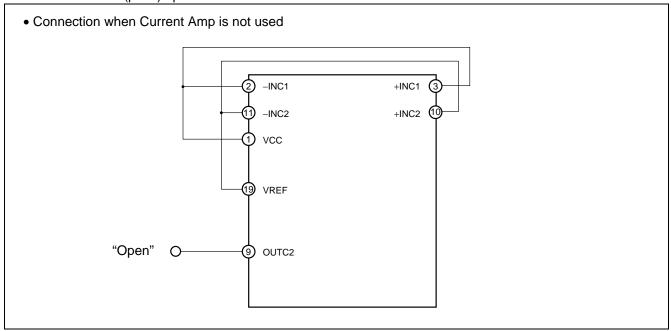

#### ■ PROCESSING WITHOUT USING OF THE CURRENT AMP1 AND AMP2

When Current Amp is not used, connect +INC1 terminal (pin 3) and -INC1 terminal (pin 2) to VCC terminal (pin 1), connect +INC2 terminal (pin 10) and -INC2 terminal (pin 11) to VREF terminal (pin 19), and then leave OUTC2 terminal (pin 9) open.

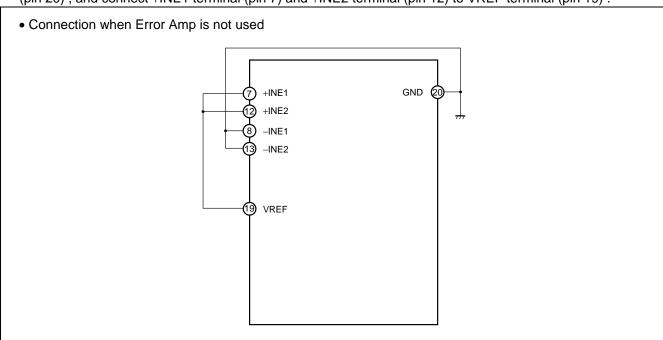

#### ■ PROCESSING WITHOUT USING OF THE ERROR AMP1 AND AMP2

When Error Amp1 and Amp2 are not used, connect –INE1 terminal (pin 8) and –INE2 terminal (pin 13) to GND (pin 20), and connect +INE1 terminal (pin 7) and +INE2 terminal (pin 12) to VREF terminal (pin 19).

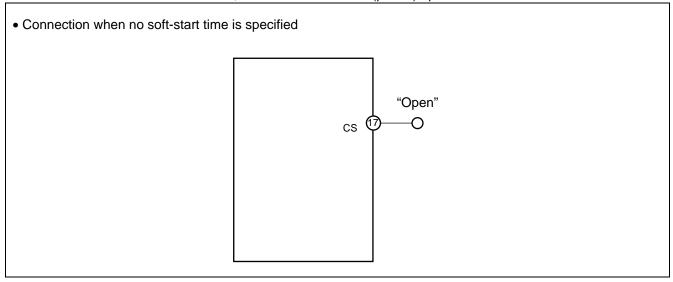

### ■ PROCESSING WITHOUT USING OF THE CS TERMINAL

When soft-start function is not used, leave the CS terminal (pin 17) open.

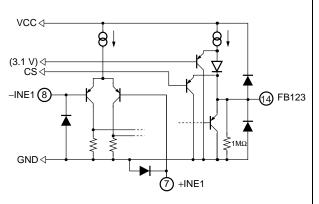

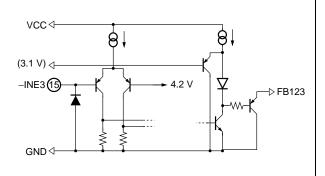

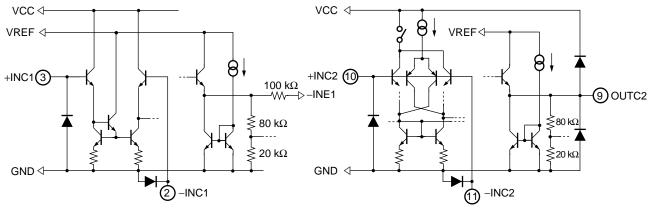

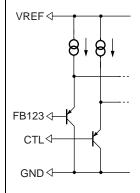

#### **■ I/O EQUIVALENT CIRCUIT**

• Reference voltage block

• Bias voltage block

• Triangular wave oscillator block

• Error amplifier block (Error Amp2)

• Control block

Soft-start block

• Error amplifier block (Error Amp1)

• Error amplifier block (Error Amp3)

# (Continued) VCC <-VREF <-

• Current detection amplifier block (Current Amp1)

• Current detection amplifier block (Current Amp2)

- PWM comparator block

- (Main side) **28** CB

Output block

- Output block (synchronous rectification side)

- Invalidity current prevention block

- Constant voltage control state detection block

- AC adapter voltage detection block

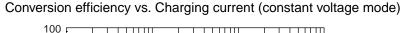

#### **■ APPLICATION EXAMPLE**

### ■ PARTS LIST

| Component       | Item              | Specification                    | Vendor  | Package | Parts No.     |

|-----------------|-------------------|----------------------------------|---------|---------|---------------|

| M1              | IC                | MB39A119                         | Fujitsu | QFN-28P | MB39A119QN-G  |

| Q1-1, Q1-2      | N-ch FET          | VDS = -30  V, ID = 8  A (Max)    | NEC     | SO-8    | μΡΑ2752       |

| Q2-1, Q2-2      | P-ch FET          | VDS = -30  V, ID = 8  A (Max)    | NEC     | SO-8    | μΡΑ1772       |

| Q5              | P-ch FET          | VDS = -30  V, ID = 6  A (Max)    | TOSHIBA | SO-8    | TPC8102       |

| D1              | Diode             | VF = 0.35 V (Max) at IF = 0.5 A  | ROHM    | TUMD2   | RSX051VA-30   |

| D4              | Diode             | VF = 0.4 V (Max) at $IF = 0.3 A$ | SANYO   | 1197A   | SBS006        |

| L1              | Inductor          | 5.2 μH, 22 mΩ, 5.5 A             | SUMIDA  | SMD     | CDRH104R-5R2  |

| C1              | Ceramic condenser | 4.7 μF (25 V)                    | TDK     | 3216    | C3216JB1E475K |

| C2              | Ceramic condenser | 4.7 μF (25 V)                    | TDK     | 3216    | C3216JB1E475K |

| C3              | Ceramic condenser | 4.7 μF (25 V)                    | TDK     | 3216    | C3216JB1E475K |

| C4              | Ceramic condenser | 4.7 μF (25 V)                    | TDK     | 3216    | C3216JB1E475K |

| C5              | Ceramic condenser | 4.7 μF (25 V)                    | TDK     | 3216    | C3216JB1E475K |

| C6              | Ceramic condenser | 0.1 μF (50 V)                    | TDK     | 1608    | C1608JB1H104K |

| C7              | Ceramic condenser | 1.0 μF (25 V)                    | TDK     | 3216    | C3216JB1E105K |

| C8              | Ceramic condenser | 0.1 μF (50 V)                    | TDK     | 1608    | C1608JB1H104K |

| C9              | Ceramic condenser | 0.22 μF (25 V)                   | TDK     | 1608    | C1608JB1E224K |

| C10             | Ceramic condenser | 0.1 μF (50 V)                    | TDK     | 1608    | C1608JB1H104K |

| C11             | Ceramic condenser | 6800 pF (50 V)                   | TDK     | 1608    | C1608JB1H682K |

| C12             | Ceramic condenser | 330 pF (50 V)                    | TDK     | 1608    | C1608CH1H331J |

| C13             | Ceramic condenser | 22 pF (50 V)                     | TDK     | 1608    | C1608CH1H220J |

| C14             | Ceramic condenser | 22 pF (50 V)                     | TDK     | 1608    | C1608CH1H220J |

| C18             | Ceramic condenser | 1500 pF (50 V)                   | TDK     | 1608    | C1608CH1H152J |

| C21             | Ceramic condenser | 0.1 μF (50 V)                    | TDK     | 1608    | C1608JB1H104K |

| C22             | Ceramic condenser | 0.22 μF (25 V)                   | TDK     | 1608    | C1608JB1E224K |

| C23             | Ceramic condenser | 0.22 μF (25 V)                   | TDK     | 1608    | C1608JB1E224K |

| Rs <sub>1</sub> | Resistor          | 33 mΩ                            | KOA     | SL1     | SL1TTE33L0D   |

| Rs <sub>2</sub> | Resistor          | 15 m $\Omega$                    | KOA     | SL1     | SL1TTE15L0D   |

| R2              | Resistor          | 15 Ω                             | ssm     | 1608    | RR0816P150D   |

| R6              | Resistor          | 51 kΩ                            | ssm     | 1608    | RR0816P513D   |

| R8              | Resistor          | 300 kΩ                           | ssm     | 1608    | RR0816P304D   |

| R10             | Resistor          | 100 kΩ                           | ssm     | 1608    | RR0816P104D   |

| R15             | Resistor          | 24 kΩ                            | ssm     | 1608    | RR0816P243D   |

| R17             | Resistor          | 10 kΩ                            | ssm     | 1608    | RR0816P103D   |

| R18             | Resistor          | 33 kΩ                            | ssm     | 1608    | RR0816P333D   |

| R19             | Resistor          | 39 kΩ                            | ssm     | 1608    | RR0816P393D   |

| R20             | Resistor          | 20 kΩ                            | ssm     | 1608    | RR0816P203D   |

| R21             | Resistor          | 24 kΩ                            | ssm     | 1608    | RR0816P243D   |

| R24             | Resistor          | 47 kΩ                            | ssm     | 1608    | RR0816P473D   |

| R25             | Resistor          | 9.1 kΩ                           | ssm     | 1608    | RR0816P912D   |

| R26             | Resistor          | 15 kΩ                            | ssm     | 1608    | RR0816P153D   |

| R27             | Resistor          | 16 kΩ                            | ssm     | 1608    | RR0816P163D   |

### (Continued)

| Component | Item     | Specification | Vendor | Package | Parts No.   |

|-----------|----------|---------------|--------|---------|-------------|

| R28       | Resistor | 2 kΩ          | ssm    | 1608    | RR0816P202D |

| R32       | Resistor | 100 kΩ        | ssm    | 1608    | RR0816P104D |

| R33       | Resistor | 10 kΩ         | ssm    | 1608    | RR0816P103D |

| R34       | Resistor | 100 kΩ        | ssm    | 1608    | RR0816P104D |

| R39       | Resistor | 16 kΩ         | ssm    | 1608    | RR0816P163D |

| R40       | Resistor | 75 kΩ         | ssm    | 1608    | RR0816P753D |

| R41       | Resistor | 16 kΩ         | ssm    | 1608    | RR0816P163D |

| R45       | Resistor | 100 kΩ        | ssm    | 1608    | RR0816P104D |

| R46       | Resistor | 56 kΩ         | ssm    | 1608    | RR0816P563D |

| R51       | Resistor | 10 Ω          | ssm    | 1608    | RR0816P100D |

| R52       | Resistor | 10 Ω          | ssm    | 1608    | RR0816P100D |

Note: NEC : NEC corporation

TOSHIBA: TOSHIBA CORPORATION

ROHM: ROHM CO., LTD.

SUMIDA: Sumida Corporation

TDK: TDK Corporation

KOA: KOA Corporation

ssm: SUSUMU CO., LTD.

SANYO: SANYO Electric Co., Ltd.

#### ■ SELECTION OF COMPONENTS

#### N-ch MOS FET

The N-ch MOS FET for switching use should be rated for at least +20% more than the input voltage. To minimize continuity loss, use a FET with low  $R_{\text{DS (ON)}}$  between the drain and source. For high input voltage and high frequency operation, on-cycle switching loss will be higher so that power dissipation must be considered. In this application, the NEC  $\mu\text{PA2752}$  is used. Continuity loss, on/off switching loss and total loss are determined by the following formulas. The selection must ensure that peak drain current does not exceed rated values.

Continuity loss: Pc

$$P_C = I_{D2} \times R_{DS}$$

(on)  $\times Duty$

On-cycle switching loss: Ps (on)

$$Ps(on) = \frac{V_D(Max) \times I_D \times tr \times fosc}{6}$$

Off-cycle switching loss: Ps (OFF)

$$Ps (OFF) = \frac{V_D (Max) \times I_D (Max) \times tf \times fosc}{6}$$

Total loss : P<sub>T</sub>

$$P_T = P_C + P_S (ON) + P_S (OFF)$$

#### Inductor

In selecting inductors, it is of course essential not to apply more current than the rated capacity of the inductor, but also to note that the lower limit for ripple current is a critical point that if reached will cause discontinuous operation and a considerable drop in efficiency. This can be prevented by choosing a higher inductance value, which will enable continuous operation under light loads. Note that if the inductance value is too high, however, direct current resistance (DCR) is increased and this will also reduce efficiency. The inductance must be set at the point where efficiency is greatest.

Note also that the DC superimposition characteristics become worse as the load current value approaches the rated current value of the inductor, so that the inductance value is reduced and ripple current increases, causing loss of efficiency. The selection of rated current value and inductance value will vary depending on where the point of peak efficiency lies with respect to load current. Inductance values are determined by the following formulas.

The L value for all load current conditions is set so that the peak to peak value of the ripple current is 1/2 the load current or less.

#### 16.8 V output

$V_{IN} = 24 \text{ V (Max)}$ ,  $V_0 = 16.8 \text{ V}$ ,  $I_0 = 4.0 \text{ A}$ , fosc = 500 kHz

## 1. N-ch MOS FET (μPA2752 : NEC product)

Main side

$$V_{DS}=30~V,~V_{GS}=~\pm~20~V,~I_{D}=8~A,~R_{DS}~(o_{N})~=25~m\Omega~(Typ)~,~Qg=10~nC~(Typ)$$

Synchronous rectification side

$$V_{DS} = 30 \text{ V}, V_{GS} = \pm 20 \text{ V}, I_{D} = 8 \text{ A}, R_{DS} \text{ (on)} = 25 \text{ m}\Omega \text{ (Typ)}, Qg = 10 \text{ nC (Typ)}$$

Drain current: Peak value

The peak drain current of this FET must be within its rated current. If the FET's peak drain current is I<sub>D</sub>, it is obtained by the following formula.

Main side

$$I_D \ge I_O + \frac{V_{IN} - V_O}{2L} t_{ON}$$

$$\ge 4.0 + \frac{24 - 16.8}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^3} \times 0.7$$

$$\ge 4.97 A$$

Synchronous rectification side

$$I_D \ge I_O + \frac{V_O}{2L} t_{OFF}$$

$$\ge 4.0 + \frac{16.8}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^3} \times (1 - 0.7)$$

$$\ge 4.97 A$$

### 2. Inductor (CDRH104R-5R2: SUMIDA product)

$5.2 \,\mu\text{H}$  (tolerance  $\pm \,30\%$ ) , rated current =  $5.5 \,\text{A}$

$$L \ge \frac{2 (V_{IN} - V_{O})}{I_{O}} t_{ON}$$

$$\ge \frac{2 \times (24 - 16.8)}{4.0} \times \frac{1}{500 \times 10^{3}} \times 0.7$$

$$\ge \frac{5.04 \, \mu H}{100} + \frac{1}{100} \times \frac{1}$$

The load current satisfying the continuous current condition

Io

$$\geq \frac{\text{Vo}}{2\text{L}}$$

toff

$\geq \frac{16.8}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^{-3}} \times (1-0.7)$

$\geq 0.97 \text{ A}$

Ripple current : Peak value

The peak ripple current must be within the rated current of the inductor. If the peak ripple current is  $l_L$ , it is obtained by the following formula.

$$I_L \ge I_O \frac{V_{IN}-V_O}{2L}$$

to  $\frac{24-16.8}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^3} \times 0.7$   $\ge 4.97 \text{ A}$

Ripple current : peak-to-peak value

If the peak-to-peak ripple current is  $\Delta I_{\perp}$ , it is obtained by the following formula.

$$\Delta I_{L} = \frac{V_{IN} - V_{O}}{L} \quad to_{N}$$

$$= \frac{24 - 16.8}{5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^{3}} \times 0.7$$

$$\stackrel{?}{=} 1.94 \text{ A}$$

### 12.6 V output

$$V_{IN} = 20 \text{ V (Max)}$$

,  $V_0 = 12.6 \text{ V}$ ,  $I_0 = 4.0 \text{ A}$ ,  $fosc = 500 \text{ kHz}$

## 1. N-ch MOS FET (μPA2752 : NEC product)

Main side

$$V_{DS}=30~V,~V_{GS}=~\pm~20~V,~I_{D}=8~A,~R_{DS}~(o_{N})~=25~m\Omega~(Typ)~,~Qg=10~nC~(Typ)$$

Synchronous rectification side

$$V_{DS}=30~V,~V_{GS}=~\pm~20~V,~I_{D}=8~A,~R_{DS}~(on)~=25~m\Omega~(Typ)~,~Qg=10~nC~(Typ)$$

Drain current: Peak value

The peak drain current of this FET must be within its rated current. If the FET's peak drain current is I<sub>D</sub>, it is obtained by the following formula.

Main side

$$I_{D} \ge I_{O} + \frac{V_{IN} - V_{O}}{2L} t_{ON}$$

$$\ge 4.0 + \frac{20 - 12.6}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^{3}} \times 0.63$$

$$\ge 4.90 \text{ A}$$

Synchronous rectification side

$$I_D \ge I_O + \frac{V_O}{2L} t_{OFF}$$

$$\ge 4.0 + \frac{12.6}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^3} \times (1 - 0.63)$$

$$\ge 4.90 \text{ A}$$

## 2. Inductor (CDRH104R-5R2 : SUMIDA product)

$5.2 \,\mu\text{H}$  (tolerance  $\pm \,30\%$ ), rated current =  $5.5 \,\text{A}$

$$L \ge \frac{2 \text{ (V_{IN}-Vo)}}{\text{Io}} \text{ ton}$$

$$\ge \frac{2 \times (24-12.6)}{4.0} \times \frac{1}{500 \times 10^3} \times 0.63$$

$$\ge \frac{4.67 \,\mu\text{H}}{100} \times \frac{1}{100} \times \frac{1}{1$$

The load current satisfying the continuous current condition

Io

$$\geq \frac{\text{Vo}}{2\text{L}}$$

toff

$\geq \frac{12.6}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^{3}} \times (1-0.63)$

$\geq 897.0 \text{ mA}$

$$I_L \ge I_O \frac{V_{IN}-V_O}{2L} t_{ON}$$

$$\ge 4.0 + \frac{20-12.6}{2 \times 5.2 \times 10^{-6}} \times \frac{1}{500 \times 10^3} \times 0.63$$

$$\ge 4.90 A$$

Ripple current : Peak-to-peak value

If the peak-to-peak ripple current is  $\Delta I_L$ , it is obtained by the following formula.

$$\Delta I_{L} = \frac{V_{IN} - V_{O}}{L} \quad to_{N}$$

$$= \frac{20 - 12.6}{5.2 \times ^{-6}} \times \frac{1}{500 \times 10^{3}} \times \quad 0.63$$

$$\stackrel{\Rightarrow}{=} \quad 1.79 \text{ A}$$

## 3. Diode for bootstrap (SBS006 : SANYO product)

V<sub>R</sub> (DC reverse voltage) = 30 V, Average output current = 500 mA, peak surge current = 10 A

$V_F$  (forward voltage) = 0.35 V, at  $I_F$  = 300 mA

V<sub>R</sub>: value that satisfies input voltage

Efficiency is somewhat rising in low leak Schottky diode by the use but even if the signal diode is used, it is enough. It is recommended to use low  $V_E$  Also, capacitor for bootstrap must be very large than gate capacity of FET at main side. It is recommended to use the capacity of approximately 0.1  $\mu$ F to 1.0  $\mu$ F.

## 4. Charging current setting sense resistor (SL1TTE33L0F: KOA product)

$33~\text{m}\Omega$

When + INE2 terminal (pin 12) voltage is 3.3 V, and the charging current (Io) is 4.0 A, R4 is obtained by the following formula.

$$R4 = \frac{+ INE2}{24.5 \times Io}$$

$$= \frac{3.3}{24.5 \times 4.0}$$

$$\Rightarrow \frac{33.0 \text{ m}\Omega}{24.5 \times 4.0}$$

## 5. Input current setting sense resistor (SL1TTE15L0F: KOA product)

$15~\text{m}\Omega$

When + INE1 terminal (pin 7) voltage is 2.25 V, and the input current is 6.0 A, R1 is obtained by the following formula.

R1 =

$$\frac{+ \text{INE1}}{25 \times \text{I1}}$$

$$= \frac{2.25}{25 \times 6.0}$$

$$= \frac{15.0 \text{ m}\Omega}{}$$

## 6. Switching P-ch FET (μPA1772 : NEC product, TPC8102 : TOSHIBA product)

Q2-1, Q2-2, and Q5 must select an appropriate device according to the input current.

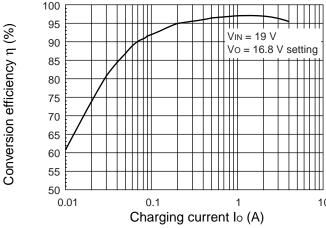

## **■** REFERENCE DATA

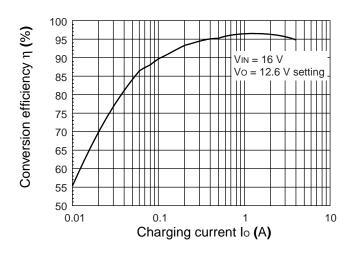

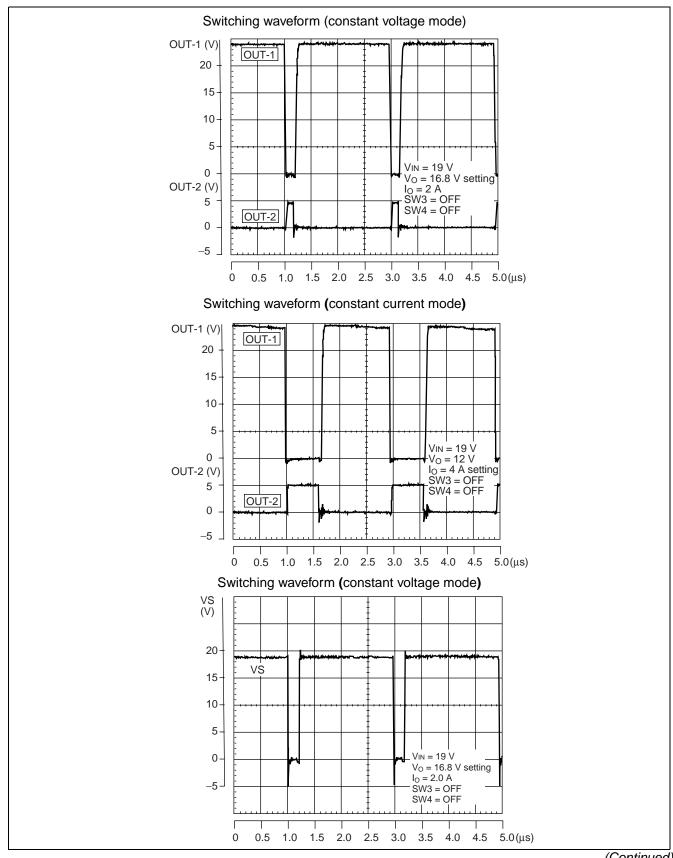

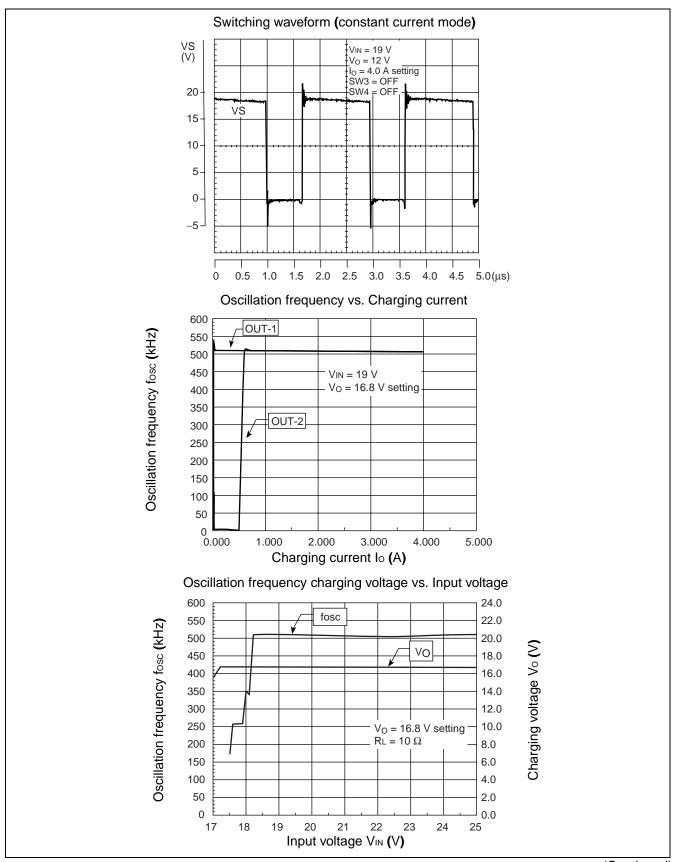

Conversion efficiency vs. Charging current (constant voltage mode)

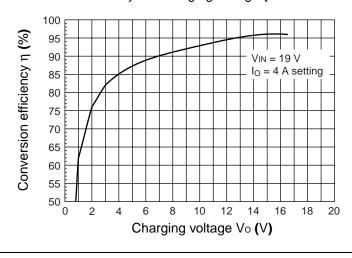

Conversion efficiency vs. Charging voltage (constant current mode)

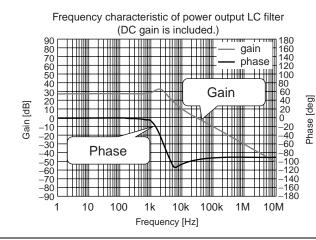

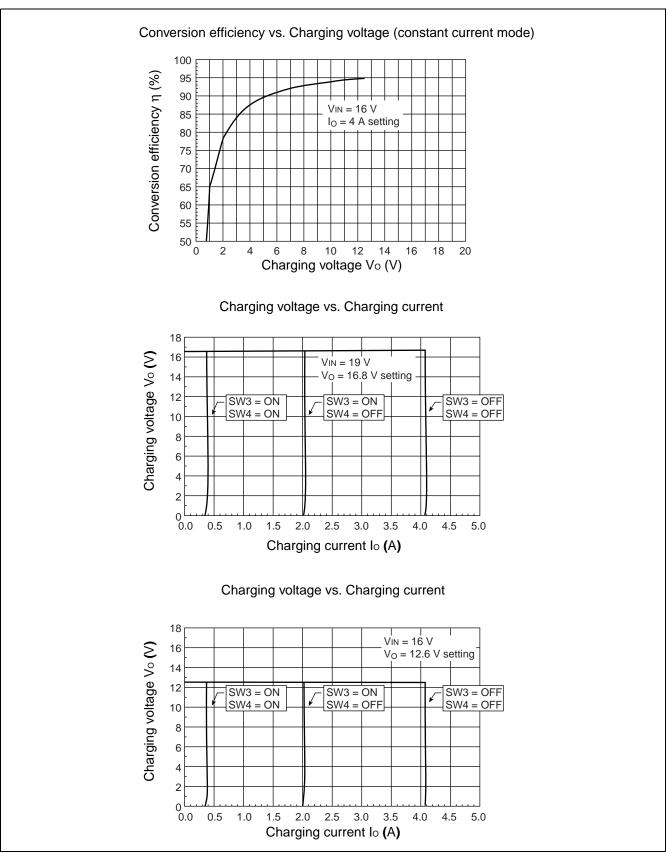

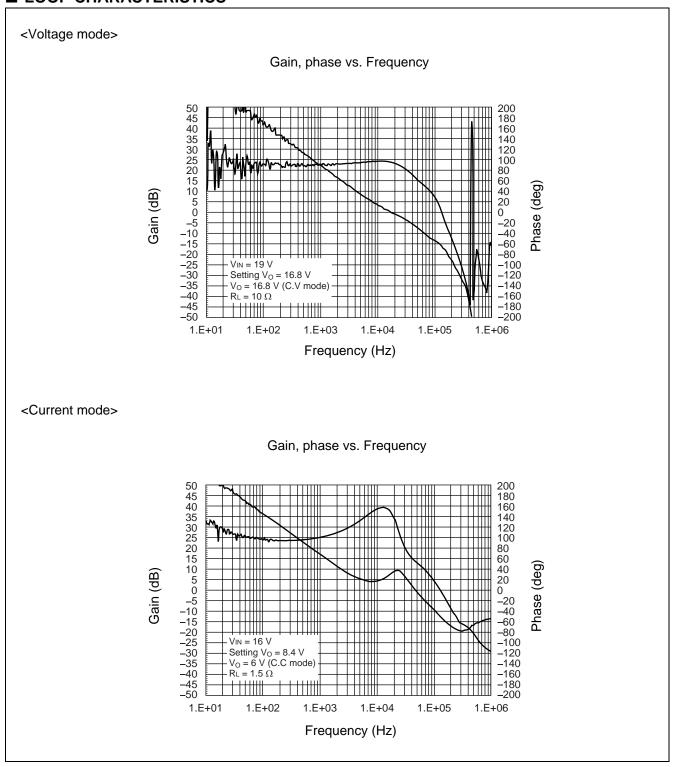

## **■ LOOP CHARACTERISTICS**

#### **■ USAGE PRECAUTIONS**

- Printed circuit board ground lines should be set up with consideration for common impedance.

- Take appropriate static electricity measures.

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  between body and ground.

- Do not apply negative voltages.

- The use of negative voltages below –0.3 V may create parasitic transistors on LSI lines, which can cause abnormal operation.

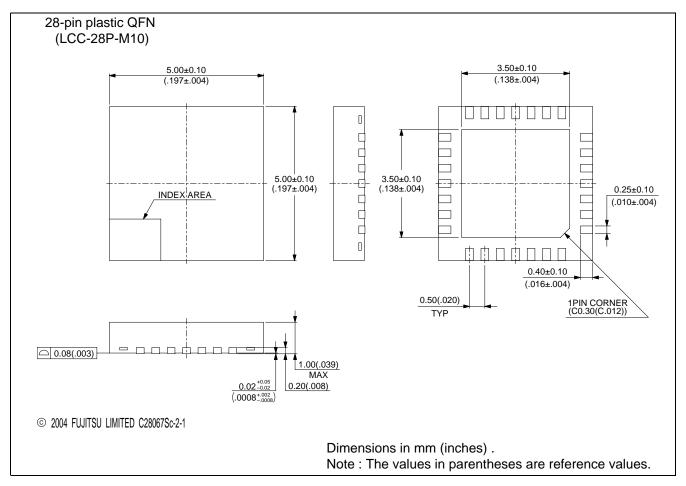

### **■** ORDERING INFORMATION

| Part number | Package                             | Remarks |

|-------------|-------------------------------------|---------|

| MB39A119QN  | 28-pin plastic QFN<br>(LCC-28P-M10) |         |

## **■ PACKAGE DIMENSION**

# **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.